Блок управления преобразователя напряжения в код последовательного приближения

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советскик

Социалистических

Республик (u>873406

К АВТОИЖОМУ СВИ ЕТЕЛЬСТВУ

1 (61) Дополммтельное к авт. санд-ву— р1)м. к.з

Н 03 F. 13/17 (22) Заявлено 03. 12. 79 (21) 284 7783/18-21 с присоединением заявки Нов (23) ПриоритетГосударственный комитет

СССР по делам изобретений н открытий

Опубликовано 15.10.81, Бюллетень Н9 38

Дата опубликования описания 15.10,81 (53) MjPl 681,325 (088.8) (72) Автор изобретен и я

Л.Н.Панков (71) Заявитель

Пензенский политехнический институт (54 ) БЛОК УПРАВЛЕНИЯ ПРЕОБРАЗОВАТЕЛЯ

НАПРЯЖЕНИЯ В КОД ПОСЛЕДОВАТЕЛЬНОГО

ПРИБЛИЖЕНИЯ

Изобретение относится к измеритель. ной и вычислительной технике и может быть использовано, в частности, в преобразователях напряжения в код последовательного приближения.

Известен блок управления преобразователя напряжения в код последовательного приближения, содержащий генератор сигналов, распределитель сигналов и два триггера в каждом разряде, выход генератора сигналов соединен со входом распределителя сигналов, во нсех разрядах входы сброса в "ноль", входы. синхронизации и первые входы установки в "единицу" триггеров сое- 15 динены с выходами распределителя сигналов, соответственно, вторые входы установки в "единицу" первого и нторого триггеров соединены с шинами

"прямого" и "инверсного" выходов бло- 20 ка сравнения, "прямой" выход первого триггера соединен с третьим входом установки в "единицу" второго триггера, "прямой" выход второго триггера соединен с третьим входом установки, 25 в "единицу" первого триггера (13 .

Вследствие раздельного выполнения распределителя сигналов, который обеспечивает также распределение тактон работы устройства, и информацион- 30 ных регистров на триггерах устройство сложно в изготовлении и требует. значительных затрат оборудования.

Известен блок управления преобразователя напряжения в код последовательного приближения, содержащий генератор сигналов, первый выход которого соединен со входом синхронизации первого и нторого триггеров каждого разряда, второй выход — co входом синхронизации третьего триггера .каждого разряда, вход сброса триггеров соединен с шиной сброса, первы вход установки в "единицу" первого и нторого триггеров соеди° 1 нен соответственно с шинами прямого" и "инверсного" сигналов сравнения, второй вход установки в "еди" ницу" — c выходом элемента И данного разряда, первый выход первого и второго триггеров подключен к шинам управления цифро-аналоговым преобразователем, второй выход первого триггера соединен с первым входом установки третьего триггера данного разряда, элементы И всех разрядов соединены последовательно (2) .

В этом устройстве на общих схемных элементах реализуются функции информационных регистров и распреде873406 лителя тактов работы, такое совмещение функций дает уменьшение затрат оборудования по сравнению с затратами оборудования н известных устройствах с выполнением функций информационных регистров и распределителя тактов работы на различных схемных элементах.

Однако устройство сложно в изготовлении, так как в нем применены днухтактные триггера, каждый из которых ныполняется из двух однотактных триггеров. Общее число триггеров в и-разрядном устройстве составляет

4и. Кроме того, в устройстве используетс я и элементов И-НЕ и и элементов Й. Из-за применения большого числа триггеров изготовление устройства сложно и требует значительных затрат оборудования.

Цель изобретения — сокращение аппаратурных затрат.

Цель достигается тем, что в блок управления преобразователя напряжения .в код последовательного приближения, содержащий генератор сигналов, перный выход которого соединен со входом синхронизации первого и второго триггеров каждого разряда, второй выход — со входом синхронизации третьего триггера каждого разряда, вход сброса триггеров соединен с шиной сброса, первый вход установки в "единицу" первого и второго триггеров соединен .соответственно с шинами "прямого" и "инверсного" сигналон сравнения, второй вход установки н "единицу" — с выходом элемента И данного разряда, первый выход первого и второго триггеров подключен к шинам управления цифро-аналоговым преобразователем, второй выход первого триггера соединен с первым входом установки третьего триггера данного разряда, элементы И всех разрядов соединены последовательно, н каждом разряде второй выход второго триггера соединен со вторым входом установки третьего триггера данного разряда, "прямой" выход которого соединен с третьим входом установки н

"единицу" первого и второго триггеров следующего разряда, "инверсный" выход третьего триггера соединен со вторым входом элемента И,данного разряда, "прямой" выход третьего триггера последнего разряда соединен со входом установки в "ноль" первого и второго триггеров всех разрядов.

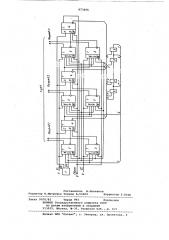

На чертеже представлен блок управления преобразователя напряжения в код последовательного приближения, содержащий генератор сигналов 1, триггеры 2,3 и 4, элементы И 5 в каждом разряде. Триггеры 2 и 3 синхронные RS-триггеры, в качестве триггера 4 применяют синхронный

D-триггер, вход О которого используЬО

65 линается логическая единица, которая разрешает занес-ние результатов сравнения Х1 и Х 1 н триггеры 2 и 3 следующего разряда во втором такте работы устройства. Одновременно сигналом логического ноля с "инверсного" ется для управления установки триггера 4 н состояние "ноль".

Во всех разрядах входы сброса в

"ноль" триггеров 2,3 и 4 соединены со входом 6 устройства. Входы синхронизации триггеров 2,3 и 4 соединены с выходами генератора сигналов 1 соответственно. Первые входы установки. в "единицу" триггеров 2 и 3 соединены с шинами 7 и 8 "прямого" и

"инверсного" сигналов сравнения. Элементы И 5 соединены последовательно.

В каждом разряде вторые входы установки в "единицу" триггеров 2 и 3 соединены с выходами элемента И 5 данного разряда. Выход триггера 2

15 соединен с первым входом .установки триггера 4 данного разряда. В каждом разряде выход триггера 3 соединен со вторым входом установки триггера 4 данного разряда, "прямой" выход кото2О рого соединен с третьими входами установки в "единицу" триггеров 2 и 3 следующего разряда. "Инверсный" выход триггера 4 соединен со входом элемента И 5 данного разряда. "Прямой" выход триггера 4 последнего разряда соединен со входами установки н "ноль" триггеров 2 и 3 всех разрядов.

Устройство работает следующим образом.

По сигналу, поступающему на вход б устройства триггеры 2,3 и 4 всех разрядов сбрасываются н "ноль". Этот сигнал необходим только для принудительного приведения устройства н исI ходное состояние. После каждого цикла преобразования это состояние периодически восстанавливается без дополнительных сигналов на вход б устройства. При этом сигналами с "прямых" выходов триггеров 4 запрещает4Р ся занесение результатов сравнения по сигналам Х, и Х; в триггеры 2 и 3

1 всех разрядон, кроме первого разряда. На входах управления установкой н "единицу" триггеров 2 и 3 перво45 ro Разряда пРисутствует н момент поступления очередного синхроимпульса

CH от генератора сигналов 1 логическая единица с выхода элемента И 5 перного разряда. Результат-сравнения Х„= 1 фиксируется в триггер 2, а результат сравнения Х = 1 — в триггер 3 первого разряда. По сигналу СИ состояние триггера 4 перного разряда меняется с "ноля" на "единицу", так как схема совпадения по входу D, обеспечивающая установку триггера 4 в "ноль", блокируется запрещающим сигналом с "инверсного" ныхода триггера 2 или 3. Далее на

"прямом" выходе триггера 4 устанан873406

Формула изобретения

Блок управления преобразователя напряжения в код последовательного приближения, содержащий генератор сигналов, первый выход которого соединен со входом синхронизации первого и второго триггеров каждого разряда, второй выход — со входом синхронизации третьего триггера каждого разряда, вход сброса триггеров соединен с шиной сброса, первый вход установки в "единицу" первого и вто- . рого триггеров соединен соответственно с шинами "прямого" и "инверсионного" сигналов сравнения, второй вход установки в "единицу" — с выходом элемента И данного разряда, первый выход первого и второго триггеров подключен к-шинам управления цифро-аналоговым преобразователем, второй выход первого триггера соединен с первым входом установки третьего триггера данного разряда, элементы И всех разрядов соединены последовательно, отличающийся тем, что, с целью сокращения аппаратурных затрат, в каждом разряде второй выход второго триггера соединен со вторым входом установки третьего триггера данного разряда, "прямой" выход которого соединен с третьим входом установки в "единицу" первого и второго триггеров следующего разряда, "инверсный" выход третьего триггера соединен со вторым входом элемента И данного разряда, "прямой" выход третьего триггера последнего разряда соединен со входом установки в "ноль" первого и второго триггеров всех разрядов.

Источники информации, принятые во внимание при экспертизе

1. Патент ФРГ 9 1129716, кл.G 06 F 13/00, 1962.

2. Авторское свидетельство СССР по заявке 9 .2697549/21, кл. Н 03 К 13/17, 1978,(прототип. ). выхода триггера 4 первого разряда через элемент И 5 первого разряда запрещается повторное изменение состояния триггеров 2 и 3 первого разряда.

АНалогичным образом происходит разрешение занесения результатов сравнения Х и Х((i62,n) s триггеры 2 и 3, 5 следующих разрядов и запрещение повторного изменения состояния триггеров 2 и 3 предшествующих разрядов.

После занесения результатов сравнения Х„ и Х„ в триггеры 2 и 3 последнего разряда и сигнал логической единицы с,"прямого" выхода триггера 4 последнего разряда поступает на входы установки в ."ноль" триггеров 2 и

3 всех разрядов. В момент прихода очередного сигнала СИ триггеры 2 и

3 всех разрядов переводятся в состояние "ноль". По сигналу СИ это состояние фиксируется триггерами 4 всех разрядов. Устройство вновь пе- 20 реходит в исходное состояние. Ему; соответствует такт определения старшего разряда кода преобразуемого напряжения.

При необходимости управления со- стоянием триггера 4 может быть выполнено по сигналам с "прямых" выходов триггеров 2 и 3. В этом случае по входу 0 реализуется схема собирания, вход D используется для управления установкой триггера 4 в состояние "ноль". При использовании в качестве триггера 4 синхронного Я$триггера управление по входам установки R u S осуществляется по соотношениям

s = (e + e ) . сн

R=5 5.rH

1 Ь где Q1 ° 0 51 i Q - сигналы с "прямых" и "инвер- 40 сных" выходов триггеров 2 и

3.

В устройстве используется Зл однотактных триггеров и и элементов И ° 45

Применение в каждом разряде устрой" ства трех однотактных триггеров вместо двух двухтактных триггеров со- . кращает затраты оборудования на 25%. °

Уменьшение числа схемных элементов . упрощает схему устройства и повышает ее надежность. В преобразователе напряжения в код с предлагаеыам блоком управления повышается быстродействие, так как в данном устройстве сигналы на входы ЦАП поступают с выходов 2 и З,меняющих свое coc o" яние по переднему фронту сигнала CH.

В известном устройстве сигналы на входы цАП поступают с выходов второй ступени двухтактных триггеров 2 и

3, которые меняют свое состояние по сигналам СИ. Последнее обстоятельство увеличивает каждый такт преобразования известного устройства на длительность синхимпульса СИ вЂ” 2-4t где — среднее .время задержки элементов второй ступени двухтактных триггеров.

873406

Составитель В.Махнанов

Редактор И.Митровка Техред A.Ñàâêà Корректор Г.Огар

Заказ 9070/83 Тираж 991 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4