Коммутатор

Иллюстрации

Показать всеРеферат

OllИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскиз

Социалистических

Реснублнк (61) Дополнительное к авт. свид-ву—

<я)м. к. (22) Заявлено 14.1279 . (21) 2855582/18-21 с присоединением заявки М

Н 03 К 17/00

Государственный комнтет

СССР по делам нзобретеннй н открытий (23) Приоритет—

Опубликовано 15.10.81. Бюллетень М 38

Дата опубликования описания 15.1081 (53) УДК 681. 32 (088 ° 8) (72) Автор изобретения

В.С. Голубев (71) Заявитель (5 4 ) КОММУТАТОР

Изобретение относится к автоматике и коммутационной технике.

Известны коммутаторы, содержащие дешифраторы и блоки памяти, а также управляющие и информационные шины .(1). 5

К недостаткам известных устройств относится низкая надежность функционирования.

Наиболее близким по технической сущности к данному является коммутатор, содержащий дешифраторы, первая группа входов первого из которых соединены.с первой группой управляющих шин, а входы второго дешифратора подключены к первой и второй группам 15 управляющих шин, при этом выходы каждого из дешифраторов соединены с управляющими входами соответствующего блока памяти, одноименные информационные входы которых объединены и 20 подключены. к третьей группе управляющих шин, а также информационные входные и выходные шины(23, Недостаток устройства — низкая надежность функционирования. 25

Целью изобретения является повышение надежности коммутатора.

Указанная цель достигается за счет того, что в коммутатор введены мультиплексоры и элементы И, выход : 30 каждого из которых соединен с соответствующей выходной шиной, а входы подключены к одноименным выходам блоков памяти, при этом информационные входы каждого мультиплексора соединены с соответствующей группой информационных входных шин, управляющие входы — co второй группой управляющих шин, а выход подключен к одному из входов второй группы первого дешифратора.

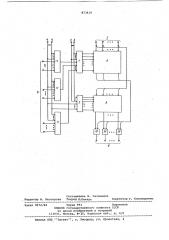

Блок-схема коммутатора представлена. на чертеже.

Она содержит дешифраторы 1 и 2, первая группа входов первого из которых соединена с группой управляющих шин 3, а входы дешифратора 2 подключены к группам управляющих шин 3 и 4, выходы каждого из дешифраторов 1, 2 соединены с управляющими входами соответствующего блока памяти 5,б, одноименные информационные входы которых объединены и подключены к группе управляющих шин 7, информационные. входные 8 и выходные 9 шины, элементы И 10, выход каждого из которых соединен с соответствующей выходной шиной 9, а входы подключены к одноименным выходам блоков памяти

873410

S и 6, информационные входы каждого мультиплексора 11 соединены с соответствующей группой информационных входных шин 8, управляющие входы— с группой управляющих шин 4, а выход подключен к одному из входов второй группы дешифратора 1.

Функционирование коммутатора осуществляется следующим образом.

В режиме настройки информационные входные шины R под воздействием сигналов, поступающих на управляющие шины 4, поочередно подключаются к выходам мультиплексоров 11 и, следовательно, ко входам дешифратора 1.

Сигналы с управляющих шин 4 поступают- также на входы дешифратора 2.

На другие входы дешифраторов 1 и 2 подается код с управляющих шин 3.

Настройка осуществляется индивидуаль но для каждой информационной входной шины 8. При этом на управляющие шины 7, а следовательно, и на информационные входы блоков памяти 5 и .6 подается двоичный код номера выходной шины 9, на которую должна быть подключена информационная входная шина 8. В процессе настройки на информационную входную шину 8 подается единичный сигнал. На остальные информационные входные шины 8 подаются последовательные значения двоичных кодов, которые с выходов мультиплексоров 11 поступают на соответствующие входы дешифратора 1. После получения максимального числа единиц на входах дешифратора 1 осуществляется переход к настройке следующей информационной входной шины

8. В процессе настройки информацианных входных шин 8, подключенных к одноименным входам мультиплексоров

11, одновременно с записью единиц в информационные разряды блока памяти 5 осуществляется запись единиц в одноименные разряды и блоки памяти 6 по адресу, соответствующему коду на управляющих шинах 3 и 4. После завершения программирования информационных входных шин 8, подключенных к одноименным входам мультиплексоров 11, на управляющие шины 4 подается новый код, в соответствии с которым осуществляется подключение другой группы информационных входных шин 8 ко входам дешнфратора 1 и их поочередная настройка. В режиме коммутации коммУтируемые сигналы поступают на информационные входные шины 8, а управляющие сигналы — на шины 3 и 4. При этом на один такт смены информации на информационных входных шинах 8 будет приходиться и тактов смены сигналов на управляющих шинах 4 (где n — число шин, подключенных к информационным входам каждого мультиплексора 11), что обеспечивает

5 (а

20 Таким образом, в предложенном

55 поочередное подключение информационных входных шин 8 ко входу дешифратора 1 и их коммутацию в соответствии с кодом настройки, записанным в блоке памяти 5. В режиме коммутации блоки памяти 5 и 6 спрашиваются . одновременно. При этом блок памяти

5 опрашивается по адресу, соответствующему коду на информационных входных юинах 8, поцключенных ко вхадай дешифратора 1, а блок памяти 6 опрашивается по адресу, соответствующему коду на управляющих шинах 4, подключенных ко входу дешифратора 2.

При опросе блоков памяти 5 и 6 на входы элементов И 10 с выходов блоков памяти 5 и 6 будут поступать сигналы в соответствии с записанной . в них программой и кодом на информа" ционных входных шинах 8. коммутаторе путем введения мультиплексоров и элементов И достигается уменьшение объема блоков памяти 5 и 6, тем самым, повышение надежности коммутатора.

Формула изобретения

Коммутатор, содержащий дешифраторы, первая группа входов первого из которых соединена с первой группой управляющих шин, а входы второго дешифратора подключены к первой и второй группам управляющих шин, при этом выходы каждого из дешифраторов соединены с управляющими входами соответствующего блока памяти, одноименные информационные входы которых объединены и подключены к третьей группе управляющих шин, а также информационные входные и выходные шины, отличающийся тем, что, с целью повышения надежности, в него введены мультиплексоры и элементы И, выход каждого из которых соединен с соответствующей выходной шиной, а входы подключены к одноименным выходам блоков памяти, при этом информационные входы каждого мультиплексора соединены с соответствующей группой информационных входных шин, управляющие входы — со второй группой управляющих шин, а выход подключен к одному из входов второй группы первого дешифратора.

Источники информации, принятые Во внимание при экспертизе

1. Авторское свидетельство СССР

Р 4784 39, кл. Н 03 К 17/00, 30 . 11, 73 .

2. Авторское свидетельство СССР по заявке Р 2668663/21, кл. Н 03 К 17/00, 02.10.78,26.03.79 (прототип).

873410

Тираж 991 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 9072/84

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4

Сост авитель В. Чачанидз е

Редактор И. Нестерова Техред Л, Пекарь Корректор у. Пономаренко