Многоканальное устройство приема шумоподобных сигналов

Иллюстрации

Показать всеРеферат

Оп ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТИЗЬСТВУ

<1ц873421

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. саид-ву— (22) Заявлено 070979. (21) 2832210/18-09 с присоединением заявки ¹â€” (23) Приоритет—

Опубликовано 15.1081.Бюллетень № 38

Дата опубликования описания 15.1681

Р )м. кл.з

Н 04 В 1/06

Государственный комитет

СССР но делам изобретений я открытий (53) УДК 621 ° 372 57 (088.8) Ю

В. В. Барлабанов, Л. Г. Гассанов, A.A. Паламарчук, В. Д.ушаков, М. A. Хмелевский и В. Д. Чернышев 1 -.

1, (72) Авторы ,изобретения (71) Заявитель (54) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИЕМА шуМОпОдОБных сиГнАлОВ

Изобретение относится к контурам, импульсная характеристика которых приближается к заданной временной функции, и может использоваться в системах передачи дискретной информации.

Известно многоканальное устройство приема шумоподобных сигналов, содержащее двоичный квантователь, вйход которого подключен к первому входу регистра сдвига, второй вход которого соединен с выходом генератора тактовых импульсов и входом двоичного квантователя, при этом выходы регист- 15 ,ра сдвига подключены к соответствующим входам и блоков сравнения,,.где и — количество разрядов регистра сдвига, причем другие входы блоков срав-. нения соединены с соответствующими 2О выходами коммутатора опорных кодов, выходы блоков сравнения подключены к соответствующим входам сумматора, при этом вход генератора тактовых импульсов соединен с первым выходом блока управления, второй выход кото-. рого подключен ко входу коммутатора опорных кодов Г13 .

Однако известное многоканальное устройство приема шумоподобных.сигналов имеет невысокую помехоустойчивость.

Целью изобретения является повышение помехоустойчивости.

Для этого в многоканальное устройство приема шумоподобных сигналов, содержащее двоичный квантователь, выход которого подключен к первому входу регистра сдвига, второй. вход которого соединен с выходом генератора тактовых импульсов и входом двоичного квантователя, при этом выходы регистра сдвига подключены к соответствующим входам и блоков сравнения,где

n — количество разрядов регистра сдвига, причем другие входы блоков сравнения соединены с соответствующими выходами коммутатора опорных кодов, выходы блоков сравнения подключены к соответствукидим входам сумматора, при этом вход генератора тактовых импульсов соединен с первым выходом блока управления, второй выход которого подключен ко входу ковмутатора опорных кодов, введены делитель, управляеваий инвертор, коммутатор и а канальных блоков, где е — количество каналов, при этом вход делителя соединен с выходом генератор4е тактовых импульсов, а выход, целителя под873421 ключен к первым и вторым входам канальных блоков, третий и четвертый входы которых соединены с соответствующими выходами коммутатора, при этом первый вход коммутатора соеди1 нен с третьим выходом блока управле5 ния, второй вход коммутатора соединвй с первым выходом сумматора и входом управляемого инвертора, выходы которого подключены к соответствующим входам коммутатора, а другие входы управляемого инвертора соединены с соответствующими выходами сумматора..

В многоканальном устройстве обработки шумопободных сигналов каналь-ный блок содержит элемент памяти,стро . бирующий элемент, компаратор и парал- лельный регистр, при этом первый вход параллельного регистра является первым входом канального блока, а второй вход параллельного регистра соединен с выходом компаратора и первым вхо- 20 дом элемента памяти, при этом второй вход элемента памяти является третьим входом канального блока, выход элемента памяти подключен к первому входу стробирующего элемента, второй . 25 вход которого является вторым входом канального блока„ при этом дополнительные входы параллельного регистра, соединенные с соответствующими входами компаратора, являются четвертыми входами канального блока, а выходы параллельного регистра подключены к дополнительным входам компаратора.

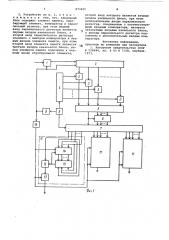

На фиг. 1 представлена структурная электрическая схема многоканального уотройства приема шумоподобных сигналов; на фиг. 2 — временные диаграммы напряжений, поясняющие работу устройства, где g — напряжение на.выходе генератора тактовых импульсов (ГТИ); 6 — напряжение тактовой 46 частоты блока управлениями 8 — напряжение на входе регистра сдвигау напряжение на выходе компаратора; ф напряжение на выходе элемента памяти;

2е — напряжение на выходе делителя;

2ж — напряжение на выходе стробирующего элемента.

Многоканальное устройство приема шумоподобных сигналов содержит двоичный квантователь 1 на два уровня,пер- у0 вый выход которого соединен со входом п — разрядного регистра сдвига 2, выходы которого подключены к соответ-ствующим входам и блоков сравнения 3, вторые входы которых соединены с выходами коммутатора 4 опорных кодов, выходы п блоков сравнения 3 подключе" ны к п входам сумматора 5, первый выход (старший разряд) которого подключен к входу управляемого инвертора (УИ) б и к второму входу коммутатора ЬО

7 первый вход которого соединен с третьим выходом блока управления 8, первый выход которого соединен со входом генератора тактовых импульсов 9, выход которого соединен с делителем б5

10, подключенным, в свою очередь, к. первым и вторым входам каждого из mканальных блоков 11, где m - количество каналов, состоящих каждый из,элемента памяти 12, стробирующего элемента 13, параллельного регистра 14 и компаратора 15.

Многоканальное устройство приема шумоподобных сигналов работает сле1 дующим образом.

Входной сигнал поступает на вход двоичного квантователя 1, где производится выборка значений входного сигнала в двоичном коде (фиг. 2в) с частотой, равной частоте следования импульсов генератора тактовых импульсов 9 (фиг. 2a), которая устанавливается блоком управления 8 ° Принятый код записывается тактовыми импульсами в последовательный регистр сдвига 2, число разрядов которого равно числу элементов (базе) шумоподобного сигнала. За время, равное периоду следования тактовых импульсов, по сигналу блока управления 8 в коммутаторе 4 опорных кодов происходит циклическая смена опорных кодов,.число которых равно числу обрабатываемых каналов (фиг. 25). Коммутатор 4 опорных кодов может быть выполнен в виде постоянного запоминающего устройства, в котором записано необходимое количество опорных канальных кодов.

На выходах блоков сравнения 3 каждый раз после смены опорного кода появляется столько единиц, сколько совпадений было между принятым и опорным кодами,(n-входовый цифровой параллельный) сумматор 5 производит суммирование единиц и формирует на своих выходах параллельных двоичный код числа совпадений.

Двоичный код на выходах сумматора

5 показывает значение функции корреляции между принятым и опорным кода ми, которое будет максимальным при совпадении опорного и принятого кодов. Появление "1" .или "0" на выходе старшего разряда сумматора 5 может служить сигналом приема прямого или обратного шумоподобного сигнала соответственно, при этом остальные разряды дают оценку корреляции опорного кода как с пряным, так и с обратным принятым сигналом. Это достигается с помощью управляемого инвертора,б, который может быть выполнен на сумматорах по модулю два. Например, дпя и 31. при приеме прямого по отношению к опорному сигнала на выходю. сумматора 5 в момент совпадения будет код 11111, а на выходе управляемого б npH swoM - код 1111 В случае приема обратного по отношению к этому опорному коду сигнала на выходе сумматора будет код 00000, а на выходе управляемого инзертора б

1111.

87342".

Формула изобретения

Таким образом, когда информация передается прямыми и обратными шумо; подобными сигналами, двоичный код на выходе управляемого инвертора 6 служит оценкой корреляции принятого сигнала и опорного кода, а выход старшего разряда сумматора 5 может использоваться в качестве информационного. Коммутатор 7 по сигналу блока управления 8 синхронно со сменой опорных кодов в коммутаторе 4 опорных кодов подключает выходы уп-. равляемого инвертора 6 и старший разряд сумматора 5 к соответствующему канальному блоку 11. В каждом канальном блоке 11 выходы младших разрядов коммутатора 7 подключены к соответствующим входам параллельного регистра 14, который в начальный момент цикла устанавливается в нулевое состояние, и компаратора 15, на выходе которого появляется сигнал перезапи- 20 си. в случае, если поступивший двоичный код больше записанного в параллельном регистре 14. По сигналу перезаписи компаратора 15 в параллельный регистр 14 записывается поступивший в канал двоичный код и, одновременно, в элемент памяти 12 записывается информационная посылка (фиг.

23), в качестве которой при передаче информации противоположными сигналами используется значение старшего разряда сумматора 5, а в случае передачи информации ортогональными кодами - сигнал блока управления.

Через и тактов генератора тактовых. импульсов 9 с делителя 10 (Фиг.

2е) на стробирующий элемент 13 поступает импульс опроса, после чего на выходе канальных блоков 11 появляются информационные посылки (Фиг. 2Ф), а параллельные регистры 14 устанавли- 40 ваются в начальное состояние.

Таким образом, за время, равное длительности шумоподобного сигнала, происходит определение переданной информационной посылки в соответствии щ с максимумом функции корреляции между принятыми и опорными кодами беэ дополнительной синхронизации по циклам и наличия жесткого порога срабатывания, 50

Процесс выделения информационной. посылки, соответствующей максимуму функции взаимной корреляции принимаемого и опорного кодов, хорошо виден, из временных диаграмм (Фиг. 2). В начале цикла работы первый тактовый импульс (см. Фиг. 2ц) вызывает появле- ние импульса на выходе компаратора

15 (см. Фиг. 2 ), так как начальное состояние параллельного регистра 14 нулевое; после второго тактового им- 60 пульса отклик сумматора 5 больше,что опять приводит к появлению импульса на выходе компаратора 15 и смене состояния элемента памяти 12 (см. Фиг. ,26). Как следует иэ графиков, йри 65 появлении третьего тактового импуль- са происходит максимальное совпадение принятого и опорного кодов для данного канала, так как в течение остальной части цикла сигнал на выходе компаратора не появляется и элемент памяти 12 хранит информацию, записанную в него во время действия третьего тактового импульса. Конец цикла анализа определяется импульса ми, поступающими с делителя 10 (см.

Фиг. 2е ), которые снимают информацию (см. Фиг. 2а) и стирают максимальное значение отклика из параллельного регистра 14, подготавливая, таким образом, устройство для следующего цикла работы„

Предложенное устройство позволяет повысить помехоустойчивость принимаемой информации за счет устранения необходимости использования жесткого порога при принятии решения, а также повысить быстродействие путем.использования параллельного суммирования . отклика.

Многоканальное устройство приема шумоподобных сигналов, содержащее двоичный квантователь, выход которого подключен к первому входу регист-. ра сдвига, второй вход которого соединен с выходом генератора тактовых импульсов и входом двоичного квантователя, при этом выходы регистра сдвига подключены к соответствующим входам и блоков сравнения, где в — количество разрядов регистра сдвига, причем другие входы блоков сравнения соединены с соответствующими выходами коммутатора опорных кодов, выходы бло-. ков сравнения подключены к соответствующим входам сумматора, при этом вход генератора тактовых импульсов соединен с первым выходом блока управления, второй выход которого подклю-. чен ко входу коммутатора опорных кодов, отличающийся тем, что, с целью повышения помехоустойчивости, введены делитель, управляемый инвертор, коммутатор и m канальных блоков, где m — количество каналов, при этом вход делителя соединен с выходом генератора тактовых импульсов, а выход делителя подключен к первым и вторым входам канальных блоков, третий и четвертый входы которых соединены с соответствующими выходами коммутатора, при этом первый вход коммутатора соединен с третьим выходом блока управления, второй вход коммутатора соединен с первым выходом сумматора и входом управляемого инвертора, выходы которого подключены к соответствующим входам коммутатора, а другие входы управляемого инвертора соединены с соответствующими выходами сумматора.

2. Устройство по и. 1, о т л и ч а ю щ е е с я тем, что, канальный блок содержит элемент памяти, страбирующий элемент, компаратор и параллельный регистр, при этом первый вход параллельного регистра является первым входом канального блока, а второй вход параллельного регистра соединен с выходом компаратора и первым входом элемента памяти, при этом второй вход элемента памяти является третьим входом канального блока, выход элемента памяти подключен к первому входу стробирующего элемента, второй вход которого является вторым входом канального блока, при этом дополнительные входы параллельного регистра, соединенные с соответствующими входами компаратора, являются четвертыми входами канального блока, а выходы параллельного регистра подключены к дополнительным входам компаратора.

Источники информации, принятые во внимание при экспертиэе

1. Авторское свидетельство СССР

Р 528б84, кл. Н 03 H 7/28, опублик.

1973.

873421

Составитель Г.Челей

Редактор М.Недолуженко Техред С.Мигунова Корректор У.Пономаренко

Заказ 9073/84 Тираж 701 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4