Устройство для приема информации по двум параллельным каналам связи

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик (11)

ИЗЬБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 17.12.79 (21) 2869244/18-09 с присоединением заявки №вЂ” (23) Приоритет— (51) М.К .

Н 04 L 1/16

Гееудеретееннмй кемнтет (53) УДК 621.394..14(088.8) Опубликовано 15.10.81. Бюллетень № 38

Дата опубликования описания 25.10.81 но делам нзееретеннй и еткрмтнй (72) Авторы изобретения

Н. М. Золотоносов, Г. П. Евланов и И. А. Ша

3

41дрр бди 1,I (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ

ПО ДВУМ ПАРАЛЛЕЛЬНЫМ КАНАЛАМ СВЯЗИ

Изобретение относится к технике передачи данных и может использоваться при разработке устройств повышения достоверности приема информации.

Известно устройство для приема информации по двум параллельным каналам. связи в системе передачи с решающей обратной связью, содержащее,два блока повышения достоверности, выходы которых подключены к информационным входам логического блока, к управляющему входу которого подключен выход сумматора, а один из выходов логического блока подключен ко входу бЛока управления повторением кодовых комбинаций, а также накопители, регистр сдвига и ключевые блоки (1).

Однако известное устройство имеет низкую достоверность принимаемой информации.

Цель изобретения — повышение достоверности принимаемой информации.

Цель достигается тем, что в устройство для приема информации по двум параллельным каналам связи в системе передачи с решающей обратной связью, содержащее два блока повышения достоверности, выходы которых подключены к информационным входам логического блока, к управляющему входу которого подключен выход сумматора, а один из выходов логического блока подключен ко входу блока управления повторением кодовых комбинаций, а также накопители, регистр сдвига и ключевые блоки, введены блок защиты, блок управления считыванием информации, дополнительный регистр сдвига и элемент ИЛИ, при этом ко входам элемента ИЛИ подключены вы16 ходы ключевых блоков, первые входы которых объединены с первыми управляющими входами накопителей и подключены к соответствующим управляющим выходам блока управления считыванием информации, вторые управляющие выходы которого подклю1> чены соответственно ко вторым управляющим входам накопителя, к информационным входам которых подключены соответствующие выходы логического блока, а выходы накопителей соответственно через регистр сдвига и дополнительный регистр сдвига подключены ко входам сумматора, объединенным с соответствующими входами ключевых блоков, управляющие выходы логичес873437 кого блока подключены к соответствующим входам блока управления считыванием информации, к другим входам которого подключены соответственно вход установки в начальное положение и один из выходов блока защиты, другйе. выходы которого подключены соответственно к информационным входам блоков повышения достоверности и логического блока, к соответствующему входу которого подключен выход блока управления считыванием информации, причем входы блока защиты являются соответственно входами информационного сигнала, тактовых импульсов, сигнала установки начального положения служебных сигналов.

При этом блок защиты содержит два канала, каждый из которых состоит из последовательно соединенных первого элемента И, триггера и второго элемента И, а также последовательно соединенные элемент

ИЛИ, выходной элемент И и таймер, выход которого подключен к объединенным входам выходного элемента И и первых элементов

И обоих каналов, выходы триггеров которых подключены ко входам элемента ИЛИ; причем вторые входы вторых элементов И обоих каналов являются входами информационных сигналов, третий вход выходного элемента

И вЂ” входом тактовых импульсов, объединенные входы триггеров обоих каналов— входом сигнала установки начального положения, вторые входы первых элементов И обоих каналов — входами служебных сигналов.

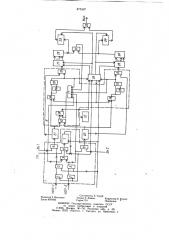

На чертеже представлена структурная электрическая схема предложенного устройства.

Устройство для приема информации по двум параллельным каналам связи в системе передачи с решающей обратной связью содержит блок защиты 1, состоящий из двух каналов, каждый из которых состоит из первого элемента И 2, триггера 3 и второго элемента И 4, и элемента ИЛИ 5, выходного элемента И 6 и таймера 7, логический блок 8, состоящий из четырех элементов И 9 — 12, двух элементов НЕ 13 и 14, двух элементов

ИЛИ-НЕ 15 и 16,-двух триггеров 17 и 18 и элемента ИЛИ 19, два блока повышения достоверности 20 и 21, блок 22 управления повторением кодовых комбинаций, элемент ИЛИ 23, два ключевых блока 24 и 25, блок 26 управления считыванием информации, два накопителя 27 и 28, регистр сдвига 29, дополнительный регистр сдвига 30, сумматор 31.

Устройство работает следующим образом.

На его вход поступают сигналы КФП-1, КФП-2 (конец фазирующей последовательности), соответствующие моментам вхождения в синхронизм (установки фазы) в каждом канале системы передачи данных под воздействием фазирующих последовательностей,. обеспечивающих цикловую синхронизацию. Эти сигналы поступают на первые

f5 триггеров 3.

В этом состоит механизм защиты от при-. ема разной информации. Данная схема может быть расширена на любое число каналов для чего соответственно увеличивают число элементов И 2 и триггеров 3. При допустимом временном сдвиге между сообщениями их обработку ведут оба блока повышения достоверности.

При обнаружении ошибки в поступающей информации на управляющем выходе блока повышения достоверности 20 и 21 возникает «единичный» сигнал, который, будучи проинвертированным в элементе

ИЛИ-НЕ 15 и 16 логического блока 8, устанавливает триггеры 17 и 18 в «нулевое» состояние, при котором сообщение с информационного выхода блоков повышения достоверности 20 и 21 не поступает в накопители 27 и 28.

При обнаружении ошибки в обоих блоках повышения достоверности возникает сигнал на выходе элемента И 12, который через элемент ИЛИ 19 обеспечивает выдачу из блока 22 управляющего сигнала на повторение кодовых комбинаций.

Информация о наличии ошибок, обнаруженных блоками повышения достоверности-20 и 21 с выхода триггеров 17 и 18, а также с выхода элемента ИЛИ 19 (когда ошибки обнаружены в обоих каналах), поступает в блок управления 26, который управляет считыванием информации из накопителей 27 и 28 и отпиранием ключевых блоков 24 и 25.

Отсутствие ошибок в каналах сопровождается «нулевым» сигналон на управляющих выходах блоков повышения достоверности 20 и 21, что обеспечивает установку триггеров 17 и 18 в «единичное» состояние и запись сообщений в накопители 27 и 28.

После поступления выходного сигнала с таймера 7 блок 26 управления считыванием информации формирует управляющие о

25 зо

$$ элементы И 2 блока 1 защиты от приема . сообщений разного содержания и устанавливают триггеры 3 в «единичное» состояние, что обеспечивает прохождение информации к блокам повышения достоверности 20 и 21, В исходном состоянии первые элементы

И 2 обеспечивают прохождение входных сигналов КФП. Первый из пришедших сигналов КФП, установив один из триггеров 3 в «единичное» состояние, через элемент или

5и выходной элемент И 6 запускает таймер 7, который отсчитывает максимальное время, на которое могут быть сдвинуты в каналах связи сообщения одного и того же содержания. Выходной сигнал таймера блокирует все первые элементы И 2 и выходной элемент И 6 и, если второй сигнал КФП к этому моменту не поступает, то сообщение, соответствующее данному каналу, на блок повышения достоверности не подается, так как остается в «нулевом» состоянии один из

873437,сигналы на одновременное считывание информации с накопителей 27 и 28, которая с выходов регистров 29 и 30 в последовательном виде подается на входы сумматора 31. При обнаружении несравнения на выходе сумматора 31 возникает «единичный» сигнал, который через элемент И 11, элемент ИЛИ 19 воздействует на блок 22 управления повторением кодовых комбинаций .

Сигнал на выходе элемента И 11 возникает при «единичном» состоянии триггеров 17 и 18 (отсутствие ошибок, обнаруживаемых блоками повышения достоверности) и триггеров 3 блока 1 (в принятых сообщениях содержание идентично). В случае отсутствия несравнений на выходе сумматора 31 блок 26 формирует управляющий сигнал, обеспечивающий открывание ключевого блока 25 и повторное считывание сообщения с накопителя 27, которое через элемент ИЛИ 23 поступает к получателю.

Учитывая, что считывание с накопителей 27 и 28, когда осуществляется сравнение, на сумматоре, производится на высокой скорости, по крайней мере на два порядка превышающей скорость прохождения информации в каналах связи, операция сравнения на сумматоре 31 не вызывает заметной задержки сообщений.

Если в одном из каналов соответствующий ему блок повышения достоверности обнаружит ошибки, на его управляющем выходе возникает «единичный» сигнал и, следовательно, соответствующий триггер 17 или 18 устанавливается в «нулевое» состояние. При этом не происходит записи информации в накопитель, что отмечается в блоке сравнения информации. В этом случае блок

26 сразу формирует второй сигнал считывания с накопителя с одновременным вскрытием соответствующего ключевого блока, и информация через элемент ИЛИ 23 поступает на выход устройства.

Таким образом, в устройстве реализована зашита от приема с двух параллельных каналов сообщений разного содержания, что обеспечивает осуществление данного метода повышения достоверности приема информации, а также осуществлена синхронная выдача сообщений для их поэлементного сравнения, без чего операция сравнения невыполнима.

Формула изобретения

Устройство для приема информации по двум параллельным каналам связи в системе передачи с решающей обратной связью, содержащее два блока повышения достоверности, выходы которых подключены к информационным входам логического блока, к управляющему входу которого подключей выход сумматора, а один из выходов логического блока подключен ко входу блока управления повторением кодовых комбинаций, а также накопители, регистр сдвига и ключевые блоки, отличающееся тем, что, 5 с целью повышения достоверности принимаемой информации, введены блок зашиты, блок управления считыванием информации, дополнительный регистр сдвига и элемент

ИЛИ, при этом ко входам элемента ИЛИ подключены выходы ключевых блоков, первые входы которых объединены с первыми управляющими входами накопителей и подключены к соответствующим управляющим выходам блока управления считыванием информации, вторые управляющие выходы которого подключены соответственно ко вторым управляющим входам накопителей, к информационным входам которых подключены соответствующие выходы логического блока, а выходы накопителей соответственно через регистр сдвига и дополнительный регистр сдвига подключены ко входам сумматора, объединенным с соответствующими входами ключевых блоков, управляющие входы логического блока подключены к соответствующим входам блока управления считыванием информации, к другим входам которого подключены соответственно вход установки в начальное положение и один из выходов блока защиты, другие выходы которого подключены соответственно к информационным входам блоков повышения

Зо достоверности и логического блока, к соответствующему входу которого подключен выход блока управления считыванием информации, причем входы блока защиты являются соответственно входами информационного сигнала, тактовых импульсов, сигнала установки начального положения служебных сигналов.

2. Устройство по п. 1, отличающееся тем, что блок защиты содержит два канала, каждый из которых состоит из последова4О тельно соединенных первого элемента И, триггера и второго элемента И, а также последовательно соединенные элемент ИЛИ, выходной элемент И и таймер, выход которого подключен к объединенным входам выходного элемента И и первых элементов

45 И обоих каналов, выходы триггеров которых подключены ко входам элемента ИЛИ, причем вторые входы вторых элементов И обоих каналов являются входами информационных сигналов, третий вход выходного элемента И вЂ” входом тактовых импульсов, объединенные входы триггеров обоих каналов — входом сигнала установки начального положения, вторые входы первых элементов

И обоих каналов — входами служебных сигналов.

S5 Источники информации принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 473314, кл. Н 04 1. 1/16, 1972 (прототип).

873437

Ь

Составитель E. Голуб

Редактор Т. Веселова Тех ред А. Войк а с Корректор Е. Рошко

Заказ 9078/85 Тираж 701 Подписное

ВНИИПИ Государственного, комитета СССР по делам изобретений и оз крытий

I 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4