Цифровой когерентный частотно-фазовый демодулятор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНЙЯ

Сееоз Советских

Социалистических

Республик

<>873453

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву (22) Заявлено 230Ц79 (21) 2814210/18-09 (51)М. Клз с присоединением заявки М

Н 04 L 27/18

Государственный квинтет

СССР но дмаи нзобретеннй н открытнй (23) Приоритет

Опубликовано 151081. Бюллетень Н9 38

Дата опубликовамия описания 15.1 0.81 (53) УДК 621. 376. 32 (088. 8) (72) Авторы изобретения

В.В.Калмыков, А,A,Ñòîìàõèí, Ю.A.Ìàêñèìîâ и -М.Селезнев;

1

Московское ордена Ленина и ордена Трудового Красньго

Знамени высшее техническое училище им. Н.Э.Баумана (71) Заявитель (54) ЦИФРОВОЙ КОГЕРЕНТНЫЙ ЧАСТОТНО-ФАЗОВЫЙ, ДЕМОДУЛЯТОР.1

Изобретение относится к устройствам обработки дискретных сигналов и может использоваться в системах радиосвязи, радиотелеграфии и провод- с ных автоматизированных системах передачи данных.

Известен когерентный управляемый демодулятор ЧМ-ФМ сигналов, состоящий из последовательно соединенных ,некогерентного частотного детектора, формирователя опорного ЧМ колебания. для работы фазового детектора и когерентного фазового детектора (1j.

Безынерционное формирование опорного ЧМ колебания обеспечивается 15 при полосе,синхронизма, равной или несколько большей разности частот

ЧМ сигнала, поэтому подобные демодуляторы имеют низкую помехоустойчивость» 20

Известен также цифровой когереит- ный частотно-фазовый демодулятор, содержащий входной аналого-цифровой преобразователь, подключенный к первым входам двух элементов и н епосред- 25 ственно, а ко вторым — через первый и второй формирователи опорных колебаний соответственно, причем выходы элементов И подключены к элементу сравнения через реверсивные счетчи- 30 ки, а также блок тактовой синхронизации, подключенный к управляющим входам элемента сравнения и реверсивных счетчиков 2 .

Однако этот демодулятор имеет низкую помехоустойчивость.

Цель изобретения — повышение помехоустойчивости.

Цель достигается тем, что в цифровой когерентный частотно-фазовый демодулятор, содержащий входной аналого-цифровой преобразователь, подключенный к первым входам двух элементов И непосредственно, а ко вторым — через первый и второй формирователи опорных колебаний соответственно, причем выходы. элементов И подключены к элементу сравнения через реверсивные счетчики, а также блок тактовой синхронизации, подключенный к управляющим входам элемента сравнения и реверсивных счетчиков, введены последовательно соединенные коммутатор, управляющий вход которого соединен с выходом элемента сравнения, элемент памяти и декодер, между выходом каждого реверсивного счетчика и входами коммутатора включен соответствующий пороговый элемент, а между выходом элемента сравнения

873453 и управляющими входами формирователей опорных колебаний включен элемент. фаэирования, причем блок тактовой синхронизации подключен к выходу входного аналого-цифрового преобразователя и выполнен в виде последовательно соединенных некогерентного фазового демодулятора и блока тактовой автоподстройки частоты, меж-. ду выходом которого и дополнительными входами формирователей опорных .колебаний включен блок защиты, при этом выход блока тактовой синхронизации подключен к управляющим входам элемента фазирования и пороговых элементов.

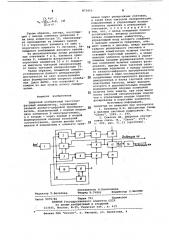

На чертеже изображена структурная электрическая схема цифрового когерентного частотно-фазового демодулятора.

Демодулятор содержит входной аналого-цифровой преобразователь (АЦП)

1, первый и второй формирователи 2 и 3 опорных колебаний, элемент фазирования 4, элементы И 5 и 6, реверсивные счетчики 7 и 8, элемент сравнения 9, пороговые элементы 10 и 11, коммутатор 12, элемент памяти 13„ декодер 14, блок тактовой синхронизации 15, состоящий из последовательно соединенных некогерентного фазового демодулятора 1б, блока тактовой автоподстройки частоты 17 и блока защиты 18.

Цифровой когерентный частотнофазовый демодулятор работает следующим образом.

С выхода АЦП 1, содержащего последовательно соединенные канальный полосовой фильтр, усилитель-ограничитель и формирователь импульсов перехода, следующих с частотой периодов входного колебания, импульсы подаются на первый и второй формирователи опорных колебаний 2 и 3 и некогерентный фазовый демодулятор 1б блока тактовой синхронизации 15 °

Формирователи опорных колебаний 2 и 3 представляют собой цифровые ФАПЧ с дискретным управлением. При наличии импульсов тактовой синхронизации один из формирователей 2 и 3 работает в режиме слежения, а другой в это время находится s режиме срыва, поэтому по сигналу тактовой синхронизации в конце посылки производится фазирование формирователя, находившегося в режиме срыва, от другого формирователя через элемент фазирования 4. При пропадании сигнала на входе демодулятора с выхода блока защиты 18 на дополнительные входы первого и второго формирователей .2 и 3 подается сигнал на обработ ку режима ввода в синхрониэм,,при котором полоса синхроназма формирователей более широкая, чем в режиме слежения. При восстановлении канала связи,по сигналу тактовой синхронизации формирователи 2 и 3 вновь переводятся в режим слежения с узкой полосой синхронизма. С выходов формирователей 2 и 3 и АЦП 1 сигналы подаются на входы элементов И 5 и б.

С выходов последних импульсы рассогласования подаются на входы добавления и вычитания реверсивных счетчиков 7 и 8.

3а исходный алгоритм работы демо.дулятора взят алгоритм работы оптимального корреляционного приемника %

I((<)C,() ae-f(8)CУ) И со" () где $ (t) — принимаемый сигнал, gÄ(t), 0 (с) — опорные сигналы, получаемые с формирователей 2 и 3, длительность эле20 ментарной посылки.

Но выражение (1! соответствует одноканальному демодулятору.

В случае частотно-фазового сигнала числовое значение на выхЬде реверсивного счетчика при одной и той же частоте меняет знак в зависимости от фазы сигнала. Поэтому для выделения информации частотного канала элемент сравнения 9 должен оце.нивать абсолютные значения чисел, N поступающих на него в параллельном коде с реверсивных счетчиков 7 и 8, т.е. необходимо реализовать следующий алгоритм

Л Г

35 г а0"-) фЖС,()Щ-13F()C ®e) 0 . Л) 1 о

После устранения частотной неопре деленности информация фазового канала выделяется пороговыми элемента

4)) ми 10 и 11, которые выносят решение о фазе принимаемого сигнала по следующему алгоритму

Ю>О, (f(g) G«a)®>i0

45 (2)

ЬО<О, );()С ()а О 0

О

Элемент сравнения 9, реализующий алгоритм (2), формирует выходной .сигнал следующим образом1

41) х!)М 1 ф„а Я 15)-)Þ, (4)

О,)Xl<)Я 1 где Х, У - числа s реверсивных счетчиках 7 и 8 °

Выходной сйгнал элемента сравне ния 9 соответствует огибающей частот-. ного канала. Пороговые элементы 10 и 11, реализующие алгоритм (3), производят операцию сравнения поступаю-, щих с выходов реверсивных счетчиков

7 и 8 чисел с нулем и формируют

65 сигнал следующим образом:

873453

Формула изобретения

Составитель Н.Пантелеева

Техред И.Гайду Корректор С.Шекмар

Редактор Т. Веселова

9аказ 9079/8б Тираж 701 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35; Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Таким образом, сигнал,, поступаю- щий с выхода элемента сравнения 9 на вход коммутатора 12, обеспечивает прохождение на элемент памяти

13 с порогового элемента 10 либо с порогового элемента 11 сигналов, являющихся огибающими фазового канала.

На дополнительные входы реверсивных счетчиков 7 и 8, элемента сравнения 9, элемента фазирования 4 и пороговых элементов 10 и 11 подаются импульсы тактовой синхронизации от блока тактовой синхронизации 15 .

Таким образом, повышение помехо.устойчивости данного демодулятора достигается за счет использования двух формирователей опорного колебания (двух ФАПЧ), что позволяет в каждом из них сузить полосу синхронизма.

Цифровой когерентный частотнофаэовый демодулятор,.содержащий входной аналого-цифровой преобразователь, подключенный к первым входам двух элементов И непосредственно, а к вторым — через первый и второй формирователи опорных колебаний соответственно, причем выходы элементов И подключены к элементу сравкения через реверсивные счетчики, а также блок тактовой синхронизации, подключенный к управляющим входам элемента сравнения и реверсивных счетчиков, отличающийся тем, что, с целью повышения помехоустойчивости, введены последовательно соединенные коммутатор,управляющий вход которого соединен с выходом элемента сравнения, эле о мент памяти и декодер, между выходом каждого реверсивного счетчика и входами коммутатора включен соответствующий пороговый элемент, а между выходом элемента сравнения и управляющими входами формирователей опор-" ных колебаний включен элемент фазирования, причем блок тактовой синхронизации подключен к выходу входного аналого-.цифрового преобразователя и выполнен в виде последовательно

20 соединенных некогерентного фазового демодулятора и блока тактовой автоподстройки частоты, между выходом которого и дополнительными входами формирователей опорных колебаний включен блок защиты, при этом выход блока тактовой синхронизации подключен к управляющим входам элемента фазирования и пороговых элементов.

Источники информации, принятые во внимание при экспертизе

1. Бухвинер В.Е. Дискретные схемы в фазовых системах радиосвязи. M,„

"Связь", 1969, с. 140.

2. Спилкер Дж. Цифровая спутниковая связь. M., "Связь", 1979, с. 292, рис. 11.23 (прототип).