Цифровой фазовый детектор

Иллюстрации

Показать всеРеферат

ОПИСЛНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Респубнин ц8753ОЗ (61) Дополнительное к авт. саид-ву— (22} Заявлено 12. 02. 80 (21) 2886011/18-21 (51) М. Кл.

6 01 11 25/04 с присоединением заявки 1та—

Вкуааратеевй квинтет

CCCP яе «евам изабретений я етарнткй (23 ) Й риоритет—

Опубликовано 23 10.81 ° бюллетень Яа 39 (53) УДK.б21.317. .772(088.8) Дата опубликования описания 25. 10.81 (72) Авторы изобретения

В.И. Козлов, И.Е. Чеченя и Г.Д. ШумиХин

I (71) Заявитель (54) ЦИФРОВОЙ ФАЗОВЫЙ ДЕТЕКТОР

Изобретение .относится к радиотехнике и может быть использовано для детектирования радиосигналов с угло- . вой модуляцией, для получения сигналов рассогласования в системах автоматической подстройки частоты (АПЧ) а также для формирования сетки стабильных частот в приемонередающей и измерительной аппаратуре.

Известно устройство цифрового фазового детектирования на неравных частотах, основанное на приведении частот к равенству путем их деления в целое число раз цифровыми методами

Устройство предназначается для целей частотного синтеза и именно здесь нашло в свое время широкое применение I l ).

Однако из-за инерционности, вносимой делителями частоты в случае, когда частоты некратны и имеют малый общий множитель, устройства такого типа не удовлетворяют возросшим требованиям к динамической, точности петектирования и применение их в настоящее время весьма ограничено.

Известно также устройство цифрофазового синтеза, которое в значительной степени устраняет этот недостаток. Устройство основано на применении делителя частоты с дробным переменным коэффициентом деления и цепи компенсации помех дробности, в которой аналоговый сигнал фазового де16, тектора суммируется с функцией накопления дробной части коэффициента деления, также преобразованной в аналоговую форму $2).

Однако точность детектирования в

- этом случае определяется остаточным (нескомпенснрованным) уровнем помех дробности, который зависит от точности аналогового суммирования и стабильности во времени и в температуре статических характеристик фазового детектора, цифроаналогового преобразователя (ЦАП) и суммирующего устройства.

Из-эа этого не удается достичь ус875303 тойчивой компенсации помех дробности до уровня ниже 40 дБ, что чаще всего оказывается недостаточным.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее два накопительных регистра, цифровой сумматор и

ЦАП.

Под действием тактовых импульсов (1 (1) с частотой 1 содержимое

A(t) первого регистра возрастает с каждым тактом на величину А, задаваемую этим числом на кодовом входе регистра. Аналогичным образом действует второй накопительный регистр, формируя функцию S(t), возрастающую на величину В всякий раз при поступлении на его тактовый вход импульсов последовательности сРд (t) с часто- . той f< . На цифровом сумматоре суммируются переменные коды A(t) и 8(t)

1 снимаемые соответственно с инверсных выходов первого и второго регист- ра, чем обеспечивается вычитание функций A(t) и 8(t) на выходе сумматора.

С помощью ЦАП разность кодов C(t) преобразовывается в аналоговую величйну и поступает на выход устройства.

При условии, что 1 8=1 А значение постоянной составляющей на выходе не зависит от времени и определяется эквивалентной разностью фаз импульсных последовательностей дА(Т) и dg(t). Статическая (при

"a S у 0) погрешность детектирования определяется лишь точностью ЦАП, так как погрешность, подаваемая цифровым сумматором в этом случае, рав" на нулю. Высокая статическая точность детектирования (десятиразрядный ЦАП, например, имеет погрешность « 10.>) является важным достоинством этого устройства по сравнению с известными13

Однако возможности устройства по быстродействию ограничены задержками операций поразрядного суммирования и переносов результатов суммирования из разряда в разряд в цифровом сумматоре. Задержки оказываются значительными, так как на практике А и

В многоразрядные двоичные числа (до 12 и более разрядов). Из-за задержек результирующий процесс C(t) на выходе сумматора воспроизводится с погрешностью, заключающейся как в поразрядных искажениях логических уровней "О" и "1", так и в более крупных ошибках, выражающихся в

"выпадании" ступеней величиной А и

50 В из результата суммирования. Дннамическая точность детектирования оказывается удовлетворительной (приближающейся к статической) при входных частотах по крайней мере на по I рядок меньших предельной рабочей час. тоты цифрового сумматора, из-за чего использование этого устройства на практике весьма неэффективно.

Цель изобретения — расширение функциональных возможностеи.

Указанная цель достигается тем,, что в устройство, содержащее цифроаналоговый преобразователь и два накопительных регистра, тактовые и кодовые входы которых подключены соответственно к импульсным и числовым входам устройства, введены триггер и дополнительный старший разряд цифроаналогового преобразователя, подключенный к выходу триггера, входы которого соединены с выходами импульсов переполнения накопительных регистров, разрядные выходы которых попарно подключены к разрядным входам цифроаналогового преобразователя.

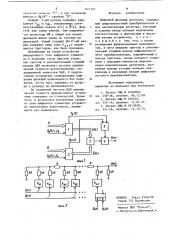

На фиг. l показана схема предла гаемого устройства; на фиг. 2 — пример выполнения суммирующего ЦАП.

Устройство содержит накопительные регистры 1 и 2, цифроаналоговый преобразователь (ЦАП) 3, дополнительный старший разряд ЦАП 4, триггер 5.

Схема работает следующим образом.

Переменные коды A(t) и 8(t) с выходов накопительных регистров I и 2 поступают на входы цифроаналогового преобразователя 3, в котором осуществляется поразрядное (без переносов) суммирование и преобразование кодов.

Для устранения скачкообразных приращений выходного аналогового процесса в моменты переполнений регистров, в

ЦАП введен дополнительный старший разряд, подключенный к выходу триггера

5. Триггер управляется импульсами переполнения Pg(t)и P (t) соответствующих регистров 1 и 2. В момент переполнения накопительного регистра 1 код A(t) уменьшается на величину Q, равную емкости регистров, а при переполнении регистра 2 код В(1) увеличивается на ту же самую величину, Так как вес введенного старшего разряда

ЦАП соответствует величине Q,, для устранения упомянутых скачков достаточно лишь выбрать полярность включения . триггера такой, чтобы при появлении импульса Рд(4) он передавал на ЦАП лоФормула изобретения

Цифровой фазовый детектор, содержащий цифроаналоговый преобразователь и два накопительных регистра, тактовые и кодовые входы которых подключены соответственно к импульсным и числовым входам устройства, о т л и— ч а ю щ и " с я тем, что, с целью расширения функциональных возможностей, в него введены триггер и дополнительный старший разряд цифроаналогового преобразователя, подключенный к выходу триггера, входы которого соединены с выходами импульсов переполнения накопительных регистров, разрядные выходы которых попарно подключены к разрядным входам цифроаналогового преобразователя.

Источники информации, принятые во внимание при экспертизе

l. Патент США - 2490500, кл. 250-36, опублик. 06.12.49.

2. Патент США - 355446, кл. 331-16, опублик. 12.01.71.

3. Патент США Ф 3913028, .кл. 331-1А, опублик. 14.10.75.

° Ф

НИИПИ Заказ 9326/70

Тираж 735 Подписное

° ° фиг. Г

6И s(

5 875303 гический уровень "1", а при появлении импульса ф (+.) — уровень "0", Каждый 1-ый разряд содержит пару ключей Кд; и Кр„, управляемых соответствующйми кодами А(t) и В(t). .Все- s го К пар таких ключей. Они подключа ют резисторы 49,к общей или потен" циальной щинам (шины на чертеже не показаны). Самый старший (К+1) †.ый разряд содержит один ключ К 1,+ и управляется триггером, как было пояснено.

Исключение из схемы устройства инерционного узла цифрового сумматора и введение таких простых узлов, как триггер и дополнительный старший 15 разряд ЦАП позволяет достичь динамической точности детектирования, определяемой точностью ЦАП. В предлагаемом устройстве суммирование цифровых функций производится без пере- 20 носов, из-за чего задержка от разряда к разряду не накапливается.

До граничной частоты ЦАП динамическая точность предлагаемого устройства совпадает со статической. Кроме 25 того, в результате исключения сложного узла цифрового сумматора устройство значительно упростилось, надежность его повысилась.

Филиал ППП "Патент", г.ужгород,vn,Проектная,4