Измеритель симметричных составляющих напряжений в трехфазной промышленной сети

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

О П И С А Н И Е ю1875309

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61 ) Дополнительное к авт. свид-ву (22) Заявлено 20. 02. 80 (21) 2889244/ }8-21 с присоединением заявки № (23) Приоритет— (5! )М. Кл.

G 0I и 29/04

Ibeyaapnsonefi кем«тет

СССР ае делам «эебретен«« и вткрит«}}

Опубликовано 23. 1 О. 8l ° Бюллетень ¹ 39

Дата опубликования описания 25.}0.81 (53) УДК 621.317..319(088.8) " а д,.

Л.М. Буняк, Л.Н. Лупенко и А.А. Елизаров

j .Р (72) Авторы изобретения (7}) заявители (54) ИЗМЕРИТЕЛЬ СИММЕТРИЧНЫХ СОСТАВЛЯЮЩИХ НАПРЯЖЕНИЙ

В ТРЕХФАЗНОЙ ПРОМЫШЛЕННОЙ СЕТИ

Изобретение относится к электротехнике и электроизмерениям и может . быть использовано для выделения напряжений прямой, обратной и нулевой по-.

- следовательностей в трехфазной сети, например, для расчета несимметричных режимов, определения коэффициентов несимметрии и неуравновешенности на.; пряжений.

Известен измеритель симметричных составляющих напряжений в трехфазной сети, содержащий последовательно соединенные частотно-избирательный, фильтр и вольтметр переменного тока, а также трансформаторный преобразо15 ватель, двухполупериодный выпрямитель, конденсатор и фильтр боковой . частоты t I ).

Недостаток этого устройства — ограниченная точность измерения.

Наиболее близким к изобретению является устройство, содержащее масштабный преобразователь, входы которого соединены с шинами фазис напряжений, а выходы подключены к входам коммутатора, вход управления которого соединен с одним нз выходов блока управления, выход коммутатора соединен с первым входом блока управления непосредственно, а с входом формирователя импульсов через фильтр нижних частот, управляемый фазоврагщатель и регистратор 1 2}.

Недостаток этого измерителя — низкая точность работы.

Цель изобретения — повышение точ, ности.

С этой целью в измеритель симмет- ричных составляющих напряжений в трехфазной промышленной сети, содержащий масштабный преобразователь, входы которого соединены с шинами фазных напряжений, а выходы подключены к входам первого коммутатора, вход управления которого соединен с одним из выходов блока управления, выход первого коммутатора соединен с первым входом блока управления непосредст87 венно, а с входом формирователя импульсов через фильтр нижних частот, управляемый фазовращатель и регистратор, вход управления которого соединен со вторым выходом блока управления, введены второй коммутатор, включенный между выходами формирователя импульсов и входом управляемого фазовращателя, фазосдвигатель, два умножителя частоты, два интегратора, два элемента памяти и амплитудный компаратор, один выход которого соединен с входом управления управляемого фазовращателя, а второй — с одним входом регистратора, два других входа кото4 рого соединены с выходами элементов памяти, первые входы которых подключены к третьему выходу блока управления, причем второй вход одного элемента памяти подключен к одному выходу управляемого фазовращателя. непосредственно, а второй вход второго элемента памяти соединен со вторым выходом управляемого фазовращателя через последовательно включенные интегратор и первый умножитель частоты, вход амплитудного компаратора подключен через последовательно соединенные второй интегратор, второй умножитель частоты и фазосдвигатель ко второму выходу управляемого фазовращателя, вторые входы первого и второго умножителей частоты подключены к первому входу блока управления, а вторые входы интеграторов подключены к четвертому выходу блока управления, второй вход которого. соединен с одним из выходов формирователя импульсов.

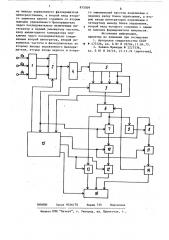

На чертеже представлена структурная электрическая схема устройства.

Устройство состоит из масштабного преобразователя 1, компараторов

2 и 3, низкочастотного избирательного фильтра 4, формирователя 5 импульсов, фазовращателя 6 управляемого, умножителей 7 и 8 частоты, фазосдвигателя 9, интеграторов 10 и 11, эле- ментов 12 и 13 памяти, амплитудного компаратора 14, блока 15 управления и регистратора 16.

Устройство работает следующим образом.

Трехфазное напряжение промышленной сети через масштабный преобразователь

1 поступает на коммутатор 2, который под воздействием блока 15 управления коммутирует последовательно во времени фазы А, В и С.

5309 ф

Выходной сигнал коммутатора 2, со ответствующий выбранной фазе поступает на низкочастотный избирательный фильтр 4, который служит для выделения

5 первой гармоники периодического сигнала.

Выделенное синусоидальное напряжение с частотой первой гармоники поступает на формирователь 5, который служит для создания сетки опорных час10 тот, кратных частоте первой гармоники, причем количество частот формирователя, их номера соответствуют требуемому количеству и номерам гармоник, выделяемых из напряжения сети.

40

Время интегрирования определяется блоком 15 управления, куда поступает входное напряжение. После окончания времени интегрирования выходной сигнал интегратора 10 равен синусной

45 ортогональной составляющей гармоники

А, анализируемой в данном цикле, т.е. 4 = A = — U(a)win К1Ю.ЬМ, soli(интщ < Т о

50 где Т вЂ” период входного напряжения

Выходной сигнал интегратора 10 по команде от блока 15 управления записывается в аналоговом элементе 12 памяти; одновременно с этим значение

55 фазового сдвига, установленное на фазовращателе 6 в этот момент, записывается по команде от блока 15 уп,равления в элемент !3 памяти.

Сигналы опорных частот поступают на коммутатор 3, который под воздействием блока 15 управления выбирает требуемый номер гармоники (опорной частоты ), которая затем поступает ца фазовращатель 6.

В исходном состоянии угол сдвига фазы фазовращателя 6 равен нулю. Выходной сигнал фазовращателя 6 поступает на умножитель 7 и через фазой сдвигатель 9, обеспечивающий сдвиг фазы на 90, на умножитель 8.

Умножитель 7 и интегратор 10 входят в состав формирователя синусной зо составляющей k-ой гармоники входного соответствующего напряжения, а умножитель 8 и интегратор 11 — в состав формирователя косинусной составляющей.

На входы умножителей 7 и 8 подается также напряжение выбранной фазы

U(t). Выходной сигнал умножителя 7 интегрируется интегратором 10 в течение времени, равного периоду первой гармоники входного напряжения.

75.309

15

25

5 8

:!

Работа умножителя 8 и интегратора

11 происходит аналогично. При том выходной сигнал интегратора ll равен косинусной ортогональной составляющей гармоники В)„ анализируемой в данном цикле, т. е ) выл .. к=т1®cosKet84 И о

Выходнои сигнал интегратора 11 поступает на амплитудный компаратор )4.

В том случае, если косинусная ортогональная составляющая В равна ну.лю, значение амплитуды С„ анализируемой гармоники равно синусной ортогональной составляющей Ак.

Это возможно только в случае, если начальный фазовый сдвиг k-ой гармоники бравен нулю.

Для получения нулевого фазового сдвига Vg служит фазовращатель 6. В случае, если ВКУСО,амппитудный компаратор )4 управляет фазовращателем 6 до тех пор, пока косинусная ортогональная составляющая В не станет миник мальной. При этом в фазовращателе 6 окажется установленным значение фазового сдвига равное начальному сдвигу фазы k-ой анализируемой гармоники.

Ввиду того, что интеграторы 10.и

1) работают циклически (время интегрирования равно периоду исследуемого сигнала), значение сдвига .фазы фазовращателя изменяется дискретно, поэтому в обшем случае величина В), косинусной ортогональной составляющей может быть не равной нулю, но близкой к нулевому значению. Амплитудный компаратор !4 фиксирует момент минимума косинусной ортогональной. составляющей и выдает сигнал на запись амплитудного значения и начального фазового сдвига анализируемой гармоники. При этом сигналы с выхода элемента 12 памяти, равные амплитуде гармоники, и с выхода фазо.вращателя 6, равные начальному фазорому сдвигу, регистрируются регйстрагором 16.

Блок 15 управления в это время выдает регистратору номер гармоники и к какой фазе промышленной сети от- . носится данная анализируемая гармоника.

Блок 15 управления определяет алгоритм работы всех узлов устройства, а именно: определяет порядок коммутации фазных напряжений сети, выдавая соответствующие управляющие сигналы на коммутатор 2; управляет последоЪ вательным выбором опорных частот,соответствующих анализируемому номеру гармоники, с помощью коммутатора

3; определяет период напряжения выбранной сети и задает время интегриро-. вания интеграторам 10 и ll, равное этому периоду; управляет элементами

)2 и 13 памяти, записывая в них пос" ле окончания каждого цикла интегриро- вания текущего значения модуля синусной составляющей гармоники и сдвига фазы, установленного в фазовращателе б; выдает регистратору )6 текущее значейие номера анализируемой гармоники и порядок коммутации фазы промышленной сети (А, В или С), подключенной к устройству.

Работа всего устройства синхронизируется с частотой исследуемого напряжения. Для этого на блок 15 управления с формирователя 5 частоты поступает синхронизирующий сигнал самой высокой опорной частоты, который синхронизирует работу устройства управления.

Формула изобретения

Измеритель симметричных составляющих напряжений в трехфазной промышленной сети, содержащий масштабный преобразователь, входы которого соединены с шинами фазных напряжений, а выходы подключены к входам первого коммутатора, вход управления которого соединен с одним из выходов блока управления, выход первого коммутатора соединен с первым входом блока управления непосредственно, а с входом формирователя импульсов через фильтр ниж них частот, управляемый фазовращатель и регистратор, вход управления которого соединен со вторым выходом блока управления, о т л и ч. а ю шийся тем, что, с целью повышения точности, в него введены второй коммутатор, включенный между выходами формирователя импульсов и входом управляемого фазовращателя, фазосдвигатель, два умножителя частоты, два интегратора, два элемента памяти и амплитудный компаратор, один выход которого соединен с входом управления управляемого фазовращателя, а второй — с одним входом: регистратора, два других входа которого соединены с выходами элементов памяти, первые входы которых подключены к третьему выходу блока управления, причем второй вход одного элемента памяти подключен к одно7 875309 8 му выходу управляемого фазовращателя го умножителей частоты подключены к

I непосредственно, а второй вход второ- первому входу блока управления, а втого элемента памяти соединен со вторым рые входы интеграторов подключены к выходом управляемого фазовращателя четвертому выходу блока управления, через последовательно включенные ин- второй вход которого соединен с одним тегратор и первый умножитель частоты, из выходов формирователя импульсов. вход амплитудного компаратора под- Источники информации, ключен через последовательно соеди- принятые во внимание при экспертизе ненные второй интегратор, второй ум- 1. Авторское свидетельство СССР ножитель частоты и фазосдвигатель ко 1о 11 473126, кл. G 01 R 29/04, 17.04.73. второму выходу управляемого фазовра- : 2. Заявка Франции Ф 2227536, щателя, вторые входы первого и второ- кл. G 01 R 29/16, 27.12.74 (прототип), ВНИИПИ Заказ 9326/70 Тираж 735 Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 ..