Устройство логического и допускового контроля

Иллюстрации

Показать всеРеферат

О ll И С А Н И Е 875313

Союз Соввтсннк

Соцнапнстнчвснна

Рвс ублнн

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДИТИЗЬСТВУ (61) Дополнительное к авт. синд-sy (5 )М. Кл, Q 01K 31/28 (22) Заявлено 20.02.80(23) 2886632/18-21 с присоединением заявки М

9вударстюивй квинтет

СССР ее дами веевретеввв в етеунтвв

Я 06 F 11/00 (23 ) П рнорнтет

Опубликовано 23.10.81. Бюллетень М39

Дата опубликования описания 25.10.81. (53) УДК 621 374.32 (088.8) у

Л. A. Иванов

". Ъф .".1".,, ; т ф ;."г, : „..

Специальное конструкторское бюро систем омьйцтэпкрй ;,".; автоматики (72) Автор изобретения (7l ) Заявнтеяь (54) УСТРОЙСТВО ЛОГИЧЕСКОГО И ДОПУСКОВОГО

КОНТРОЛЯ

Изобретение отнк:ится к технической диагностике и может быть использовано в устройствах дня проверки логических .схем

Известно устройство логического и допускового контроля, содержащее блок кон- > троля уровней, преобразователь уровней и цифровой компаратор 1

Недостатком известного устройства является его относительная сложность.

Известно также устройство логического 10 и допускового контроля, содержащее .две входные шины, элемент неравнозначности, два аналоговых компаратора, элемент

ИЛИ, первая входная шина соедийена е первым входом элемента неравнозначнос15 ти и с первыми входами аналоговых компараторов Г2 .

Недостатком известного устройства является его относительная сложность, что приводит к уменьшению надежности.

Цель изобретения - повышение иадеж ности.

Поставленная цель достигается тем, что в устройство логического и допуско вого контроля, содержащее две входные шины, элемент неравнозначности и аналоговый компаратор, первый вход которого соединен с первой входной шиной, введены два элемента HE и два резистора, вторая входная шина .соединена со входом первого элемента НЕ, выход которого соединен через первый резистор со вторым входом аналового компаратора и соединен со входом второго элемента КЕ, выход которого соединен с первым входом элемента неравнозначности и через второй резистор- со вторым входом аналового компаратора, выход которого соединен со вторым входом элемента неравнозначности.

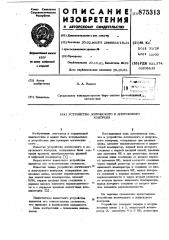

На чертеже схематично представлено устройство логического и допускового контроля.

Устройство содержит первую и вторую входные шины 1 и 2, аналоговый компаратор 3, .элементы 4 и 5 НЕ, резисторы

875313

6 и 7, элемент 8 неравнозначности и входную шину 9.

Входная шина 1 соединена с первым входом аналового компаратора З,,входная шина 2 соединена со входом элемента 4 НЕ, выход которого соединен через резистор 6 со вторым входом аналового компаратора 3 и соединен со входом элемента 5 НЕ, выход которого соединен с первым входом элемента 8 неравнозначности и соединен через резистор 7 со вторым входом аналового компаратора 3, выход которого соединен.со вторым входом элемента 8 неравнозначности, выход которого соединен с выходной шиной 9. устройство предназначено преимущест- венно для проверки логических схем с высокоомными входами и низкоомными выходами, например К/МОП - микросхем, и логических блоков, выполненных на таких, микросхемах, поэтому для определенности будем рассматривать работу схемы сравнения при подключении к ее входным шинам 1 и 2 выводов К/МОП - микросхем.

Устройство работает следующим образом.

На шину 1 подается логический сигнал с выхода проверяемой микросхемы, а на шину 2 — с одноименного выхода эталонной (заведомо исправной) микросхемы того же типа, что и проверяемая микросхема, причем предполагается, что на эти микросхемы поданы совпадающие наборы воздействий (логических сигналов), номинальные выходные напряжения этих микросхем соответствуют номинальным напряжениям логических уровней входного сигнала элемента 4 НЕ, а проверяемая, эталонная микросхема, элементы НЕ и элемент 8 неравнозначности подключены к общим шинам питания.

Характерным дпя К/ХОП-микросхем является то, что установленные техническими условиями допускаемые отклоне ния напряжений выходных уровней О и

1 от их номинальийх значений, принятых равными напряжениям на общей шине и на шине питания соответственно, по абсолютной величине совпадают. Номиналь ные сопротивления резисторов 6 и 7 выбраны такими, что они удовлетворяют со-отношению а а 3

Е где Я Д; «номинальные сопротивлений

41 резисторов 6 и 7 соответственн01

Я - номинальное значение напряжения на шине питания;

g - абсолютная величина установ ленного техническими условиями на проверяемую микросхему допускаемого отклонения напряжений выходных уровней от их номинальных значений.

Поскольку эталонная микросхема считается исправной, то сигнап на шине 2 всегда принимает значение либо «О", лиt0 бо "1 и приводит в соответствующее действие элемент 4 HE.

При сигнале О на шине 2 на выходах элементов 4 и 5 НЕ имеют место сигналы 1 и "О" соответственно с наts пряжениями, почти точно равными нулю и

Есоответственно,,при этом на инвертирующий вход компаратора 3 с точки соединения резисторов 6 и 7 поступает напряжение, почти точно равное д . Если напряжение на шине 1 не привышает величины 4, т.е. находится в пределах, допустимых для напряжения логйческого

О, то на выходе компаратора 3 имеет место логический сигнал "О, при этом на обоих входах элемента 8 неравнозначности имеют место одинаковые логические сигналы О, поэтому он формирует на выходе 9 логический сигнал О, в противном случае - логический сигнал

Зо

При сигнале "1 на шине 2 на выходах элементов 4 и 5 НЕ имеют место сигналы "0» и 1" соответственно с напряжениями, почти точно равными Е и зз нулю соответственно, при этом на инвертируюший вход компаратора 3 с точки . соединения резисторов 6 и 7 поступает напряжение, почти точно равное (Е-д).

Если напряжение на шине 1 превышает

40 величину (Е-д), т.е. находится в преде- . лах, допустимых дпя напряжения логической "1", то на выходе компаратора 3 имеет место логический сигнал 1, при . этом на обоих входах элемента 8 неравнозначности имеют место одинаковые ло4 гические сигналы "1"., поэтому он формирует на выходе 9 логический сигнал

О", в противном случае - логический сигнал 1

Таким образом, при обоих значениях логического сигнала на шине 2 устройство формирует на шине 9 логический сигнал "О при соответствии, сигнала на шине 1 сигналу на шине 2 но логическому значению и соответствии напряжения на шине 1 заданным допускам и логический сигнал 1 - нри несоответствии сигнала на шине 1 сигналу на.„шине 2 по логическому значению или при несоответствии sa5 8753 пряжения на шине 1 заданным допускам, т.е. устройство осуществляет логический и цопусковыйконтроль, при меньшем ко- . личестве используемых конструктивных признаков, что повышает надежность пред лагаемого устройства.

Формула изобретения

to

Устройство логического и aottyczosoro контроля, содержащее две входные шины, элемент неравнозначности и аналоговый компаратор, первый вход которого соединен с первой входной шиной, о т л и ч а - 5 ю ta е е с я тем, что, с целью повышения надежности, в него введены два эле мента НЕ и два резистора, вторая вход-, ная шина соедин на со входом первого элемента НЕ, выход которого соединен через первый резистор со вторым входом аналогового компарвтора и соединен со. входом второго элемента НЕ, выход кото-. рого соединен с первым входом элемента неравнозначности и через второй резисторсо вторым входом аналового компаратора, . выход которого соединен со вторым входом элемента неравнозначности.

Источники инфорамции, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 451994, ил. Я 06 11/00, 1973.

2. Вердиш Э. С. и др. Автоматическая установка для контроля.цифровых схем в процессе производства. - "Приборы и системы ущравления, 1975. No 2, (прототип).

Составитель Ранов

Редактор Г. Волкова Текред Ж.Кастелевич корректор

Заказ 9327/71 Тираж 735 Подписное

ВНИИПИ Гжударствеиного комитета СССР по делам изобретений и открытий

113035, Mocha, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г, Ужгород, ул. Проектная, 4