Устройство для сопряжения

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОИЖОМУ С ТВЛЬСТВУ

CoIo3 Севетскнк

Соцналнстнческнк

Республик (61) Дополнительное к авт. саид-ву (22) Заявлено 220380 (21) 2889809/18-24 (51) М. КЛ. с присоединением заявки йо (23) Приоритет

G 06 F 3/04

ГосударстаенямЯ комитет

С.СС Р яо делам нзобретениЯ я открытмЯ

Опубликовано 231 а81. бюллетень Н9 39

Дата опубликования описания 231 Q81 (53) УДК 681. 325 (088.8) (72) Авторы изобретения

A.Â.Èöêîâè÷, А.С.Когутенко и А;Е.Мерзляк (71) Заявитель (54) УСТРОЯСТВО ДЗЩ СОПРЯЖЕНИЯ

Изобретение относится к вычислительной технике и может быть использовано для сопряжения синхронного источника с асинхронным приемником, в частности для связи устройства циклического опроса датчиков с .устройством вывода информации.

Известно устройство для обмена информацией, содержащее буферный накопительный блок, дешифратор адреса, регистр числа, регистры текущих адресов и регистр начального адреса (1 .

Недостатком этого устройства являются большие аппаратурные затраты из-за необходимости большого числа регистров текущих адресов, требующихся для осуществления произвольного порядка записи и выборки информации.

Наиболее близким по технической сущности к предлагаемому является устройство для сопряжения, содержащее буферный запоминающий регистр, дешифратор, маркерный регистр, триггер, первый и второй элементы задержки, первый и второй вентили, элемент ИЛИ-НЕ, формирователь импульса f2) .

Недостаток известного устройства. состоит в ограниченных функциональных возможностях, что не позволяет осуществлять выборку информации по адресу из основного запоминающего

5 устройства (ЗУ).

Цель изобретения — расширение функциональных воэможностей за счет обеспечения возможности вывода информации по заданному адресу.

Поставленная цель достигается тем, что в устройство, содержащее буферный запоминающий блок, регистр, первый триггер, элемент задержки, элемент И, формирователь импульса и дешифратор, причем информационные вход и.выход буферного запоминающего блока являются соответственно информационными входом и выходом устройства, введены синхронизатор, счет.чик, второй триггер, схема сравнения, 2О сувеаатор по модулю два, элемент

И-ИЛИ-и два элемента ИЛИ, причем первый вход дешифратора соединен с первыми входами первого и второго триггеров, формирователя импульса, элемента Й и первым входом устройства, первый вход схемы сравнения соединен со вторыми входом устройства, первый выход первого триггера подКлючен ко второму входу формироватеЗО пя импульса, выход которого подключен

875374

65 к первому входу элемента И-ИЛИ и через элемент задержки к первому входу первого элемента ИЛИ, выход которого соединен со вторым входом второго триггера, а второй вход — co вторым входом схемы сравнения и выходом элемента И, второй вход которого подключен ко второму выходу первого триггера, второй вход которого соединен с выходом дешифратора и со вторым входом элемента И-ИЛИ, подключенного третьим входом к выходу схемы сравнения, третий вход схемы сравнения соединен с первым выходом синхронизатора, выход — с первым . входом регистра и первым управляющим нходом буферного запоминающего блока, второй выход синхронизатора подключен к четвертому входу элемента

И-ИЛИ, третий выход синхронизатора соединен со вторым управляющим входом буферного запоминающего блока, выход элемента И-ИЛИ подключен к первому входу счетчика, второй вход которого подключен к выходу второго элемента ИЛИ, а выход — ко вторым входам дешифратора и регистра и к первому входу сумматора по модулю два, выход которого подключен к адресному входу буферного запоминающего блока, второй вход сумматора по модулю два соединен с третьими входами второго триггера и дешифратора, первьм входом второго элемента ИЛИ и первым выходом регистра, второй выход которого подключен ко второму входу второго элемента ИЛИ, выход второго триггера является выходом устройства.

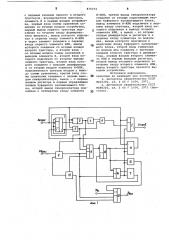

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 — временная диаграмма.

Устройство содержит первый 1 и второй 2 триглзры, формирователь 3 импульса, элемент 4 задержки, элемент И 5, первый б и второй, элементы ИЛИ, схему 8 сравнения, элемент И-ИЛИ 9, счетчик 10, дешифратор

11, сумматор 12 (по модулю 2), синхронизатор 13, регистр 14 и буферный запоминающий блок 15. . Устройство работает следующим образом.

Триггер 1 находится в состоянии

"0". Потенциал запроса через элемент

И 5 поступает на управляющий вход схемы сравнения 8. На первый вход схемы сравнения подан адрес зоны, информация из которой должна быть выведена, на второй — адрес зоны, информация иэ которой обрабатывается в данный момент. При равенстве кодов на входах на выходе схемы сравнения формируется потенциал, разрешающий запись "1" в первый разряд регистра 14 (режим записи), деблокировку счетчика 10 через элемент

ИЛИ 7, подачу импульсов смены адреса на счетчик 10 и импульсов запи5 !

О

40 си †. на вход буферного запоминающего блока 15.

Последний импульс смены адреса при выборке сбросит счетчик 10 в "0".

При этом "1" продвинется во второй разряд регистра 14 (режим выдачи информации), на входы сумматора 12 подаются "1", на адресный вход буферного запоминающего блока 15 подается инверсный код счетчика, устанавливая на выходе устройства информацию, хранившуюся в последней ячейке считанной эоны. Триггер 2 устанавливается в "0", формируя на выходе строб сопровождения.

При снятии сигнала запроса триггер

1 устанавливается в "1" и самоблокируется, дальнейшие изменения потенциала на этом входе не вызовут изменения его состояния. Триггер 2 устанавливается в "1", снимая сигнал строба. Следукщий импульс запроса поступает на вход формирователя 3, импульс с выхода которого через элемент И-ИЛИ 9 поступает на вход счетчика 10, увеличивая адрес на "1" и через элемент 4 задержки и элемент

ИЛИ 6 — на вход триггера 2, устанавливая строб.

Каждый последующий сигнал запроса увеличивает код счетчика 10 на единицу, уменьшая на единицу адрес буферного запоминающего блока, и затем формирует строб. После снятия последнего импульса запроса дешифратора 11 подает через элемент И-ИЛИ 9 импульс на счетчик 10, сбрасывая его в "0" и устанавливает в "0" первый триггер, подготавливая устройство к выдаче информации из другой зоны.

Таким образом, предлагаемое устройство позволяет обеспечить простое сопряжение синхронного источника с асинхронным приемником при возможности выбора информации из произвольной зоны, адрес которой определяется внешним кодом.

Формула изобретения

Устройство для сопряжения, содержащее буферный запоминающий блок, регистр, первый триггер, элемент задержки, элемент И, формирователь им пульса и дешифратор, причем информационные вход и выход буферного запоминающего блока являются соответственно информационными входом и выходом устройства, о,т л и ч а ю щ е ес я тем, что, с целью расширения функциональных воэможностей устройства за счет обеспечения возможности вывода информации по заданному адресу, в него введены синхронизатор, счетчик, второй триггер, схема сравнения, сумматор по модулю два, элемент И-ИЛИ и два элемента ИЛИ, причем первый вход дешифратора соединен

875374 I, с первыми входами первого и второго триггеров, формирователя импульса, элемента И и первым входом устройства, первый вход схемы сравнения соединен со вторым входом устройства, первый выход первого триггера подключен ко второму входу формирователя импульса, выход которого подключен к первому входу элемента И-ИЛИ и через элемент задержки к первому входу первого элемента ИЛИ, выход которого соединен со вторым входом второго триггера, а второй вход со вторым входом схемы сравнения и выходом элемента И, второй вход которого подключен ко второму выходу первого триггера, второй вход которого соединен с выходом дешифратора и со вторым входом элемента И-ИЛИ, подключенного третьим входом к выходу схемы сравнения, третий вход схемы сравнения соединен с первым выхо- 20 дом синхронизатора, выход — с первым . входом регистра и первым управляющим входом буферного запоминающего блока, второй выход синхронизатора подключен к четвертому входу элемента

И-ИЛИ, третий выход синхронизатора соединен со вторым управляющим входом буферного запоминающего блока, выход элемента И-ИЛИ подключен к первому входу счетчика, второй вход которого подключен к выходу второго элемента ИЛИ, а выход — ко вторым входам дешифратора и регистра и к первому входу сумматора по модулю ° два, выход которого подключен к адресному входу буферного запоминающего блока, второй вход сумматора по модулю два соединен с третьими входами второго триггера и дешифратора, первым входом второго элемента ИЛИ и первым выходом регистра, второй выход которого подключен ко второму входу второго элемента ИЛИ, выход второго триггера является выходом устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9410392, кл. G 06 F 3/04, 1971.

2. Авторское свидетельство СССР

9488202, кл. G 06 F 3/04, 1973 (прототип).

875374

chic

Вбр сТ (с)

° °

Запись .ЕК

Составитель В.Вертлиб

Техред С.Мигунова Корректор М.демчик

Редактор Г.Волкова

Эакаэ 9335/74 Тираж 748 Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений н открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП "Патент", г. Ужгород, ул. Проектная, 4