Аналого-дискретное интегрирующее устройство

Иллюстрации

Показать всеРеферат

875407

Союз Советсиик

Социалистические

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l ) Дополмительмое к авт. свид-ву (22) Запвлемо 13.11. 79 (21) 2837896/18-24

l с присоедииеммем заявки,ле (23) Приоритет

Опублмковамо 23. 10.81. Ьюллетемь Аа 39

Дата опублмковаммя описамия 25. 10.81 (Ы)М. Кл.

G 06 J 3/00

G 06 G 7/186

1 тпвулерптеаеый кемитет

CCCP ве делает кэебретеккй н етйрмткй (5З) УДК 681, .34 (088.8Р

Г» И. Грездов, Ю. П. Космач и Г. А. Лоб к"

Р (72) @вторн изобретеммя

4, г та" Опытное. конструкторско-технологическое бюро металлофиэики АН Украинской CCP и институт электродинамики AH Украинской CCP (73) . Заявители (54) АНАЛОГО-ДИСКРЕТНОЕ ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО

"8 П- "Pq +>""Selх1

Изобретение относится к вычислительной технике и предназначено для использования в гибридных вычиСли-. тельных устройствах для длительного быстрого и точного интегрирования про" извольно меняющихся аналоговых напря.-.

S жений.

Известны аналого-дискретные интегрирующие Устройства, используемте для длительного интегрирования сиг10 налов, которые содержат аналоговый интегратор, компараторы, преобразователь полярности входного сигнала, аналоговые ключи и счетчик для накопления интеграла (1 2 Однако такие

1S устройства имеют ограниченное применение так как обеспечивают возможность интегрирования знакопостоянного аналогового напряжения.

Наиболее близким к предлагаемому техническим решением является аналого-дискретное интегрирующее устройство, содержащее блок преобразования полярности входного сигнала, аналоговый интегратор, компараторы и цифровой блок (2 ).

Однако известное устройство осуществляет точное интегрирование сигналов только большой длительности.

Это обусловлено тем, что элементы петли обратной связи (компаратор, цифровой блок, блок преобразования входного сигнала) вносят суммарную временную задержку, Наличие ее приводит к тому, что после достижения выходным напряжением аналогового интегратора порогового уровня управляющий сигнал по петле обратной связи изменяет, знак подыинтегральной функции с задержкой t> и значение выходного напряжения аналогового интегратора в этот момент составит где А0п -„ напряжение аналогового ин-, ВЬ|Х тегратора, превьппающее шкалу интегратора.

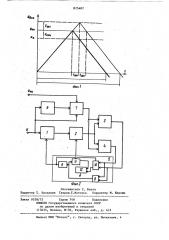

7 ному входу и входу опорного напряжения устройства, управляющий вход соединен с выходом блока 6 определения полярности, а выход подключен ко вторым входам компараторов 3 и 4.

Цифровой блок 5 состоит из элемента ИЛИ 8, входы которого являются входами цифрового блока, управляющего триггера 9, вход которого подключен к выходу элемента ИЛИ 8, а выход яв" ляется первым выходом цифрового блока

5 и соединен со входом блока 10 определения направления счета, форми" рователь 11 счетных импульсов, подключенный к счетному входу счетчика

12, выход которого является выходом устройства

Устройство работает следующим об ); азом.

Входной сигнал, например U>0, поступает через блок 1 преобразования полярности входного сигнала на вход аналогового интегратора 2 первоначально со своим знаком. Как только напряжение на выходе интегратора, имеющее положительное приращение интеграла, достигнет положительного порогового уровня, срабатывает компаратор 3, который через цифровой блок 5 изменяет знак подынтегральной функции на выходе блока 1. Это изменяет знак приращения интеграла на выходе интегратора 2, выходное напряжение стремится к отрицательному пороговому уровню, при достижении которого срабатывает компаратор 4, что вызывает очередное изменение подынтегральной функции через блоки 5 и 1, а следовательно, и,знак приращения интеграла, и выходное напряжение стремится к положительному пороговому уровню. Таким образом, при знакопостоянном входном сигнале компараторы срабатывают стро-. го поочередно. Если же в какой-либо момент входная величина изменит свой знак, изменится и знак приращения интеграла на выходе интегратора 2. В .этом случае один из компараторов срабатывает дважды подряд. Цифровой блак

5, используя эту информацию, накапливает результат интегрирования после каждого очередного срабатывания компаратора при условии, если происходит изменение знака приращения интеграла на выходе аналогового интегратора (это возникает, когда входная величина отсутствует .или соизмерима е дрейфом нуля интегратора), накопление результата интегрирования не про

3 87540

Цель изобретения — повышение точности интегрирования и быстродействия устройства.

Поставленная цель достигается тем, что в аналого-дискретное интегрирующее устройство, содержащее последовательно .соединенные блок преобразования полярности входного сигнала и аналоговый интегратор, выход которого подключен к первым входам компараторов, элемент ИЛИ, входы которого и входы блока определения направления счета. соединены с выходами компараторов, выход элемента ИЛИ через управляющий триггер подключен к уп35 . равляющим входам блока преобразования полярности входного сигнала и блока определения направления счета и через формирователь счетных импульсов к.управляющему входу интегратора и счетному входу счетчика, вход задания направления счета которого соединен с выходом блока определения направления счета, введены блок определения полярности входного сигнала и блок формирования порогового уровня, входы которого соединены соответственно с сигнальным входом и входом опорного напряжения устройства, выход подключен ко вторым входам компа30 раторов, а управляющий вход связан с выходом блока определения полярности входного сигнала, входом соединенного с сигнальным входом устройства.

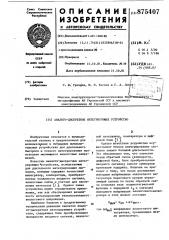

На фиг. 1 показан график напряжений на выходе интегратора до и после компенсации; на фиг.2 — структурная схема аналого-дискретного интегрирующего устройства.

Устройство содержит блок 1 пре-.

40 образования полярности входного сигнала, вход которого подключен к сигнальному входу устройства, а выход соединен. со входом аналогового интег. ратора 2, компараторы 3 и 4, первые входы которых подключены к выходу аналогового интегратора 2, а выходы к цифровому блоку 5, первый выход которого подключен к управляющему вхо ду блока 1 преобразования полярности so входного сигнала, а второй — соединен с управляющим входом аналогового интегратора 2, блок 6 определения полярности входного сигнала, вход которого подключен.:к сигнальному входу устройства, и блок 7 формирования (компенсационного) порогового уровня, входы которого подключены к сигналь5 8,7540 исходит, а на втором выходе цифрового блока 5 формируется команда разряда интегрирующей емкости аналогового интегратора 2 на величину, достаточную для возвращения выходного напряжения интегратора в пределы его шкалы. Блок 6 определяет полярность входного сигнала и вырабатывает управляющий сигнал с помощью которого из входного сигнала и эталонного опор- 1е ного напряжения на выходе блока 7 формируется компенсационное пороговое напряжение, которое подается на вторые входы компараторов 3 и 4 ° и определяет положительный и отрицательньй .пороговый уровень их срабатывания, Введение блока определения полярности входного сигнала и блока компен- . сационного порогового уровня выгодно отлиФает предлагаемое аналого-дискретное интегрирующее устройство от известного, так как позволяет повы- сить точность, за счет устранения . систематической погрешности, обусловленной временной задержкой .петли обратной связи и существенно увеличить быстродействие за счет уменьшения постоянной интегрирования аналогового интегратора вплоть до. величин, соизмеримых со скоростными качествами операционного усилителя аналогового интегратора. Это позволило уменьшить постоянную интегрирования аналогового интегратора, до 10 М с . и с высокой точностью осуществлять ии

35 тегрирование сигналов длительностью до 20 с.

Формула изобретения

Аналого-дискретное интегрирующее .ао устройство, содержащее последователь7 6 но соединенные блок преобразования полярности входного сигнала и аналоговый интегратор, выход которого подключен к первым входам компараторов, элемент ИЛИ, входы которого и входы блока определения направления счета соединены с выходаеаа компараторов, вы ход элемента ИЛИ через управляющий триггер подключен к управляющим входам блока преобразования полярности входного сигнапа и блока определения направления счета и через формирователь счетных импульсов к управляющему входу интегратора и счетному входу счетчика, вход задания направления счета которого соединен с выходом блока определения направления счета, о т .л и ч а ю щ е е с я тем, что, с целью повышения точности интегрирования и быстродействия устройства, в него введены блок определения полярности входного сигнала и блок формирования порогового уровня, входы которого соединены соответственно с сигнапьным входом и входом опорного напряжения устройства, выход подключен ко вторым входам компараторов, а управляющий вход связан с выходом блока определения полярности входного сигнала, входом соединенного с сигнапьным входом устройства.

Источники информации, принятые во внимание при экспертизе

1, Патент США У 348593, кл кл. G 06 G 7/18, 1976.

2. Авторское свидетельство СССР

Ф 556463, кл. G 06 J 1/00, 1975 (прототип) .

875407 и иг.

Составитель С, Белан .

Редактор Т. Киселева Техред T.Ìàòî÷êà Корректор М. Шароши

Заказ 9338/75 Тираж 748 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

l)3035, Москва, Ж-35, Раушская наб., д, 4/5 филиал ППП "Патент", г. Ужгород, ул. Проектная, 4