Регистр сдвига

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

Сова Советских

Социалистических

Реслублик

„„875462 (61) Дополнительное к авт. сеид-ву— (22) Заявлено 260280 (21) 2889846/18-24

Р1)М. Кл.З с присоединением заявки ¹â€”

G 11 С 19/00 Государственный крмитет

СССР ио делам изобретений и открытий

/ (23) Приоритет (53) УДК 681.327..66(088.8) Опубликовано 231081. Бюллетень Н9 39

Дата опубликования описания 23.1081 (72) Авторы изобретения

В.В.Зуб И В.Н.Свирин (71) Заявитель (54) РЕГИСТР СДВИГА

Изобретение относится к вычислительной технике и может быть использовано в устройствах для контроля параллельного двоичного кода на чет- 5 ность или в цифровых корреляторах для обнаружения кодового слова.

Известен регистр сдвига, каждый разряд которого содержит триггер и элементы И и ИЛИ (1) .

Наиболее близким из известных по технической сущности является регистр, каждый разряд которого содержит триггер с асинхронным информационным и синхронизирующим входом, причем информационный вход триггера последующего разряда соединен,с прямым выходом триггера предыдущего разряда, а информация вводится фо все разряды регистра параллельно Фереэ асинхронные входы триггеров разрядов, синхронизирующие входы всех триггеров соединены с шиной сдвигающих импульсов.

С приходом каждого сдвигающего им- 25 пульса происходит сдвиг записанного в регистр кода на один разряд (2) .

Недостатком известных регистров является невозможность сдвига одноименных битов (например логических 30

"1") записанного кода, что необходимо в ряде устройств, основанных на подсчете числа логических "1" кода.

Использование известного регистра в этих устройствах уменьшает быстродействие, так как число тактов сдвигающих импульсов, необходимых для сдвига всего записанного кода, больше числа логических "1", содержащихся в этом коде.

Цель изобретения — расширение области применения.

Поставленная цель достигается тем,,что в регистр сдвига, содержащий ячейки памяти, каждая из которых из триггера, первый вход которого соединен с информационным входом регистра сдвига, шину сдвига и шину управления, в каждую его ячейку памяти введены элементы И, ИЛИ и элемент НЕ, вход которого соединен с шиной управления и с первым входом первого элемента И, второй вход первого элемента

И подключен ко второму входу триггера данной ячейки памяти и к выходу первого элемента ИЛИ предыдущей ячейки памяти, третий вход первого элемента И каждой ячейки памяти соединен с первым выходом триггера данной

875462 ячейки памяти, второй выход триггера которой подключен к первым входам первого и второго элементов ИЛИ данной ячейки памяти, второй вход первого элемента ИЛИ каждой ячейки памяти соединен с выходом первого элемента

И данной ячейки памяти, выход элемента НЕ каждой ячейки памяти соединен со вторьМ входом второго элемента

ИЛИ, выход которого соединен с первым входом второго элемента И, второй вход второго элемента И подключен к шине сдвига, выход второго элемента

И соединен с третьим входом триггера.

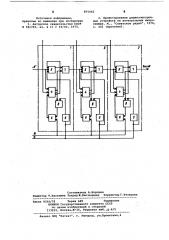

На чертеже изображена функциональная схема регистра сдвига.

Регистр сдвига содержит ячейки 1- 15

1-3 памяти (на чертеже показаны только три ячейки памяти регистра сдвига), причем каждая ячейка памяти регистра сдвига содержит триггер 4, элементы

И 5 и 6, элементы ИЛИ 7 и 8, элемент ;ф

НЕ 9, шину 10 сдвига и шину 11 управЛРНИЯ

Шина установки в "0" регистра на чертеже не показана.

Работа регистра происходит следующим образом.

Регистр устанавливается. в нулевое состояние. Код (например 001) вводится параллельно на первые входы триггеров 4 соответственно в ячейки памяти 3,2 и 1 регистра и на прямых выходах триггеров 4 ячеек памяти 1-3 устанавливаются соответственно потенциалы логических уровней 1,0 и О.

Если на шину 11 управления подать нулевой потенциал, то первый элемент

И 5 будет заблокирован, и на его вы ходе установится нулевой потенциал.

Нулевой потенциал с шины 11 управления инвертируется в элемеьРге НЕ 9 в высокий потенциал, который, пройдя 40 через второй элемент ИЛИ 8, разрешит прохождение импульсов сдвига с шины

10 на третий вход триггера 4 всех ячеек памяти 1-3. Нри поступлении трех импульсов сдвига логическая "1" 45 из ячейки 1 памяти, пройдя регистр, появится на его ныходе.

Если на шину 11 управления подать высокий потенциал, то будет снята блокировка первого элемента И 5. щ

Высокий потенциал с шины 11 упранления инвертируется в элементе HE в низкий потенциал, который позволит упрайлять вторым элементом И 6 потенциалом от прямого выхода триггера

4, фоходящим через первый вход второго элемента ИЛИ 8.

При этом в ячейках 2 и 3 памяти уровень записанного логического "0" с прямого выхода триггера 4 запрещает прохождение сдвигающих импульсов от d0 шины 10 через второй элемент б на третий вход триггера 4, а уровень логической "1" с инверсного выхода триггера 4 разрешает прохождение ин. формации с выхода ячейки памяти 1 65 через первый элемент И 5 и первый элемент ИЛИ 7 каждой из ячеек 2 и 3 памяти.

В ячейки 1 памяти уровень логической "1" с прямого выхода триггера

4 разрешает прохождение сдвигающих импульсов от шины 10 через второй элемент И 6 на третий вход триггера

4, а уровень логического "0" с инверсного выхода триггера 4 запрещает прохождение информации через первый элемент И 5. и первый элемент ИЛИ 7 ячейки 1 памяти.

Таким образом, в ячейках 2 и 3 памяти в триггерах которых записывается логический "0" кода, информация со входа на выход передается через элементы И 5 и ИЛИ 7, а в ячейке памяти 1 информация со входа на выход передается через триггер 4.

С приходом первого сдвигающего импульса произойдет запись логического "0" в триггере 4 ячейки 1 памяти и в регистре не останется ячеек rtaмяти с записанными в них логическими п1н

Таким образом, за один такт сднигающих импульсов произошло перемеще,ние из регистра всех (одной)логических "1" записанного в регистре кода и достигнут эффект сдвига только одноименных битов информации.

Формула изобретения

Регистр сдвига, содержащий ячейки памяти, каждая из которых состоит из триггера, первый вход которого соединен с информационным входом регистра сдвига, шину сдвига и шину управления, отличающийся тем, что, с целью расширения области применения, в каждую ячейку памяти регистра сдвига введены элементы И, ИЛИ и элемент НЕ, вход которого соединен с шиной управления, и с первым входом первого элемента И, второй вход первого элемента И подключен ко второму входу триггера данной ячейки памяти и к выходу первого элемента ИЛИ предыдущей ячейки памяти, третий вход первого элемента И каждой ячейки памяти соединен с первым выходом триггера данной ячейки памяти, второй выход триггера которой подключен к первым входам первого и второго элементов ИЛИ данной ячейки, второй вход первого элемента ИЛИ каждой ячейки памяти соединен с выходом первого элемента И данной ячейки памяти, выход элемента НЕ каждой ячейки памяти соединен со вторым нходом второго элемента ИЛИ, выход которого соединен с первым входом второго элемента И, второй вход второго элемента И подключен к шине сдвига, выход второго элемента И соединен с третьим входом триггера.

875462

Составитель А.Воронин

Редактор Т.Киселева Техред Ж.Кастелевич Корректор Г.Назарова

Заказ 9356/78 Тираж 648 Подписное

ВНИИПИ Государствениого комитета СССР по делам изобретений и открытий

113035, Москва,Ж-35, Раушская наб.,д.4/5

Филиал ППП "Патент", г. Ужгород, ул.Проектная,4

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

В 551701, кл. С 11 С 19/00, 1975 °

2. Проектирование радиоэлектронных устройств на интегральных микросхемах. М., "Советское радио", 1976, с. 261 (прототип) .