Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (6! ) Дополнительное к авт. саид-ву (5 )М. Кл.з

G 11 С 27/00

- (22) Заявлено 08;0280 (21) 28804 94/18-24 с присоединением заявки Но

Государственный комитет

СССР но делам изобретений и открытий (23) Приоритет

Опубликовано 23,108 1,Áþëëåòåíü 89 39

Дата опубликования описания 23,1081 (53) MK 681.327 ° 66 (088.8) Г.Д. Новиков, A,Ã. Козодаев, Е.П. Красненонт и М.й. Захряпин

1

j. (72) Авторы изобретения (71) Заявитель (54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике и технике регулирования.

В технике регулирования часто возникают задачи длительного хранения величины управляющего воздействия, например, хранение постоянного напряжения на управляющем входе кварцевого генератора, находящегося в копьце фазовой автоподстройки, при раэьыкании петли ФАП и других системах автоматического управления.

Известно аналоговое устройство для хранения и выборки информации, ксЗторое состоит из двух каналов записи 15 информации. Информация в виде постоянного напряжения запоминается на двух интегрирующих конденсаторах, при этом величины емкостей выбираются разными, поэтому постоянные 20 времени разряда конденсаторов разные. Напряжения на конденсаторах сравниваются схемой сравнения. При рассогласовании двух напряжений со

:схемы сравнения выдаются команды на 25 включение генераторов коротких импульi сов. Короткие импульсы подаются на кон-. денсаторы и подзаряжают нх. жоаким образом поддерживается равенство напряжений на конденсаторах (11 ., 30

Недостатком данного- ус трой ств а является невысокая надежность длис тельного хранения постоянного напря» жения, так как со временем напряжение на конденсаторах будет уменьшаться.

Наиболее близким к предлагаемому по техиической сущности является аналоговое запоминающее устройство, состоящее иэ интегратора, нуль-органа, ключа, преобразователя код-.напряжение, реверсивного счетчика, логического блока, компаратора и генератора тактовых импульсов. Первый вход интегратора является входом устройства, а второй вход соединен с выходом ключа. Выход интегратора, являющийся выходом устройства, подключен ко второму входу компаратора, первый вход которого подключен к выходу преобразователя код-напряжение.

Информационные входы преобразователя код-напряжение соединены с информационными выходами реверсивного счетчика, а управляющий вход преобразователя подключен к выходу управления логического блока, другие выходы которого подключены ко входам реверсивного счетчика. Первый, Второй, третий и четвертый входы ло87 54б4 гического блока подключены соответств ен но к выход ге нера то ра так товых импульсов, к выходу компаратора, соединенному с сигнальным входом ключа, к выходу нуль-органа, соединенному с управляющим входом:ключа и к выходу реверсивного счетчика.

Первый вход нуль-органа подключен ко входу устройства, а второй к общей шине устройства (21.

Недостатком данного устройства является невысокая надежность длительного хранения запоминающего напряжения.

B случае сбоя реверсивного счетчика в режиме хранения напряжение на интеграторе будет устанавливатЬ.ся равным напряжению на выходе преобразователя, в результате отслеживания интегратора состояния реверсивного счетчика.

Цель изобретения — повышение надежности устройства.

Поставленная цель достигается тем, что в аналоговое запоминающее устройство, содержащее интегратор, первый вход которого соединен с первым входом нуль-органа и со входом устройства, ключ, выход которого соединен со вторым входом интегратора, генератор тактовых импульсов, выход которого подключен к первому входу блока управления, второй вход блока управления соединен с .выходом нуль-органа, второй вход. которого подключен к шине нулевого потенциала, выход блока управления соединен с первым входом реверсивного счетчика, выходы которого соединены со входами преобразователя коднапряжение, компаратор, первых вход которого соединен с выходом преобразователя код-напряжение, второй вход компаратора подключен к выходу интегратора, выход компаратора соединен с третьим входом блока управления, введен пассивный элемент, один из выводов которого подключен к выходу преобразователя код-напряжение, другой вывод соединен с первым входом ключа, второй вход которого со вторым выходом блока управления.

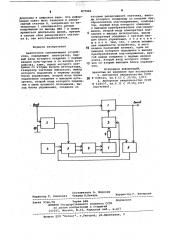

На чертеже изображена функциональная схема предложенного устройства. устройство содержит интегратор 1, нуль-орган 2, ключ, 3, генератор 4 . тактовых импульсов, блок 5 управления, реверсивный счетчик б, преобразователь 7 код-напряжение (ПКН), комщ ратор 8, пассивный элемент 9 и шину 10 нулевого потенциала.

Устройство работает следующим образом.

При наличии входного сигнала .срабатывает нуль-орган 2 и выдает. команду в блок 5, с которого выдается команда на размыкание ключа 4, интегратор 1 запоминает напряжение входного сигнала. При этом срабатывает компаратор 8 и выдает команду в блок 5 управления, разрешая работу цифровой следящей системы (генератор 4 тактовых импульсов, блок

5 управления, реверсивный счетчик б) .

На реверсивный счетчик б начинают поступать импульсы с выхода генератора 4 тактовых импульсов, до тех пор, пока напряжение на выходе ПКН 7 не станет равным напряжению на выходе интегратора 1. При этом по ко О манде с компаратора 8 поступление импульсов с генератора 4 на вход реверсивного счетчика б прекращается.

При уменьшении входного сигнала

15 до "0" срабатывает нуль-орган 2 и эта команда проходит блок 5, при наличии одновременно с этой командой команды с компаратора 8, соответ ствующей совпадению напряжений на выходах интегратора 2 и ПКН 7, бло . О ком 5 выдается команда на ключ 3, и выход ПКН 7 подключается через пассивный элемент 9 и замкнутый ключ 3 ко второму входу интегратора 1. При этом на выходе интеграто25 ра 1 поддерживается напряжение, рав—

goe напряжению на выходе ПКН 7 .

В. случае сбоя реверсивного счет- чика б на выходе IlKH 7 мгновенно изменяется напряжение, на элементе 9

ЗО выделяется разность напряжений на выходе интегратора 1 и OKH 7, срабатывает компаратор 8, по его команде блок 5 размыкает ключ 3, а реверсивный счетчик б описанным выше способом восстанавливает свое состояние, а, следовательно, и напряжение на выходе ПКН 7, равное напряжению на выходе интегратора 1.

При равенстве напряжений на выходе ПКН 7 и интегратора 1 компаратор

40 8 срабатывает, по его команде блок 5 запрещает поступление импульсов на цифровую следящую систему и замыкает ключ 3. Таким образом, интегратор 1 будет продолжать поддерживать

45 напряжение на выходе запоминающего устройства постоянным.

Обеспечение постоянного выходного напряжения с высокой точностью достигается путем выбора соответству50 ющего значения постоянной времени цепи разряда интегратора 1, а именно, такого, чтобы за время пересчета реверсивного счетчика б интегратор 1 разрядился на величину, не превышающую величины напряжения последнего разряда ПКН 7.

Таким образом, при сбое реверсивного счетчика б от импульсных помех, сетевых помех, а также при кратковременном пропадании сети предложен60 ное аналоговое., запоминающее устройство обеспечивает высокую надежность длительного хранения напряжения.

Кроме того, предлагаемое запоминающее устройство может быть исполь65 зовано для длительного хранения ин875464

Формула изобретения

Составитель А. Воронин

Редактор. Т. Киселева Техред Л.Пекарь Корректор Г. Назарова

Заказ 9356/78 Тираж 648

BHHHIIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Подписное

Филиал gllll "Патент", г.Ужгород, ул.Проектная, 4 э формации в цифровом виде. Эта информация может быть записана в реверсивный счетчик 6, напряжение на.интеграторе 1 запоминается равным напряжению на выходе ПКН 7 и может храниться длительное время, причем в случае сбоя реверсивного счетчика 6, оно восстанавливается.

Аналоговое запоминающее устройство, содержащее интегратор, пер. вый вход которого соединен с первым входом нуль-органа и со входом уст« ройства, ключ, выход которого eye- 15 динен со вторйм входом интегратора, генератор тактовых импульсов, выход которого подключен к первому входу блока управления, второй вход блока управления соединен с выходом нуль- 2О органа, второй вход которого подключен к шине нулевого потенциала, выход блока управления, соединен со входами реверсивного счетчика, выходы которого соединены со входами преобразователя код-напряжение, компаратор, первый вход которого соединен с выходом преобразователя код-напряжение, второй вход компаратора подключен к выходу интегратора, выход компаратора соединен с третьим входом блока управления, о т л и ч а ю щ е е с я тем, что, с целью повыаения надежности устройства, в него введен пассивный элемент, один из выводов которого подключен к выходу преобразователя код-напряжение, другой вывод соединен с первым входом ключа, второй вход которого соединен со вторым выходом блока управления.

Источники информаций, принятые во внимание при экспертизе

1 .,Авторское свидетельс тво СССР

Р 649043, кл. G 11 С 27/00, 1977 °

2. Авторское свидетельство СССР Р 628437, кл.С 11 С 27/00, 1977 (прототип).