Запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

Сеюз Советсиии

Сециаюктических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

< 1875470 (61) Дополнительное к авт. свид-ву (22) Заявлено 140?80 (23) 2883199/18-24 с присоединением заявки Ио (23) ПриоритетОпубликовано 23.10.81. Бюллетень N9 39

Дата опубликования описания 23.1 081 (51)М. Кл.

G 11 С 29/00

Государствеииый комитет

СССР

IIo делам изобретеиий и открытий (53) УДК 681. 327 (088. 8) 1

A.A. Дерий, И.A. Дичка, В. И. Корнейчук, М Н.Орлова и В.Я.Юрчишин

Киевский ордена Ленина политехнический-киститутим. 50- летия Великой Октябрьской социалистической революции (72) Авторы изобретения (71) Заявитель (54) ЗАПОМИНИОЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ

Изобретение относится к запоминающим устройствам и может быть использовано в качестве основной и вспомогательной памяти в вычислительных системах.

Известно запоминающее устройство, содержащее накопитель, блок управления, кодовые регистры, блок декодирования, схему равенства кодов и позволяет работать с теми ячейками накопителя, которые дают отказ в од.ном и более разрядах (1).

Недостатком этого устройства является невысокое быстродействие.

Наиболее близким техничесхим решением к данному изобретению является запоминающее устройство,с самоконтролем, содержащее накопитель, выход которого через блок декодированияфсоединен со входом блока управ- 20 ления, с первым и вторым регистрами числа, схему равенства кодов, у которой выход соединен со входом блока управления, а входы — с выходами первого и второго регистров числа, причем выходы этих регистров.через группу элементов ИЛИ подключены к выходной шине, к блоку декодирования, группу элементов И, входЫ которой соединены с выходом блока управ-, 30 лення и выходом второго регистра числа, блок управления,,выход кото рого подключен ко входаМ накопителя, первого и второго регистров числа (2).

Недостатками этого устройства являются небольшое быстродействие и малая обнаруживающая и корректирующая способность, что снижает надежность устройства.

Цель изобретения — повышение быстродействия и надежности устройства.

Поставленная цель достигается тем, что в запоминающее устройство с самоконтролем, содержащее накопитель, регистры числа, первую схему сравнения, блок коррекции, элементы

ИЛИ и блок управления, причем вход накопителя подключен к первому выходу первого регистра числа, первым входам элементов ИЛИ и входу блока коррекции: в выход — к первому входу первого регистра числа и входу второго регистра числа, выходы блока коррекции соединены соответственно с первым входом первой схемы сравнения и вторыми входами элемен- . тов ИЛИ, управляющие входы Элементов ИЛИ и регистров числа подключейы к одним иэ выходов блока управ875470

,ления, один из входов которого сое,динен . с выходом-первой схемы сравнения, введены дешифратор и вторая схема сравнения, входы которой подключены соответственно к первому выходу первого регистра числа и выходу второго регистра числа, а выход соединен со вторым входом первой схемы сравнения, вход и выход дешифратора подключены соответственно ко второму выходу и второму входу пер вого регистра числа, управляющий вход дешифратора и управляющие выходы второй схемы сравнения и дешифратора соединены соответственно с другими выходом и входаьы блока управления.

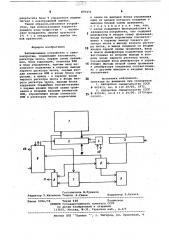

На чертеже изображена функциональная схема запоминающего устройства с самоконтролем.

Устройство содержит накопитель первый 2 и второй 3 регистры числа, дешифратор 4, первую 5 и вторую б схемы сравнения, осуществляющие соответственно функции определения равенства кодов и поразрядного сравнения кодов, блок 7 коррекции, группу элементов ИЛИ 8, блок 9 управления.

Входы 10 регистра 2 и выходы ll элементов ИЛИ 8 является соответственно входами и выходами устройств. Два разряда в регистре 2 и в накопителе

1 являются маркерными. Вход накопи-. теля 1 подключен к первому .выходу регистра 2, первым входам элементов

ИЛИ 8 и входу блока 7, а выход — к первому входу регистра 2 и входу регистра 3. Выходы блока 7 соединены соответственно с первым входом схемы 5 сравнения и вторыми входами элементов ИЛИ 8. Управляющие входы элементов ИЛИ 8 и регистров 2 и 3 подключены к одним из выходов блока

9, один из входов которого соединен с выходом схемы 5 сравнения. Входы схеваа б сравнения подключены соответственно к первому выходу регистра 2 и выходу регистра 3, а выход соединен со вторым входом схемы 5 сравнения. Вход и выход дешифратора 4 подключены .соответственно ко второму выходу .и второму входу регистра 2. Управляющий вход дешифратора 4 и управляющие выходы схемы б сравнения и дешифратора 4 соединены соответственно с другими выходом и входами блока 9.

Устройство работает следующим образом. пусть используется корректирующкФкод мощности K, под которой подраэумевается способность корректирующего кода исправлять ошибки от 1 до К

Число, подлежащее записи в накопитель 1 и предварительно закодированное, поступает на первый регистр числа 2. В режиме контрольной записи .код с первого регистра числа 2 записывается в накопитель 1 и счиЕсли в маркерных разрядах — код

" ю 01, содержимое первого регистра числа 2 передается в блок 7, где производится декодирование числа, в результате которого определяются потери подлежащих коррекции разрядов, значения этих разрядов корректируются и блок 9 управления раз— решает выдачу числа через элементы

ИЛИ 8 на выходы 11 (зто соответствует случаю, когда кратность ошиб- ки не превышает K . Если в маркерных разрядах-код 10, содержимое первого регистра числа с его ин40 версного выхода поступает в блок 7, где производится декодирование и коррекция кода, кроме того, содержимое первого регистра 2 числа с

его инверсного выхода записывается

45 в ту же ячейку накопителя 1, к которой происходит обращение, и считывается на второй регистр 3 числа.

Содержимое первбго регистра 2 числа и обратный код содержимого второго регистра 3 числа поступают в схему б сравнения, которая поразрядно сравнивает этн коды. Номера разрядов, значение которых не совпадает, являются отказавшими. Таким образом схема б сравнения определяет множество отказавших разрядов, которое поступает в схему 5 сравнения, куда поступают и номера ошибочных разрядов, определенные при декодировании в блоке 7. Если

b0 номера являются подмножеством множества номеров отказавших разрядов, исправление произведено верно н блок

9 управления разрешит выдачу откорректированного кода с блока / на выхоб5 ды 11, а в.случае отрицательного

25 тывается во второй регистр числа 3.

Содержимое второго 3 и первого 2 регистров числа сравнивается в схеме б сравнения, Если коды равны, в маркерные разряды первого регистра числа 2 дешифратор 4 записывает 00 и 01 — в случае, если кратность ошибки не превышает

Если же кратность ошибки больше К то в маркерные разряды запишется код 10 . В первых двух случаях в накопитель 1 будет записан прямой код подлежащего записи числа, а в третьем случае - обратный код, причем маркерные разряды всегда записываются в прямом коде. На этом процесс записи завершается.

При считывании информации из ! ячейки накопителя 1, к которой происходит обращение, число поступает в первый регистр числа 2. Дешифратор 4 анализирует состояние маркерных разрядов и если в них код 00, содержимое первого регистра числа 2 через элементы ИЛИ 8 передается на выходы l l (зто означает, что число не содержит ошибок) 875470

Формула изобретения

Запоминающее устройство с самоконтролем, содержащее накопитель, регистры числа, первую схему сравнения, блок коррекции, элементы ИЛИ и блок управления, причем вход на- 15 копителя подключен к первому. выходу первого регистра числа, первым входам элементов ИЛИ и входу блока кор- . рекции, а выход — к первому входу первого регистра числа и входу второго регистра числа, выходы блока коррекции соедийены соответственно с первым входом первой схемы сравнения и вторыми входами элементов

ИЛИ, управляющие входы элементов

ИЛИ и регистров числа подключены

20 Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 443413, кл. G IIC 29/00, 1972.

2. Авторское свидетельство СССР р В 433542, кл G 11 С 29/00; 1972 (про. тотип) .

Составитель В. Рудаков

Редактор Т.Киселева Техред. A.Ñàâêà

Корректор В.Бутяга

;Заказ 9356/78 Тираж 648 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва,.Ж-35, Раушская наб., д.4/5

Филиал ППП Патент, г. Ужгород, ул.. Проектная, 4,результата блок 9 управления выдает сигнал о неисправимой ошибке.

Таким образом, описанное устройство, при использовании корректирующего кода мощностью к, позволяет исправлять ошибки кратности

2 K + 1 и обнаруживать ошибки любой кратности. к одним из вь ходов блока управления один из входов которого соединен с выходом первой схемы сравнения, отличающееся тем, что, с целью повышения быстродействия и надежности устройства, оно содержит дешифратор н вторую схему сравнения, входы которой подключены соответственно к первому выходу первого реги стр а чи сл а и выходу второго ре ги стра числа, а выход соединен со вторым входом первой схемы: сравнения, вход и выход дешифратора .подключены соответственно ко второму выходу и второму входу первого регистра числа, управляющий вход дешифратора и управляющие вымоды второй схемы сравнения и дешифратора соединены соответственно с другими выходом и входами блока управления.