Запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

ОПИСЛНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Респубпик

„„875474 (61) Дополнительное к авт. свмд-ву (22) Заявлено 28. 02. 80 (2t) 2888296/18-24 (51)М. Ил.

G 11 С 29/00 с присоединением заявки ¹â€” (23) Приоритет—

Государственный комитет

СССР ло делам изобретений и открытий

Опубликовачо 231081. Бюллетень №39. (53) УДК 681 ° 327 ° 6 (088.8) Дата опубликования описания 231081 (71) За яв ите ль (54 ) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С CANOKOHTPOJIEM

Изобретение относится к вычислительной технике, в частности к запо-. минающим устройствам (ЗУ) и может быть использовано при передаче цифровой информации.

Известно устройство для обнаружения и локализации одиночных ошибок при передаче цифровой информации, в которую с целью исправления ошибок информации вводится избыточность путем увеличения разрядности хранимых слов (код Хемминга) (11 .

Однако такое устройство ограничивает быстродействие Зу в режиме считывания в виду прохождения каждого 15 слова информации из накопителя к потребителю через устройство коррекции по кодам Хемминга, независимо от присутствия или отсутствия ошибки в слове информации. 20

Наиболее близким к предлагаемому. по технической сущности является з.апоминающее устройство с самоконтролем, содержащее оперативный накопитель, подключенный через блок вос- 25 произведения к регистру числа, блок контроля достоверности информации, соединенный с блоком управления 2 ., Недостатком известного устройства

;является ограничение быстродействия l 30

ЗУ в режиме считывания информации и передачи в другие устройства-потребители. Это объясняется тем, что с применением современных быстродействующих схем накопителей с циклом чтения порядка десятков наносекунд время, необходимое для обнаружения ошибки в каждом считанном слове и организация сигналов выдачи (или блокировки в случае обнаружения ошибки) после анализа информации к потребителям, становится соизмеримым с циклом считывания со схем накопителя, при этом имеется в .виду, что считываемая.информация из памяти, в основном, является безошибочной.

Кроме того, в современных,.вычислительных устройствах потребители информации (процессор, канал, регистры и т.д.) перед использованием ее, тратят дополнительное время на контроль, в частности по модулю два.

Быстродействие.ЗУ должно определяться не только собственной скоростью цикла работы ЗУ, но и его взаимодействием с потребителями по передаче счи-, танной информации.

Цель изобретения — повышение быстродействия запоминающего устройства с самоконтролем.

875474

Поставленная цель достигается тем, что в запоминающее устройство с само-, контролем, содержащее накопитель, входы которого подключены к выходам блока записи, а выходы - к информационным входам блока воспроизведения, управляющие входы блока записи и блока воспроизведения подключены соответственно к первому и второму выходам блока управления, регистр числа, первые входы которого подключены к выходам блока воспроизведения и ко входам блока контроля, управляющий вход- к Иердому выходу блока контроля

Й к третьему входу блока управления а выходы регистра числа подключены ко входам буферного блока, управляющий вход которого подключен к четвертому выходу блока управления, дополнительно введены блок коррекции, информационные входы которого подключены к выходам блока воспроизведения, первый и второй управляющие входысоответственно к пятому и,шестому входам блока управления, первые выходы блока подключены ко вторым входам регистра числа, а вторые выходы блока коррекции подключены к первым входам блока записи, коммутатор, первые входы которого подключены к выходам буферного блока, вторые входы— к выходам блока восйроизведения, управляющий вход - к четвертому выходу блока управления, а выходы коммутатора являются выходами устройства, формироваТель, первый вход которого подключен к выходу блока контроля, а второй и третий входы — соответственно к четвертому и седьмому выходам блока управления, выходы регистра числа подключены ко вторым входам блока записи.

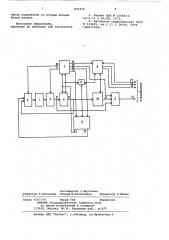

На чертеже представлена функциональная схема запоминающего устройства с самоконтролем.

Запоминающее устройство содержит накопитель 1, блок 2 записи, блок 3 воспроизведения, регистр 4 числа, блок 5 контроля, коммутатор б, блок

7 управления, формирователь 8, блок

9 коррекции, буферный блок 10, второй выход 11 блока 7 управления, выходы 12 блока воспроизведения, ийформационные выходы устройства, второй выход 14 блока 5 контроля, седьмой выход 15 блока 7 управления, первый управляющий выход 1б устройства, первый выход 17 блоха 5 контроля, пятый выход 18 бдока 7 управления, первый выход 19 блока 9 коррекции, четвертый выход 20 блока управления, вйходы 21 регистра 4 числа, выходы 22 буферного блока 10, управляющий выход

23 устройства, шестой управляющий выход 24 блока 7 управления, второй выход 25 блока 9 коррекции, первый вы ход 26 блока 7 управления и управляющий вход 27 устройства.

Работа ЗУ происходит следующим образом.

В ячейках накопителя вместе с каждым словом информации записаны контрольный разряд четности и раэряды коррекции по коду Хемминга. При реализации режима чтения на управляющий вход блока 3 воспроизведения с выхода 11 блока 7 управления подается разрешающий сигнал, по которому информация с выхода 12 блока 3 воспроизведения принимается на регистр 4 числа, блоком 5 контроля, блоком 9 коррекции, коммутатором б и с выхода 13 коммутатора б информация поступает к потребителю.

Быстродействие ЗУ достигается тем, что предварительный анализ информации на четность ведется одновременно в блоке 5 контроля устройства и на входе потребителя информации, в

20 результате чего конец анализа считанной иэ накопителя безошибочной информации в блоке 5 контроля одновременно является сигналом записи этой информации в регистр потребителя и на25 чалом следующего цикла считывания информации иэ накопителя, например для следующего потребителя.

Рассмотрим более подробно два случая, имеющих место при считывании информации иэ накопителя. Первый случай, когда в считываемой информации ошибки нет. В этом случае сигнал со второго вйхода 14 блока 5 контроля через минималъно необходимое время, затрачиваемое для проверки информации íà четность| поступает в Формирователь 8, формирующий сигналы сопровождения, подготовленный к работе импульсом,с седьмого выхода 15 блока

7 управления, разрешающим прием ин40 формации потребителя по сигналу сопровождения исправной информации с выхода 1б формирователя 8.

Фактически фронт выдачи сигнала сопрсвождения безошибочной информа45 ции является началом следующего цикла считывания, но при этом учитывается сигнал обратной связи анализа ошибки на входе потребителя, т.е. в случае ошибки при приеме Информации потребитедем сигнал сопровождения информации иа вход потребителя не поступает, в связи с приходом этого, сигнала от потребителя на направляющий вход 27 устройства s блок 8.

Таким образом максимальное возможное быстродействие ЗУ достигается при считыванйи и передаче исправной информации потребителю, а это является основная режимом работы Зу.

Второй случай, когда в считывае60 мой информации имеется ошибка. Hesaвисимо от типа-ошибки (отказ в считываемом разряде, отказ в цепи считывания или сбой в считываемом разряда) несоответствие признака чет65 ности считанной информации количест,875474 ву единиц в числе будет зафиксировано блоком 5 контроля (и соответственно на входе потребителя), и сигнал ошибки на выходе 17 блока 5 контроля будет передан в устройство 7 управления, на регистр числа 4, при этом по выходу 14 блока 5 контроля произойдет блокировка выдачи сигнала сопровождения исправной информации формирователем по выходу 16;

Блок 7 управления сигналом на выходе 18 включает блок 9 коррекции 2, 10 и в нем происходит анализ ошибки. По окончании анализа по выходу 19 блока

По окончании передачи скорректированной информации потребителю, устройство 7 управления организует цикл записи скорректированной информации в ячейку накопителя по тому же адресу, для исправления информа- ции в ячейке накопителя °

С выхода 24 блока 7 управления сигнал запускает в блоке 9.коррекции формирователи контрольных разрядов коррекции по коду Хемминга, а также разрядов четности, после чего скорректированная информация с выходов

21 регистра 4 числа с контрольными разрядами коррекции и четности, с выхода 25 блока 9 коррекции поступает на вход блока 2 записи. По сигналу с выхода 26 блока управления 7

50 информация записывается в накопитель, 55

Таким образом, сбой разряда информации в ячейке накопителя устраняется, а s случае отказа не устраняется, при этом информация корректируется для передачи потребителю при каждой цикле считывания отказавшей ячейки накопителя. бО

Предлагаемое изобретение позволяет повысить быстродействие ЗУ при

9 коррекции в регистре 4 числа проиэведется коррекция сбойного разряда с одновременной выработкой числа четиос- 5 ти скорректированного слова. По выходу 20 блока 7 управления происходит запись скорректированной информации с выхода 21 регистра 4 числа на буферный блок 10 с одновременным пе- 20 реключением коммутатора 6 на приом по выходу 22 буферного блока 10 и

Передачей потребителю по выходу 13 коммутатора 6, а также подготовка формирователем 8 по выходу 20 блока

7 управления сйгнала сопровождения скорректированной информации по вхо» ду 23, Через минимальное время анализа исправленной информации на входе потребителя по четности, т.е. по снятию сигнала ошибки. на входе потребителя, формирователь 8 по входу 23 организует сигнал сопровожде" ния исправленной информации для записи ее в регистр потребителя. считывании безошибочной информации, а это основной режим работы ЭУ, эа счет уменьшения времени передачи ин- формации на величину задержек в регистре числа, времени выработки блоком управления разрешающего сигнала для блока выдачи кодов и времени срабатывания блока выдачи кодов, так как в данном устройстве информация поступает одновременно как блоку, контроля достоверности информации, подготавливая к включению блок сопровождения сигнала информации, так и через коммутатор на вход.потреби1теля. После одинакового и практически одновременного анализа информация на ее четность выработанным сигналом сопровождения производится ее запись на вход потребителя.

Кроме того, изобретение позволяет исправлять ошибки при считывании, возникающие при случайных сбоях в ячейках накопителя.

Формула изобретения

Запоминающее устройство с сомоконтролем, содержащее накопитель, входы которого подключены к выходам блока записи, а выходы - к информационным входам блока воспроизведения, управляющие входы блока записи и блока воспроизведения подключены соответственно к первому н второму выходам блока управления, регистр числа, первые входы которого подключены к выходам блока воспроизведения и ко входам блока контроля, управляющий вход к первому выходу блока контроля и к третьему входу блока управления, а выходы регистра числа подключены ко входам буферного блока, управляющий вход которого подключен к четвертому выходу блока управления, о т л ич а ю щ е е с я тем, что, с целью повышения быстродействия устройства, оно содержит блок коррекции, информационные входы которого подключены к выходам блока воспроизведения, первый и второй управляющие входы - соответственно к пятому и шестому входам блока управления, первые выходы блока коррекции подключены ко вторым входам регистра числа, а вторые выходы блока коррекции подключены к первым входам блока записи, коммутатор, первые входы которого подключены к выходам буферного блока, вторые входы - к выходам блока воспроизведения, управляющий вход - к четвертому выходу блока управления, а выходы коммутатора являются выходами устройства формирователь, первый вход которого подключен к выходу блока контроля, а второй и третий входы — соответствен«

Но к четвертому и седьмому выходам блока управления, а выходы регистре

875474

Составитель С.Шустенко (Редактор Т.Киселева Техред Ж.Кастелевич Корректор С.Щомак

Заказ 9357/79 Тираж 648 Подписное

ВНИИПИ Государсвтенного комитета, СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", r.Ужгород, ул.Проектная,4 числа подключены ко вторым входам блока записи.

Источники информации, принятые во внимание при экспертизе

1. Патент СИЛ У 3558253, кл.G 11 С 29/00, 1972.

2. авторское свидетельство СССР

Ф 333605, кл.G 11 С 29/00, 1970 (прототип).