Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

ОП ИСАЫИЕ 875621

ИЗОБРЕТЕЫ ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советски к

Социалистические

Рес у (61) Дополнительное к авт, свнд-ву— (22) Заявлено 25.02.80.(21) 2885411/18-21 (5t)N. Кл.

Н 03 К 13/175 с присоединением заявки М

3Ьсударствеииый комитет

СССР ио делам изобретений н открытий (23) Приоритет

Опубликовано 23.10.81. Бюллетень .>е 39 (53) УДК681.325 (088.8) Дата опубликования описания 25.10.81

I.

А. В. Горепекин, С. И. Кравченко, Г, JI. Сатрап и А, П. Бебутов (72) Авторы изобретения (71 ) Зая вн тель (54) АНАЛОГО - ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к телевидению и может быть использовано для. быстродействующего преобразования аналогового телевизионного видеосигнала в цифровую форму, а также для измерения различных быстропротекаюших процессов в системах управления и обработки информации, Известен аналого — цифровой преобразователь (АЦП), содержащий цепь сдвига уровней срабатывания на диодах, источник постоянного тока, и компараторов на логических интегральных микроэлементах (1) .

Однако полный диапазон входного преобразуемого папряжения такого А11П достигает 8 В, что требует для преобразования сигналов низкого уровня спещыльного масштабного усилителя, реа. лизация которого для сигналов с полосой частот 6-10 МГц затруднена, Кроме того, такой АБП не позволяет месть соотношение величин уровней срабатывания, 2

Наиболее близким по технической сущности к предлагаемому является АЦП, содержащий компараторы, управляющие входы которых подключены ко входной шине, а опорные входы - к выходу блока опорных напряжений, и дешифратор, состоящий иэ элементов И - НЕ и инверторов 1 2 ) .

Поскольку уровни компарирования та1О кого AIEI последовательно перекрывают весь диапазон изменяющегося входного напряжения, то неизбежно появление на выходе дешифратора ложных кодовых сос15 тояний, когда, например, предыдущий компаратор уже сработал, а последующий еше нет, или, наоборот, когда имеется одновременное срабатывание соседних компараторов. Кроме того, наличие в разных разрядах различного количества ступеней логического преобразования приводит,к временным задержкам, различным для каждого иэ трех разрядов преобразования.

875621

Устранение искажений, вызванных указанными причинами, ведется с помощью блока синхронизации и подавления помех, . тактированного внешним синалом опроса, что не позволяет получить на выходе АБП кода, меняющегося с изменением входного напряжения, т. е. такой AIIII имеет погрешность преобразования, абсолютная величина которой равна изменению вход ного напряжения за период опроса. !О

Белью изобретения является повышение достоверности преобразования.

Бень достигается тем, что в аналогоцифровом преобразователе, содержащем компараторы, управляющие входы которых подключены ко входной шине, а опорные входы - к выходу блока опорных напряжений, и дешифратор, состоящий из элементов И-HE и инверторов, выход.. первого инвертора соединен со входами второго, четвертого и .пятого элементов

И-НЕ, выход второго инвертора - со входами второго, четвертого и шестого элементов -HE, выход третьего инвертора - со входами четвертого и шестого элементов И-НЕ. выход четвертого инвертора — со входами третьего, шестого и седьмого элементов И -HE, выход первого компаратора соединен со входом первого инвертора и входами треть-З его, шестого и седьмого элементов И НЕ, выход второго компаратора — со входом второго инвертора и входами первого, третьего, пятого и седьмого элементов

И:НЕ, выход третьего компаратора - со входом треьтего инвертора и входами первого, пятого и седьмого элементов

И-НЕ, выход четвертого компаратора - со входом четвертого и входами первого, второго, четвертого и пятого элементов

И-НЕ, ко входам восьмого элемента ИНЕ

40 подключены выходы первого и второго элементов И.-.НЕ, ко входам девятого эле- мента ИНЕ - выходы второго и третьего элементов И НЕ, ко входам десятого эле- мента И-НЕ - выходы че гвертого, пято- 45 ро шестого и седьмого элементов И-HE.

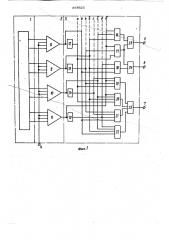

На фиг. 1 изображена структурная схема преобразователя на фиг. 2 - структура ус маковки опорных напряжений.

Схема аналого - цифрового преобразователя содержит блок 1 опорных напряжений, компараторы 2, дешифратор 3, входную шину 4, выходные клеммы 5-7, Выходы блока 1 опорных напряжений подключены к опорным входам компара- 55 торов 8-11, управляющие входы которых соединены со входной шиной 4. Выходы компараторов 8-11 подключены ко входам

4 инверторов 12-15 и к шинам а, в, с, cf соответственно, а выходы инвертора - к шинами, Ь,С, Д в той же последовательности. Входы элемента И-НЕ 16 соедйнены с шинами Ь,(,,Д, входы элемента

И-НЕ 17 — с шинамиб, Ь, 8 входы эле- мента И НЕ 18 - с шинами 0, Ъ, Д; входы элемента И НЕ 18 - с шинами0, Ь, С,d; входы элемента-И-НЕ 20 - с шинами 0, Ь,t,ñ ; входы элемента И-НЕ 21 -. с шинами О, Ь,С,Ц; входы элемента -HE..

22 - с шинами Д, ц, с, с .

Входы элемента И-НЕ 23 подключе- . ны к выходам элементов И-НЕ 16 и 17; входы элемента H-HE 24 — к выходам элементов И-НЕ 17 и 18; входы элемента -HE 25 - к выходам элементов.

И-НЕ 19-22.

Выходы элементов 23-25 соединены с выходными клеммами 5-7 соответственно.

Аналого — цифровой преобразователь работает следующим образом.

Аналоговый видеосигнал через входную шину 4- подается на управляющие входы компараторов 8-11, работающих по зонному принципу.

На опорных входах компараторов устанавливаются напряжения компарирования, формируемые в блоке 1 опорных напряжений. Для.исключения ложных кодовых состояний на выходе АБП в блоке 1 принята специальная структура установки опорных напряжений (см. фиг. 2).

Верхний опорный уровень О „компаратора устанавливается заведомо превышающим максимальный возможный уровень видеосигнала. Римскими цифрами на фиг. 2 обозначены кодируемые градации яркости, арабскими - коды яркости на выходе AHII. Уровни компарирования приведены для TB видеосигнала, имеющего уровень "черного" ОВ и уровень белого" - 1В.

В блоке опорных напряжений АБП может быть принято другое соотношение уровней компарирования при условии сохранения взаимного расположения зон, В некоторый момент времени уровень видеосигнала находится в одной или нескольких зонах компарирования. Отсутст ° вие сигнала в зонах соответствует g градации яркости, соответствующие компараторы меняют по выходу свое состояние, при этом меняются логические уровни на шинах à, à, b,)р,c,C,d,d формируемые инверторами 12-15, 87562 1 б ментов И-НЕ, выход второго ииаертора я со входами второго, четвертога и mec» того элементов ИчНЕ, выход третьего инвертора.- со входами четвертого и meo» того элементов -HE, выход четвертого инвертора - со входами третьего, шестого и седьмого элементов И-НЕ,.выход первого компаратора соединен со входом первого инвертора и входами тр6тьего, о шестого и седьмого элементов И НЕ, г выход второго компаратора - со входом второго инвертора и входами первого, третьего, пятого и седьмого элементов

И-НЕ, выход третьего компара гора со входом третьего инвертора и входами первого, пятого и седьмого элементов ИНЕ выход четвертого компаратора - со вхо дом четвертого инвертора и входами пер» вого, второго, четвертого и пятого эле. QQ ментов И-НЕ ко входам восьмого элемента И-НЕ подключены выходы первого и второго элементов И-НЕ, ко входам девятого элемента И-НŠ— выходы дорого и третьего элементов -FIED ко

Э входам десятого элемелта И-НЕ - выя ° ходы четвертого, пятого, шестого и седьмого элементов И-НЕ.

Совокупность логических состояний на выходах элементов 16-22 преобразуетс элементами 23-25 в трехразрядный двоичный код.

Процесс аналого - цифрового преоб разования происходит следующим образом.

Предположим, что уровень видеосигнала на входе АБП соответствует В градации яркости (см. фиг. 2), и на вы ходе должен появиться код 010.

В этом случае на шинахС1ОЪЬССйус танавливаются следующие уровни:

Ol =0 а= о=о 5=<

С=О .ñ3 = 3 d--o

На выходах элементов И-НЕ 16-22 сформируются уровни: 16 - "1, Х7 ««

18 - "0", 19 - 1", 20 - "1; 21

"1" - 22 - " ". Очевидно, что на вых дах элементов И-НЕ 23-25 возникают нужные кодовые состояния, передаваемы на выходные клеммы 5 - "0"; 6 -."1"

7 - 0".

Формула изобретени

Аналого - цифровой преобразователь, содержащий компараторы, управляющие входы которых подключены ко входной шине, а опорные входы - к выходу блока опор- Зр ных напряжений, и дешифратор, состоящий нз элементов И-НЕ н инверторов, о т л и ч а ю ш н и с я тем, что, с целью повышения достоверности преобразования, выход первого инвертора соединен со вхо- 35 дами второго, четвертого я пятого эле-.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР

N 687586, кл. Н 03 К 13/075, 1975.

2. Авторское свидетельство СССР

М 684735, кл. Н 03 К 13/175, 1975 (прототип).

875621 и,д

0,67

0,75

0.62

0,2

tf ?0 9 8

0- компаратора фиг. 2

Составитель В. Махнанов

Техред М.Рейвес

Корректор Л, Бокшан

Редактор P. Видика

Подписное

Филиал ППП "Патент, г, Ужгород, ул. Проектная, 4

Заказ 9385/86 Тираж 991

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5