Коммутирующее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИ Е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

< | 875628 (61) Дополнительное к авт. свид-ву ¹559389 (22) Зая влево 22.02.80: (21) 2888537/18-2 1 с присоединением заявки ¹ (23) Приоритет

Опубликовано 23, 10.81,Бюллетень ¹I39

Дата опубликования описания 25.10.81 (51)М. К.а.

Н 03 К 17/00

1Ъеударстеееный камнтет

СССР во делам наебретелкй и открв|ткк . (53) УДК 631.325. .65(088. 8) (72) Авторы изобретения.

В. П, Яковлев и Ю. С. Чистяков

Ставропольское высшее военное инженерное им. 60 - летия Великого Октября (71) Заявитель (54) КОММУТИРУЮШЕЕ УСТРОЙСТВО

Изобретение относится к автоматике и вычислительной технике.

По основному авт. св. № 559389 известно коммутирующее устройство, содержащее 1с запоминающих устройств, выходы которых соединены с полным коммутатором, разрядные выходы полного коммутатора подключены ко входам соответствующих линейных коммутаторов11

Недостаток указанного устройства . состоит в низком быстродействии его работы вследствие последовательной организации обмена.

llew изобретения - повышение быстродействия.

С этой целью в коммутирующее устройство с К.V - разрядными входами и

М V - разрядными выходами, содержащее

К запоминающих устройств, ) - разрядные входы которых являются входами устройства, полный коммутатор, информационные 1 - разрядные входы которого соединены с одноименными выходами соответствующих запоминающих устройс тв, информационные т. - разрядные выходы полного коммутатора соединены с одноименными входами соответствующих линейных коммутаторов, а т. - разрядные выходы каждого линейного коммутатора соединены с М/К p - раэря| ными выходами устройства, введены дешлфратор, регистр и блок управления, причем адресные выходы запоминающих, устройств соединены с адресными входами дешифратора, выход которого подключен к регистру, нри этом первый выход блока управления соединен с управляющим входом дешифратора, а второй . выход — с управляющим входом регистр

15 ра, выходы которого подключены к управляющим входам линейных и полного коммутаторов.

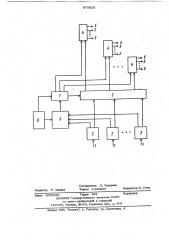

На чертеже представлена функпиональ, ная схема коммутирующего устройства, Схема содержит входы 1, запоминающие устройства 2, коммутатор 3, линейные коммутаторы 4,. выходы 5 коммутируюшего устройства, многосекционный .

875628 дапифратор 6, регистр 7, блок управления Si

Устройство работает следующим образом.

Входная информация содержит код но мера выхода коммутирующего устройства, к которому ее необходимо скоммутировать. Поступающая на входы 1 коммутирукпцего устройства информация накапливается в запоминающих устройствах 2 . о

Коды. номеров выходов с каждого запоминающего устройства 2 поступают на . многосекционный дешифратор 6, причем каждый код на свою секцию. Продешифрированные сигналы адресов коммутации зало- > > минакигся на регистре 7, с которого посту лают. далее на управляющие цепи линейных коммутаторов 4 и коммутатора 3, Блок 8 управления вырабатывает две команды, По первой команде, поступающей на многосекционный дешифратор 6, происходит дешифрация кодов номеров выходов коммутирующего устройства и их запись на регистр 7, По второй команде блока 8 управления управляющие сигналы коммутации с регистра 7 поступают на управляющие цепи коммутаторов 3 и 4, которые осуществляют коммутацию цепей и параллельную передачу информации со входов 1 устройства на соответствующие выходы 5 устройств&

Таким образом, полная передача ин» формации коммутирующим устройством осуществляется за один такт работы, вклю-

4 чающим в себе две команды. Необходимость двух команд обуславливается разделением работы устройства на подготовительные операции и собственно передачу информации.

Введение многосекционного дешифратора 6, регистра 7 и блока 8 управления позволяет увеличить быстродействие работы устройства в К раз.

Формула изобретения

Коммутирующее устройство по авт. св. % 559389, о т л и ч а ю ш е ес я тем, что, с целью повышения быстродействия, в него введены дешифратор, регистр и блок управления, причем адресные выходы запоминающих устройств соединены с адресными входами дешифратора, выход которого подключен к регистру, при этом первый выход блока управления соединен с управляющим входом дешифратора, а второй выход с управляющим входом регистра, выходы которого подключены к управляющим входам линейных и полного коммутаторов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Ж 559389, кл, Н 03 К 17/00, 1975 (прототип). . 875628

Составитель Л. Захарова

Техред А.Бабинен

Корректор Н. Стен

Редактор Р, Пицика

9385/86 Тираж 991

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва,,Ж-35, Раушская наб., д. 4/5

Подписное

Заказ

Филиал ППП "Патент», г. Ужгород, ул. Проектная, 4