Делитель частоты следования импульсов

Иллюстрации

Показать всеРеферат

()875642

ОП ИСАНИ Е

ИЗОБРЕЕЕЙИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт сеид-ву— (22) Заивлеео 19.02.80. (21) 2884336/18-21 с присоединением заявки ¹â€” (23) Приоритет— (5»М.К .

Н 03 К 23/02

Гаеударстаеиимй комитет

CCCP

Опубликовано 23.10.81. Бюллетень ¹ 39 (53) УДК 621;374. .44 (088.8) ио делам изооретеии» и открытий

Дата опубликования описания 23,10.81 (72) Автор изобретения

А. В. Ходаков

) 1 (7l ) Заявитель (54) ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ

Изобретение относится к цифровой технике и может быть применено в аппаратуре. ,обработки цифровой информации, в измерительной аппаратуре, в частности в элект-: ронных измерителях времени.

Известно пересчетное устройство, содержащее основной регистр с дешифратором 3 на входе и дополнительный регистр с шифратором на входе, выходы, которого соединены со входами дешифратора, а входы шифратора соединены с выходами основного регистра (1). тФ

Недостаток устройства — структурная сложность.

Наиболее близким по технической сущности к изобретению является пересчетное устройство, содержащее регистр с дешифратором,на входе, выходы которого соединены с дополнительным регистром с шифратором на входе (21.

Недостатки устройства —. структурная сложность и большое количество оборудования, необходимое для дешифрации, хра- р пения шифрации информации о переносах, Цель изобретения — повышение надеж- ности работы устройства.

С этой целью в делитель частоты следования импульсов, содержащий регистр с дешифратором на входе, введены счетчик адреса, счетчик числа, блок совпадения и анализатор переполнений, импульсный выход которого соединен со счетным входом счетчика числа, а потенциальный выход— с потенциальным входом блока совпадения,. синхронизирующий вход которого соединен с синхронизирующим, входом анализатора переполнений с входом записи счетчика числа и е выходом младшего разряда счетчика адреса, а стробирующий вход — с установочным входом анализатора переполнений и выходом переполнения счетчика адреса, разрядные выходы которого соединены с соответствующими адресными входами регистра с дешифратором на входе, информационные входы и выходы которого соединены соответственно с информационными выходами и входами счетчика числа, выход переполнения которого соединен с входом управления анализатора переполнений, стробирующий вход которого подключен к счетному входу счетчика адреса и к входной шине, при этом анализатор переполнений содержит регистр сдвига и элемент И, причем стро875642

55 бирующий вход анализатора переполнений соединен с первым входом элемента И, синхронизирующий вход — с вторым входом элемента И и синхронизирующим входом регистра сдвига, установочный вход — с обнуляющим входом второго разряда ре- гистра сдвига, нулевой выход которого подключен к его единичному входу и третьему входу элемента И, вход управления — с информационным входом первого разряда регистра сдвига, а импульсный и потенциальный выходы — соответственно с выходом элемента И и с единичным выходом второго разряда регистра сдвига, а блок совпадения содержит триггер и элемент ИЛИ, первый вход которого является стробирующим вхо- дом блока совпадения, а второй вход соединен c выходом триггера, первый и второй входы которого являются соответственно потенциальным и синхронизирующим входами блока совпадения.

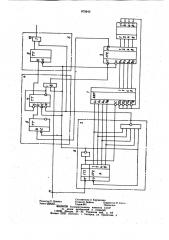

На чертеже представлена структурная, схема устройства.

Оно содержит регистр 1 с дешяфратором на входе (завоминающий блок с дешифратором адреса),. счетчик. 2 адреса, счетчик 3 числа, анализатор 4 переполнений, блок 5 совпадения.

Анализатор 4 переполнений состоит из триггеров 6 и 7 реестра сдвига и элемента 8 И.

Блок 5 совпадения включает в себя триггер 9 (возможно 0-триггер) и элемент 10

ИЛИ.

Позицией 11 обозначена входная шина устройства; счетчики 2 и 3 могут быть как двоичными, танк и декадными (при десятичном пересчете) .

Работает устройство следующим образом.

С помощью счетчика 2 и дешифратора на входе регистра 1 информация из регистра поочередно потетрадно переписывается в счетчик 3 и возвращается на то же место в регистр, причем возвращается неизменной, если отсутствовал при данном состоянии счетчика 2 сигнал на счетном входе счетчика 3.

Сигнал на счетном входе счетчика 3 формируется анализатором 4 в каждом цикле переполнения счетчика 2. Поданный на установочный вход анализатора 4 сигнал формирует разрешение добавления единицы в следующую тетраду. Разрешение добавления единицы снимается, если нет переноса сигнала с выхода переполнения счетчика 3 из предыдущей тетрады.

Таким образом, первые (младшие) разряды делителя частоты находятся в составе счетчика 2 и его переполнение является сигналом переноса в следующие разряды начальную тетраду, размещенную в регистре 1, перенос из которой в следующую тетраду регистра 1 сформируется анализатором 4, когда переполнится начальная тетрада и так далее.

Рассмотрим процесс работы делителя частоты детальнее.

Предположим, что регистр 1 и счетчик 3 обнулены,:а разряды счетчика 2 имеют состояния «1». Поступивший на шину !1 положительный импульс (будем считать его нулевым) своим отрицательным фронтом переведет младший разряд счетчика 2 в состояние «О». При этом сформируется сигнал записи кода в регистр 1 и сигнал переполнения счетчика 2, который установит триггер 7 анализатора 4 в состояние «О».

Триггер 6 анализатора 4 установится в состояние «1», поскольку на выходе переполнения счетчика 3 будет присутствовать уровень «1», свидетельствующий об отсутствии

15 переполнения в счетчике 3.

Поступивший на шину 11 следующий положительный импульс (будем считать его первым) пройдет через элемент 8 и изменит состояние счетчика 3 на « + 1» (по переднему фронту). Отрицательный фронт поступившего импульса счета переведет младший разряд счетчика 2 в состояние «1», сформирует задний фронт импульса записи в регистр 1 и тем самым зафиксирует в регистре l по адресу «15» код «0001», изменит

25 состояние старших разрядов счетчика 2 на «0000», на выходе младшего разряда появится уровень «О», который откроет вход записи числа, хранящегося в регистре 1 по адресу «О» в счетчик 3.

Следующий импульс (второй) на входной шине 11 своим отрицательным фронтом изменит состояние младшего разряда счетчика

2, сформирует окончание записи в счетчике 3, перепишет состояние «I» в триггеры 6 и 7, тем самым запретив передачу импульса на счетный вход счетчика 3, запишет в триггер 6 состояние «1» и откроет вход записи кода в регистр 1.

Третий импульс иа входной шине 11 сформирует задний фронт импульса записи кода в регистр 1, и тем самым зафиксирует в регистре 1 по адресу «О» код «О», изменит состояние старших разрядов счетчика 2 на «0001» и откроет вход записи числа, хранящегося в регистре 1 по адресу «1» в счетчик 3.

Последующие входные импульсы (4, 5, 32) поочередно переберут все адреса тетрад в регистре 1 от первого до пятнадцатого и из каждого из них считают в счетчик 3 и запишут обратно в регистр 1 код «0000».

33-й импульс после выборки по пятнадцатому адресу кода «0001», в счетчике 3 добавит к нему « + 1» и код «0010» вернется в регистр 1 по 15-му адресу.

Аналогичные циклы с периодом, равным периоду переполнения счетчика, будут повторяться до тех пор, пока по пятнадцатому адресу не будет записан, а затем выбран код «1111» код переполнения счетчика 3 (по 480-му импульсу).

875642

В этот период на выходе переполнени счетчика 3 появится уровень «0», который будет зафиксирован по заднему фронту с

480-го импульса в триггере б, по 482-му импульсу будет переписан в триггер 7 и разрешит прохождение 483-го импульса на счетный вход счетчика 3.

С приходом 512-ro импульса по адресу

«00» будет храниться код <0001», а по остальным адресам — код «0000» и по адресу

«l5» будет код, который, начиная с кода

«0000», будет меняться на «+1» через каждые 32 импульса.

Перенос в более старшие тетрады осуществляется аналогично, с той лишь разницей, что сигналы переполнения на выходе счетчика 3 будут поочередно появляться, начиная с адреса пятнадцать до адреса, в который осуществляется перенос, причем, обязательно последовательно в одном цикле между сигналами переполнения счетчика 2.

Необходимо отметить, что наличие сигнала переполнения с выхода счетчика 3 лишь . в одном из адресов (а не поочередно, йа чиная с пятнадцатого адреса) не вызывает

:.формирования импульса иа импульсном

:выходе анализатора, так. как хотя сигнал на выходе младшего разряда счетчика 2 стремится по синхровходу переписать состояние «О» из триггера б в триггер 7, триггер 7 надежно остается в состоянии «1», определяемом связью нулевого выхода триггера 7 со своим единичным входом.

Поделенный импульс формируется в блоке совпадения 5, в котором триггер 9 формирует сдвинутый потенциал . разрешения счетного импульса счетчика 3.

Если во всех тетрадах регистра 1 хранится код «1111», то, начиная с момента поступления импульса с выхода переполнения счетчика 2, триггер 7 будет сохранять состояние «О» до следующего момента поступления следующего импульса. Тогда сдвинутый на период импульса с выхода младшего разряда счетчика 2 на триггере 9 потенциал поступит, как разрешающий, на вход элемента ИЛИ 10, и отрицательный импульс переполнения с вывода счетчика 2 появится на шине, пройдет на выход и в следующем за этим периоде переполнения счетчика 2 в регистре 1 будут записаны по всем адресам коды «0000».

Таким образом, период следования импульса на выходной шине в 2 X А X 4 раз больше периода входных импульсов на шине l I, где 2 — коэффициент пересчета младmего разряда счетчика адреса 2; А — коли чество используемых адресов (коэффициент пересчета старших разрядов счетчика адреса 2); 4 — коэффициент пересчета счетчика числа 3.

Технико-экономические преимущества устройства выражаются экономией элементов памяти и комбинационных логических элементов, что при выполнении его в интегФормула изобретения

«0 разряда регистра сдвига.

3. Делитель по п. 1, отличающийся тем, что блок совпадения содержит триггер и элемент ИЛИ, первый вход которого является стробирующим входом блока совпадения, 50 а второй вход соединен с выходом триггера, первый и второй входы которого являются соответственно потенциальным и синхронизующим входами блока совпадения.

Источники информации, принятые во внимание при экспертизе

1.;«Вопросы радиоэлектроники», 1971, :ер. РТ, вып. 3, с. 126.

2. Авторское свидетельство СССР № 265588, кл. Н 03 К 23/00, 1969, 55

2S

30 ральном исполнении позволяет уменьшать плошадь кристалла и количество полупровод пиковых переходов, и, следовательно, получить экономию оборудования, затрат труда, уменьшения стоимости.

1. Делитель частоты следования импульсов, содержащий регист с дешифратором на входе, отличающийся тем, что, с целью упрощения устройства, в него введены счетчик адреса, счетчик числа, блок совпадения и анализатор переполнений, импульсный выход которого соединен со счетным входом счетчика числа, а потенциальный выход— с потенциальным входом блока совпадения, синхронизирующий вход которого соединен с синхронизирующим входом анализатора переполнений с входом записи счетчика чис-. ла, и с выходом младшего разряда счетчика, адреса, а стробирующий вход — с установочным входом анализатора переполнений и выходом переполнения счетчика адреса, разрядные выходы которого соединены с, соответствующими адресными входами регистра с дешифратором на входе, информационные входы и выходы которого соединены соответствеНно с информационными выходами и входами счетчика числа, выход пере.полнения которого соединен с входом управления анализатора переполнений, стробирующий вход которого подключен к счетному входу счетчика адреса и к входной шине.

2. Делитель по п. 1, отличающийся тем, что анализатор переполнений содержит регистр сдвига и элемент И, при этом стробирующий вход анализатора переполнений соединен с первым входом элемента И, синхронизирующий вход — c вторым входом элемента И и синхронизирующнм входом регистра сдвига, установочный вход — с обнуляющим входом второго разряда регистра сдвига, нулевой выход которого подключен к его единичному входу и третьему входу элемента И, вход управления — с . информационным входом первого разряда регистра сдвига, а импульсный н потенциальный выходы соответственно с выходом элемента И и с единичным выходом второго

875642

Составитель О. Кружнлина

Редактор P. Циника Техред А. Бойкас Корректор М. Коста

Эаназ 9)6@fg Тираж.991 Подписное

ВНЙЙПИ Государственного комитета СССР по делам изобретений н открытнЯ !

13036, Москва, )К вЂ” 35. Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4