Устройство для ввода информации

Иллюстрации

Показать всеРеферат

> ъс

1 Р

И.А. Всяких, А.А. Кошевой, В.A. Абрамов и В.Д. @фарйуур "

- ",-г„„, ;„:

7Щ, 1 Я» (72) Авторы изобретения (7l) Заявитель

Всесоюзный заочный электротехнический институ (54) УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ информации, либо стереть ошибочный символ, что ведет к уменьшению скорости ввода или частичной потере инфор-. мации.

Цель изобретения — повышение надеж- ности устройства.

Поставленная цель достигается тем, что в устройство для ввода информации, содержащее первый блок считывания, блок совпадения, блок синхронизации, и первый блок памяти, входы которого соединены с одними входами блока совпадения и выходами первого блока считывания, входы которого являются первыми входами устройства, выход блока синхронизации соединен со входами синхронизации первого блока считывания, и первого блока памяти, введены второй блок считывания, второй блок памяти, первый и второй дешифрато:ры, перьый и второй элементы saпрета и блок элементов ИЛИ, выходы котор.о являются выходами устройства, входы второго блока считывания являютУстройство относится к дискретной) технике связи, в частности к устрой- ствам ввода двоичной информации.

Известно устройство для ввода информации Plj .

Однако это устройство имеет низкую достоверность ввода.

Наиболее близким к предлагаемому по технической сущности является устройство для ввода информации, содер, 10 жащее блок считывания, усилитель, блок совпадения, блок памяти, блок вырабатывания пачки импульсов, блок выборки импульсов и блок управления, и основано на сравнении вводимой и эталонЛ ной информации с целью исключения ошибок ввода (2).

Недостатком устройства является низкая достоверность ввода информации, так как при наличии тождественных оши" бок как в эталонной, так и в вводимой информации ошибочный символ будет введен. Кроме того, при обнаружении ошибки необходимо либо остановить ввод

3 87751 ся вторыми входами устройства, а выходы соединены с входами второго дешиф-. ратора, второго блока памяти и другими входами блока совпадения, выход.которого соединен с первыми входами пер5 вого и второго элементов запрета, выходы которых соединены с входами первого и второго блоков памяти соответственно, выходы которых соединены с входами блока элементов ИЛИ, аходы первого дешифратора соединены с входами первого блока памяти, выходы первого и второго дешифраторов соединены с вторыми входами первого и второго элементов запрета соответственно, выход блока синхронизации соединен с. входами синхронизации второго блока считывания, второго блока-памяти и первого и второго дешифраторов.

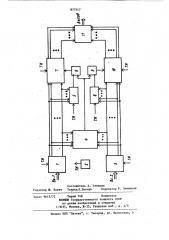

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит первый блок считывания, блок 2 синхронизации, второй блок 3 считывания, блок 4 совпадения, первый дешифратор 5,.второй дешифратор 6, первый блок 7 памяти, первый элемент 8 запрета, второй элемент.

9 запрета, второй блок 10 памяти и блок 11 элементов ИЛИ.

Устройство работает следующим обра30 зом.

Повышение надежности ввода информации достигается путем дополнительной проверки вводимой информации по кодовому признаку (четности, нечеткости, веса и т.д,) вводимых .идентичных пото- З5 ков информации и.промежуточным хранением идентичности пакетов символов информации со стиранием пакета информации, в котором обнаружен вводимый

40 символ с ошибкой.

В случае, когда при вводе в.,идентичных потоках двоичной информации символы тождественны, и они представляют собой кодовые последовательности выбранного кода сообщения, т. е, когда в каждом из них отсутствует ошибка, сигналы "Ошибка" с выхода блока 4 совпадения и с выходов дешифраторов 5 и 6 отсутствуют, поэтому и выходов .:! элементов 8 и 9 запрета на управляю- so щие входы блоков 7 и 10 памяти не поступ@от сигналы на стирание символов.

С приходом с блока 2 синхронизации . иа управляющие входы блоков 7 и 10 ггамяти тактовых. импульсов (ТИ) символы поступающих двух потоков идентичной и тождественной информации поступят на блок 11 элементов ИЛИ. Тогда на

7,ф выходах блока ll элементов ИЛИ будет один поток информации, в символах которого будут отсутствовать ошибки. ю

В случае наличий ошибки в символах только одного из потоков информации, например, поступающего с блока 1 считывания, ошибочный символ обнаружится при его посимвольном сравнении в блоке 4 совпадения. Кроме того, ошибочные.символы будут обнаружены дешифратором 5. На входы элемента 8 запрета поступят одновременно с выходов блока 4 совпадения и дешифратора 5 сигналы "Ошибка". С выхода элемента

8 запрета на управляющий вход блока

7 памяти поступает сигнал на стирание символов с ошибкой, запоминание которых осуществлено.

Тогда информационные символы с блока 7 памяти при приходе тактовых импульсов с блока 2 синхронизации не будут поступать на входы блока 1 1 элементов ИЛИ, но на другие его входы будут поступать идентичные символы с выхода блока 3 считывания, поскольку в них отсутствуют ошибки.

Таким образом, на выходе блока 11 элементов ИЛИ получается .непрерывный поток вводимой информации, в символах которого отсутствуют ошибки. Если ошибки находятся как на выходах блока

1 считывания, так и на выходах блока

3 считывания, но вид ошибки при проверке идентичных символов данных потоков не тождественен, то тогда процесс формирования потока информации, в символах которого отсутствуют ошибки, осуществляется следующим образом.

При обнаружении .ошибок в символе потока информации либо с выходов блока 1 считывания, либо блока 3 считЫвания с помощью блока 4 совпадения и дешифраторов 5 и 6, с выходов либо элемента 8 запрета, либо элемента 9 запрета на управляющие входы блоков

7 и 10 памяти поступит сигнал "Ошибка" и оШибочный символ будет стерт.

Тогда символы, в которых нет ошиб.ки, с выходов блоков 7 и 10 памяти при поступлении на их входы синхроимпульсов (ТИ) с блока 2 синхронизации поступят -на входы блока ll элементов ИЛИ.

Таким образом, с выхода блока 11 элементов ИЛИ в данном случае получаем,непрерывный поток информации, в символах которого отсутствуют ошибки.

В случае, когда в потоках информации с выходов блока 1 считывания и выхоу ов блока 3 считывания имеются иден877517 тичные символы с тождественным видом ошибки, процесс формирования вводимого потока информации,. в символах которого отсутствуют ошибки, осуществляется следующим образом.

При поступлении данных символов с выходов блоков 1 и 3 считывания, на входы блока 4 совпадения их посимвольное сравнение не позволит обнаружить ошибочный символ в потоках информации. 10

Однако при поступлении идентичных символов с выходов блоков 1 и 3 считывания,на входы дешифраторов 5 и.6 их ,проверка по признаку корректирующего кода, в котором представлены символы потоков, позволит обнаружить ошибку в данных символах.

Тогда с выходов элементов 8 и 9 запрета поступят сигналы "Ошибка" на стирание данных символов, записанных в блоках 7 и 10 памяти.

Поэтому при поступлении тактовых импульсов с блока 2 синхронизации и с выходов блоков 7 и 10 памяти данные символы не поступят на входы блока элементов ИЛИ.

Таким образом, с выходов элемента

ИЛИ получаем поток информации, в символах которого отсутствуют ошибки, а вместо идентичных символов с тождественной ошибкой выдается символ с нулевыми кодовыми посылками.

Рассмотренные случаи наличия ошибок во вводимых символах потоков информации М их исправления показывают, что .

35 при использовании предлагаемого устрой ства можно полностью исключить ввод ошибочных еимволов.

Кроме того, как следует из опи40 санного алгоритма работы устроиства, I для исправления ошибок не требуется остановки устройства ввода, что позволяет значительно повысить скорость ввода информации.

Формула изобретения

Устройство для ввода информации, Содержащее первый блок считывания, блок совпадения, блок синхронизации и первый блок памяти,. входы которого соединены с одними входами. блока совпадения и выходами первого. блока считывания, входы которого являются первыми входами устройства, выход блока синхронизации соединен с входами синхронизации первого блока считывания и первого блока памяти, о т л и ч аю щ е е с я тем, что, с целью повышения надежности устройства; в него введены второй блок считывания, в торой блок памяти, первый и второй дешифраторы, первый и второй элементы запрета и блок элементов ИЛИ, выходы которого являются выходами устройства, входы втррого блока считывания являются вторыми входами устройства, а выходы соединены с входами второго дешифратора, второго блока памяти и другими входами блока совпадения, выход которого соединен с первыми входами первого и второго элементов запрета, выходы которых соединены с входами первого и второго блоков памяти соответственно, выходы которых соединены с входами блока элементов ИЛИ, входы первого дешифратора соединены с входами первого блока памяти, выходы первого и второго дешифраторов .соединены с вторыми входами первого и второго элементов запрета соответственно, выход блока синхронизации соединен с входами синхронизации второго блока считывания, второго блока памяти и первого и второго дешифраторов.

Источники информации, принятые во внимание прн экспертизе

1. Авторское свидетельство СССР

У 146338, кл. 21 а 50, 1962.

2. Авторское свидетельство СССР

-356637,кл.G 06 F 3/04, 1969 (прототип).

8775I 7 Ь

Составитель В. Заварин

Редактор В. Ковач Техред Л,Пекарь Корректор В, Синицкая

Заказ 96l5/72 Тираж 748 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, 3-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4