Устройство для вычисления функции z= @ х @ +у @

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистические

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (iii 877531 (61) Дополнительное и авт. свих-нов (22) 5аявлено30. О! . 80 (211 ) 2876317/18-24 с прнсоеднненнене эанвнн,%— (53)М. Кл.

6 06 F 7/552 Ъеударстеенньй комитет

СССР ао делам изобретений н етлрытнй (23) Приоритет

Опубликовано 30. )0.83. бюллетень ЭЬ 40

Дата оаублнковання описания 30. 10.81 (53) УДК 681..3(088.8) (72) Автор изобретения

А.И. Стасюк

Киевский ордена Трудового Красного 3наме институт инженеров гражданской авиац (7l) Заявитель (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ

Z =Qgt+y льтата (1).

Изобретение относится к вычислительной технике и может быть применено в цифровых вычислительных машинах, специализированных вычислительных устройствах и вычислительных средах, построенных на больших интегральных схемах.

Известно устройство ля вычисления зависимости Z = X + 2, содержащее блок суммирования, счетчик, элементы И, ИЛИ, коммутаторы, причем . вторая, третья и четвертая группы входов блока суммирования соединены соответственно с выходами первого, второго и третьего коммутаторов, ко входам которых подключены соответственно выходы регистров первого и второго операндов и регистра резуНедостатком устройства является невысокое быстродействие из-за того, что вычислительный процесс организован в виде последовательности циклов.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее первый счетчик, три элемента И, четыре элемента

II 11

Запрет, второй счетчик и коммутатор, причем выход первого элемента И соединен с первым входом первого элемента ИЛИ, втооога элемента И, третьего и четвертого элементов "Запрет", второй вход элемента ИЛИ соединен с

10 выходом коммутатора и первым входом первого счетчика (2 ).

Недостатком известного устройст" ва является. невысокое быстродействие, определяемое тем, что исходные величи15 ны х и у представляются в виде серии импульсов, обработка которых реализуется последовательно.

Цель изобретения — увеличение быстродействия устройства.

Поставленная цель достигается тем, что в устройство, содержащее элемент

И и элемент ИЛИ, первый вход которого соединен с выходом элемента И, до877531

55 полнительно введены четыре группы по и-1 сумматоров по модулю два (n-разрядность представления аргумента х), и одноразрядных сумматоров и (n-1) элементов И с инверсным входом, причем первые входы одноразрядных сумматоров соединены с входами разрядов аргумента х устройства, выходы одноразрядных сумматоров являются выходами .устройства, вход i-ro сумматора по модулю два первой группы (i=1,2,...„ и-1) соединен с входом (1+2)-га разряда аргумента р устройства, выход

1-го сумматора по модулю два первой группы соединен с прямым входом i-го элемента И с инверсным входом, инверсный вход которого соединен с выходом

i-га сумматора по модулю два второй группы, первый вход которого соединен с выходом i-го сумматора по модулю два третьей группы и первым входом 1-го сумматора по модулю два четвертой группы, выход которого соединен со вторым .входом 1-ro одноразрядного сумматора, второй и третий входы i-ro сумматора по модулю два четвертой группы соединены соответственно с выходом 1-ro элемента

И с инверсным входом и выходом 1-го сумматора по модулю два первой группы (i=1 2, п-1}, второй вход J-ro сумматора по модулю два второй группы подключен к входу ()4-3) -го разряда аргумента устройства Ц=1,2, и-1) второй вход 1с-го сумматора по модулю два третьей группы соединен с выходом (k-1)-ro сумматора по модулю два первой группы, второй вход k-ro сумматора по модулю два первой группы соединен с выходом (k-1)-го суммато ра по модулю два четвертой группы, выход переноса k-га одноразрядного сумматора соединен с третьим входом (k-1)-ro одноразрядного сумматора (k=2,3,...,n-1), второй вход элемента ИЛИ соединен с входом первого разряда аргумента у устройства, вход второго разряда которого соединен с первым входом элемента И и первым входом первого сумматора,по модулю два третьей группы, второй вход которого соединен с выходом элемента

ИЛИ и вторым входом и-го одноразрядного сумматора, третий вход которого соединен с выходом переноса первого одноразрядного сумматора, второй вход элемента И соединен с входом третьего разряда. аргумента у устройства.

4S

4

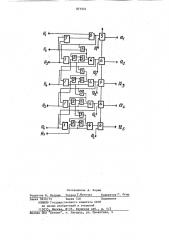

На чертеже представлена блок-схе-ма устройства для случая n=5.

Устройство содержит четыре группы по и-1 сумматоров 1-4 по модулю два, и-1 элемент И 5 с инверсным входом, и-1 одноразрядный сумматор 6, элемент

И 7, элемент ИЛИ 8, одноразрядный сумматор 9, входы 10 и 11 аргументов, выходы 12. Сумматоры по модулю два первой, второй, третьей и четвертой групп, одноразрядный сумматор и элемент И с .инверсным входом, имеющие одинаковый индекс i, образуют 1-й вычитатеиь — сумматор (i=1,2,,n-i), В основу работы устройства положено выражение Z = = y у «у --, при я. 1

9 у х., Работу предлагаемого устройства поясним на примере вычисления зависимости вида Z--х+ф где ЗВ = 33 °

Устройство работает следующим образом.

При подаче на вход 10„, т.е. на разряды 104 102 . 10И соответственно значений разрядов аргумента х, а на вход 11, т.е. на разряды

11, 11 ...,, 11, соответственно значений разрядов аргумента у после окончания перехопного процесса в схеме на выходе элемента HJIH

8 и на выходе четвертого элемента 4 сложения по модулю два каждого вычитателя — сумматора образуются значе— ния величины В, а на выходе однораз рядного сумматора 6 каждого вычитания — сумматора по выражению образуют ся соответственно значения разрядов искдмой величины Z, Благодаря введению новых элементов и связей между ними существенно увеличивается быстродействие, которое равно времени переходного процесса в схеме, т,е. решение получается за промежуток времени, равный задержке сигнала между входом и выходом устройства.

На сути предлагаемое устройство является комбинационным и может работать в асинхронном режиме. Этот факт способствует применению предлагаемого устройства в. вычислительных системах или структурах, реализующих вычислительный процесс в реальном масштабе времени.

Формула

Уст ойство для вычисления функции

Z = Х Фу, содержащее элемент И и элемент ИЛИ, первый вход которого соединен с выходом элемента И, о т—

87 л и ч а ю щ е е с я тем, что, с целью новыщения быстродействия, в него введены четыре группы по и-1 сумматоров по модулю два (n — разрядность представления аргумента Х), и одноразрядных сумматоров и и-1 элементов

И с инверсным входом, причем первые входы одноразрядных сумматоров соединены с входами разрядов аргумента х устройства, выходы одноразрядных сумматоров являются выходами устройсТва, вход i-го сумматора по модулю два первой группы (i=1,2,...,й-1) соединен с входом (1 2) — го разряда аргумента устройства, выход 1 --го сумматора по модулю два первой группы соединен с прямым. входом 1-го элемента И с инверсным входом, инверсный вход которого соединен с выходом

1-го сумматора по модулю два второй группы, первый вход которого соединен с выходом j-го сумматора по модулю два третьей группы и первым входом

1-ro сумматора по модулю два четвертой группы, выход которого соединен со вторым входом e-ro одноразрядного сумматора, второй и третий входы

<-го сумматора по модулю два четвертой группы соединенЫ соответственно с выходом а-го элемента И с инверсным входом и выходом g --ro сумматора по модулю два первой группы (i=1,2,...> п-1).:, второй вход j-го сумматора о модулю два второй группы подклю7531 6 чен к входу (jt3)-го разряда аргумента устройства (j=l,2,...,n-1), второй вход Й-го сумматора по м ду лю два третьей группы соединен с вы5 . ходом (k-1)-ro сумматора по модулю два первой группы, второй вход ф-го сумматора по модулю два первой группы соединен с выходом (Ф-1)-го сумматора по модулю два четвертой группы, 10 выход переноса Ф-ro одноразрядного сумматора соединен с третьим входом (k-1)-ro одноразрядного сумматора (4=2,3,,И-l), второй вход элемента

ИЛИ соединен с вх щом первого разря

15 да аргумента у устройства, вход втб рого разряда которого соединен с первым входом элемента И и первым входом первого сумматора по модулю два третьей группы, второй вход котощ рого соединен с выходом элемента ИЛИ и вторым входом 1-го одноразрядного сумматора, третий вход которого соеди» нен с выходом переноса первого одноразрядного сумматора, второй вход элемента И соединен с входом третьего разряда аргумента устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Ф 646330; кл. G 06 F 7/38, 1979.

2. Авторское свидетельство СССР

11 - 642704, кл. G 06 F 7/38, 1979 (прототип).

877531 гг, 2

Филиал ППП "Патент, r. Ужгород, ул. Проектная, Составитель А. Зорин редактор В. Петраш Техред Т.Иаточка Корректор р

Г. Ога

Заказ 9616/73 . Тираж 748 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035 Москва Ж-35 Раупская наб. д. 4 5