Устройство для вычисления функции е

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистичвскии

Раслублик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К А®ТОРС КОМУ СВИДЕТИЗЬСТВУ

<и 877532. (6l ) Дополнительное к аат. сеид-ву (51)М. Кл. (22) Заявлено 14. 11. 79 (21) 2841359/18-24 с присоединением заявки М— (2Ц П р нори тет

G 06 F 7/556

9вударвтаакны6 квкитвт

СССР

IIQ двлви ива4рвтеиий и открытий

Опубликовано 30. 10.81 ° Бюллетень ¹ 40

Дата опубликования олисания 30.10.81 (5Ç) УДК 681.3 (088.8) В.И. Жабин, В.И. Корнейчук, В.С, Козак, А.С. Покаржевский, А.П. Скочко, В,П. Тарасенко, Е..М. Швец и А.А. Щербина (72) Авторы изобретения

Киевский ордена Ленина политехнический институт им 50-летия

Великой Октя1 фьской социалистической революции (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ е

Изобретение относится к цифровой вычислительной технике и может быть применено в специализированных вычислительных устройствах.

Известно устройство для вычисления функции е, содержащее регистры, счетчики, сумматоры, логические злементы $1).

Однако указанное устройство ввиду больших аппаратных затрат и низкого . 10 быстродействия нецелесообразно приме" нять в тех случаях, когда требуется получить значения е для некоторой возрастающей последовательности значений

Х =Хо+X Ък, =АЙ,"

О,1 1(Наиболее близким по технической сущности к предлагаемому является устройство, содержащее и-разрядный ре» З1 гистр приращений, где п — разрядность приращения аргумента), (и+1) — разрядный первый сдвнгатель и п+4) разрядный сумматор $2 ).

Недостатком известного устройства является то, что для вычисления функ-х ции е в Й точках требуется выполнить Н шагов, длительность каждого из которых равна времени трех сложений и одного умножения, а также низкое быстродействие.

Цель изобретения — увеличение быстродействия.

Поставленная цель достигается тем, что в устройство, содержащее и-разрядный регистр приращений (где п- раз рядность приращения аргумента),(n+1) разрядный первый двигатель и (а+4)разрядный сумматор, дополнительно введены второй (и+1) — разрядный сдвигатель, (n+2) — разрядный воспомогательный регистр и двухразрядный рет гистр цифры, причем выход i-ro разря;. да регистра приращений (i-=1,2,..., +

+n) подключен к (i+1)-мв входу первого и второго сдвигателей, выход j-ro разряда первого сдвигателя (j=1,2..., n+1) подключен к (J+3)-му разряду

3 87753 сумматора, выход %-го разряда второго сдвигателя (k=1,2,...,n+I) подключен к (k+1)-му разряду сумматора, выход (i+2)-ro разряда которого (i

=1,2,...,n+2) подключен ко входу i rc выход m --го разряда вспомогательного регистра (m l 2,.. °,n+2)соединен со входом (m=1,2,...,n+2) соединен со входом (m+1)-го разряда сумматора, выходы первого и второго разрядов которого соединены со входами первого и второго разрядов регистра цифры и выходами устройства, управляющие входы вспомогательного регистра и регистра цифры соединены с тактовым входом устройства, выходы разрядов регистра цифры соединены с управляющими входами второго сдвигателя, управляющие входы первого сдвигателя соединены с входами устройства.

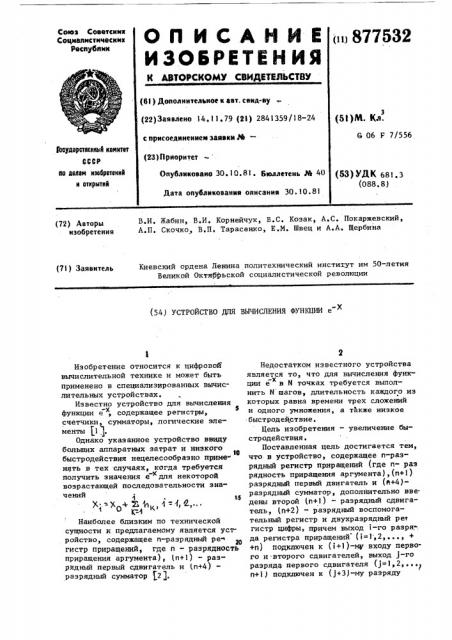

На чертеже представлена блок-схема устройства„

Устройство содержит регистр 1 приращений, сдвигатели 2 и 3, сумматор

4, вспомогательный регистр 5 и ре-. гистр 6 цифры, выходы 7-; входы 8, тактовый вход 9.

Устройство работает следующим образом.

В исходном состоянии в регистре приращения 1 записан код величины

1- %/2, где М удовлетворяет условию

2/3

В каждом 1-ом цикле вычисления на входы 8 поступает цифра у- операн-1 4 да У, имеющая вес 2 где i< — - количество разрядов, после которых фиксируется запятая s УИ .4, и принимающая значение из множества 0,1 2j., Цифра у управляет работой сдвигател

2 таким образом что последний осуФ ществляет передачу кода регистра I со сдвигом на один разряд влево, если у„ =2, без сдвига, если у„. =1, и код регистра не выдается, если у„ =0. Аналогичным образом цифра, записанная в регистре 6, управляет работой сдвигателя 3. В сумматоре

4 складываются коды, поступающие с регистра 5 и сдвигателей 2 и 3> и в двух его старших разрядах формируетйя и выдается на выходы 7 цифра результата У 14. ., имеющая вес

2 ". Цикл заканчивается сигналом по тактовому входу 9, по которому код двух старших разрядов сумматора

4 принимается на регистр 6, a,êoä

2 остальных разрядов заносится s регистр 5.

Устройство позволяет формировать на выходе значения искомой Функции и (И+1) -й точке с задержкой на один цикл относительно ввода в устройство соответствующих разрядов функции в К-й точке. Это позволяет при последовательном соединении устройств приступать к выполнению очередного шага не после окончания предыдущего шага, а непосредственно после получения первых разрядов результата этого шага. Таким образом, процессы интегрирования на й, И+1, (И+2)-м и т.д. шагах при использовании предлагаемого устройства могут быть совмещены во времени, и вревыполнения M шагов составит1=(ZM+

- .И-1)1 где и — разрядность представления Функций. 6 — время суммирова-

) Е ния, а среднее время выполнения одного шага интегрирования при достаточно большом количестве шагов M практически не зависит от разрядности функций и стремится к ТС =2 : р

Устройство для вычисления функции

-у, е, содержащее и-разрядный регистр приращений (где n — разрядность приращения аргумента), (n+ I ) — разрядный первый сдвигатель и (n+4) — разрядный сумматор, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены второй (и+1) разрядный сдвигатель, (n+2) -разрядный вспомогательный регистр и двухразрядный регистр цифры, причем выход i-го разряда регистра приращений (i=l 2,...,n) подключен к (i+I)-му входу первого и второго сдвигателей, выход j-го разряда первого сдвигателя (j=1,2,...р+1) подключен к (j+3)разряду сумматора, выход g-ro разряда второго сдвигателя (k=1,2...„n+I) подключен к (k+1)-му разряду сумматора, выход (1+2)-ro разряда которого (i=1,2... и+2) подключен ко входу i--го разряда вспомогательного регистра, выход m-ro разряда вспомогательного регистра (в=1,2,. n+2) соединен со входом (m+1)-го разряда сумматора, выходы первого и второго разрядов которого соединены со входами первого и второго разрядов ре-. гистра цифры и выходами устройства, управляющие входы вспомогательного регистра и регистра цифры соединены с тактовым входом устройства, выходы разрядов регистра цифры соединены с управляющими входами второго сдвигателя, управляющие входы первого сдвигателя соединены с входами устройс,ва.

877532

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

11 600563, кл. 9 06 Р 15/34, 1978.

2. Каляев А.В. Введение в теорию цифровых интеграторов. Киев "Наукова думка", 1964, с.!94 (прототип ), Заказ 9616/73 Тираж 748 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент", r. Ужгород, ул. Проектная, Составитель А. Зорин

Редактор В. Петраш Техред Т.Наточка Корректор Г. Огар