Устройство для управлениия блоками памяти

Иллюстрации

Показать всеРеферат

(72) Авторы изобретения

В. А. Степанов, В. А. Иванов и В. Ф. Бойков

Ордена Ленина институт кибернетики АН Украинской ССР (71) Заявитель (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ БЛОКАМИ

ПАМЯТИ

Изобретение относится к вычислительной технике и может быть использовано при создании запоминающих устройств.

Известно устройство, содержащее и генератор импульсов счетчик импульр

5 сов, дешифратор импульсов и схему форнирования улравляяния сигналов (1 ).

Недостатком данного устройства является ограниченная область его применения.

Наиболее близким к предлагаемому является устройство для управления блоками памяти, содержащее генераторы импульсов, вход каждого из которых подключен к шине обращения, дешифра15 тор типа модуля памяти, входы которого подключены к кодовым шинам адреса, схемы совпадения, схему разделения,. счетчик импульсов, дешифратор импульсов, схему формирования управляющих сигналов с входом типа операции, подключенным к шине типа операции, с тактирующими входами, подключенными к выходам дешифратора импульсов и с выходами, подключенными к шинам управления (2).

Недостатком устройства является ограниченная область его применения, так как оно не может быть применено для управления блоками памяти, содержа. щими разнотипные модули памяти, поскольку не обеспечивает изменение порядка следования и взаимонезависимое изменение длительности управлякщих сигналов при изменении кода адреса..

Цель изобретения — расширение области применения устройства путем управления блоками памяти на разнотипных модулях.

Поставленная цель достигается тем, что в устройство для управления блоками памяти, содержащее генератор импульсов, счетчик, дешифраторы и формирователь управляющих импульсов, причем вход счетчика подключен к выходу генератора импульсов, а выходы соединены со входами первого дешифратора, вход генератора импульсов и входы

877538

l0

4О

55.второго дешифратора являются соответ— ственно входом обращения и адресными входами устройства, управляющий вход и выходы формирователя импульсов являются соответственно управляющим входом и выходами устройства, введены коммутатор, тактирующие входы которого подключены к выходам первого дешифратора, управлякщие входы — к выходам второго дешифратора, а выходы — к тактирующим входам формирователя импульсов.

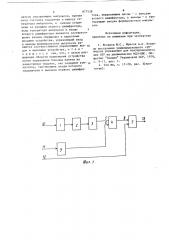

На фиг. 1 изображена структурная схема предлагаемого устройства; на

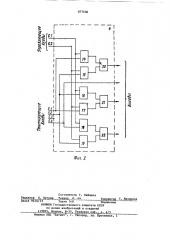

Фиг. 2 — функциональная схема наиболее предпочтительного варианта выполнения коммутатора.

Устройство содержит генератор 1 импульсов, счетчик 2, первый дешифратор 3, коммутатор 4 с тактирующими 5 и управлякщими 6 входами, формирователь 7 управляющих импульсов с тактирующими входами 8 и второй дешифратор 9. На фиг. 1 обозначены также вход 10 обращения, адресные входы 11, управлякщий вход 12 и выходы 13 устройства. Вход счетчика 2 подключен к выходу генератора 1 импульсов, а выходы соединены со входами первого дешифратора 3. Вход генератора импульсов и входы второго дешифратора 9 являются соответственно входом 10 обра— щения и адресными входами 11 устройства. Управляющий вход и выходы формирователя 7 импульсов являются соот— ветственно управляющим входом 12 и выходами 13 устройства. Тактирующие входы 5 коммутатора 4 подключены к выходам первого дешифратора 3, управляющие входы 6 — к выходам второго дешифратора 9, а выходы — к тактирующим входам 8 формирователя 7 импульсов.

Коммутатор 4 содержит элементы И 14-19 и элементы ИЛИ 20-22.

Устройство работает следующим образом.

При обращении к устройству по входу 10 обращения поступает импульс

"Обращение", который запускает генератор 1 импульсов. Одновременно или несколько ранее на входы второго дешифратора 9, предназначенного для дешифрации типа модуля памяти, по адресным входам 11 поступает код адреса, а на вход формирователя 7 управляющих импульсов по управляющему входу 12 поступает сигнал типа операции (например, сигнал "Чтение" или "Запись" ) .

Импульсы с выхода генератора 1 импульсов поступают на вход счетчика 2 и запускают его. Выходные импульсы счетчика 2 поступают на входы первого дешифратора 3, при этом на выходах первого дешифратора 3 формируются импульсы, сдвинутые во времени друг относительно друга, которые поступают на тактирующие входы 5 коммутатора 4.

В соответствии с кодом адреса на одном из выходов второго дешифратора 9 вырабатывается управляющий .сигнал, который поступает на один из управляющих входов 6 коммутатора 4 и обеспечивает подключение соответствующих выходов первого дешифратора 3 к тактирующим входам 8 формирователя 7 управляющих импульсов, который в соответствии с импульсом, поступающим с управлякщего входа 12, формирует управляющие импульсы и выдает их на выходы 13 устройства.

При изменении кода адреса, что соответствует переходу к управлению другим типом модуля памяти, второй дешифратор 9 в соответствии с нозым кодом адреса вырабатывает управляющий импульс на другом своем выходе по сравнению с предыдущим обращением. В результате этого коммутатор 4 обеспечивает изменение подключения выходов первого дешифратора 3 к тактирующим входам 8 формирователя 7 управляющих импульсов. Так как по сравнению с предыдущим обращением изменяется подключение выходов первого дешифрато)а 3 к входам формирователя 7 управляющих импульсов, то изменяется и поряцок следования импульсов на выходах 13 устройства, а также их длительность.

Технико-экономическое преимущество предлагаемого устройства заключается в том, что оно обеспечивает изменение порядка следования и взаимонезависимое изменение длительности управляющих сигналов при изменении кода адреса, за счет чего в отличие от известного оно может быть использовано для управления блоками памяти на различных типах модулей и, таким образом, расширяется область применения устройства.

Формула изобретения

Устройство для управления блоками памяти, содержащее генератор импульсовв, сче тчик, дешифр ато ры и формир о877538 ватель управляющих импульсов, причем .вход счетчика подключен к выходу генератора импульсов, а выходы соединены со входами первого дешифратора, вход генератора импульсов и входы второго дешифратора являются соответст« венно входом обращения и адресными входами устройства, управляющий вход и выходы формирователя импульсов являются соответственно управляющим вхо - ip дом и выходами устройства, о т л ич а ю щ е е с я тем, что, с целью расширения области применения устройства путем управления блоками памяти на разнотипных модулях, оно содержит ком- 15 мутатор, тактиоуюшие входы которого подключены к выходам первого дешифра-. тора, управляющие входы — к выходам второго дешифратора, а выходы — к тактирующим входам формирователя импульсов.

Источники информации принятые во внимание при экспертизе!. Яковлев Ю.С., Юрасов А.А. Вопросы построения унифицированного субмодуля управления для полупроводниковых ОЗУ на динамических ИДЛ-БИС . Об-щество "Знание" Украинской ССР, l979, с. 9 17, рис. l.

2. Там же, с, 17-20, рис. 3(прототип).

877538

Составитель Т. Зайцева

Редактор В. Петраш Техред А Ач корректор Г. Назарова

Заказ 9616/73 Тираж 748 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий.

3)3035> Москва Ж-35 Раушская наб. д. 4/5

Филиал ППП "Патент", г, Ужгород, ул. Проектная, 4