Устройство управления обращением к памяти

Иллюстрации

Показать всеРеферат

С. Ф. Жулинский, В. И. Кутняков и А. Н. ICepreee

1;. (72) Авторы изобретения (7l) Заявитель (54) УСТРОЙСТВО УПРАВЛЕНИЯ OBPAQEHHEM К ПАИЯТИ

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах для организации работы двух вычислительных машин на общее поле памяти.

Известно устройство управления обра- щеннем к памяти, содержащее блок управления, распределитель, генератор, узел индикации свободной эоны памяти, узел управления пуском распределите"" )

Однако укаэанное устройство управления обращением к памяти отличается сложностью и большим объемом оборудования.

Наиболее близким по технической сущности и достигаемому результату к предлагаемому является устройство, состоящее нз трех триггеров, двух элементов ИЛИ и двух элементов И (2).

Недостатком устройства является низкое быстродействие.

Цель изобретения — повышение быстродействия устройства.

Укаэанная цель достигается тем, что в устройство управления обращени" ем к памяти, содержащее элемент ИЛИ, два элемента И и триггер, выходы которого соединены соответственно с. первыми входами первого и второго элементов И, введены шесть элементов И, шесть элементов НЕ и элемент задержки, причем ответный вход устройства соединен с первыми входами тре" тьего н четвертого элементов И, выхо ды которых соединены соответственно с единичньм и нулевьм входами триггера выход элемента задержки соединен со вторыми входами первого и второго элементов И, выходы которых соединены соответственно через первый и второй элементы НЕ с первыми входами пятого и шестого элементов И, выходы которых соединены с соответствующими входами элемента ИЛИ, выход которого является выходом обращения устройства, первый и второй ответные выходы устройства соединены с выходами соот87 ветственно третьего и четвертого элементов И, выход пятого элемента И соединен со вторым входом третьего элемента И.и через третий элемент НЕ со вторым входом шестого элемента И и с первым входом седьмого элемента И, второй вход которого является первым запросным входом устройства, в»иод шестого элемента И соединен со вторым входом четвертого элемента И и через четвертый элемент НЕ со вторым входом пятого элемента И и с пер- вым входом восьмого элемента И, второй вход которого является вторым за- просным входом устройства, третьи вхо" ды пятого и шестого элементов И соединены с установочным входом устройства, четвертые входы пятого и шестого элементов И соединены соответственно через пятый и шестой элементы НЕ с выходами седьмого H восьмого элементов И.

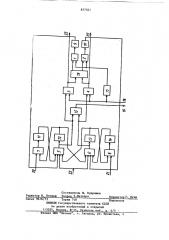

На чертеже представлена блок-схема. устройства управления обращением к памяти.

Устройство содержит элементы И 1-8, элементы НЕ 9-!4, элемент ИЛИ 15, выход 16 обращения устройства, элемент 17 задержки, ответный вход 18 устройства, триггер.19, запросные входы 20 и 21 устройства, установочный вход 22 устройства, ответные выходы 23 и 24 устройства.

Усч ройс тв о работает следующим образом.

В исходном состоянии на вход 18 поступает низкий потенциал, на входы 2022 — высокий потенциал, Под действием этих потенциалов и импульса отрицательной полярности, поступающего на вход 22 и являющегося сигналом установки устройства в исходное состояние, в устройстве в исходном состоянии высокий потенциал устанавливается на выходах элементов И 7 и 8, элементов

НЕ 9, 10, 12 и 13 и на одном (безразлично каком ) выходе триггера 19, а низкий потенциал — на выходе элементов И 1-6, элементов HE 11 и 14, элемента ИПИ 15, элемента 17 задержки, на одном из выходов триггера 19 и на выходах 16, ?3 и 24 устройства, При появлении запроса на обращение к памяти от первой вычислительной машины низкий потенциал устанавливается на входе 20, а при появлении запроса на обращение к памяти от второй вычислительной машины низкий потенциал устанавливается на выходе 21.

7 54!

Пусть первым поступает запрос на обращение к памяти от первой вычислительной машины. Под действием низкого потенциала, установленного на входе 20, на выходе элементов И 7, НЕ 12 устанавливается низкий потенциал, а на выходе элементов И 5, НЕ 11 и ИЛИ ) 5 высокий потенциал, тем самым на выходе устройства 16 формируется высокий о потенциал, который является сигналом обращения к памяти, а на втором входе элемента И 6 устанавливается низкий потенциал, запрещающий обработку запроса на обращение к памяти от второй вычислительной машины. В таком состоянии устройство находится до момента появления на его входе !8 ответного сигнала из памяти в виде импульса положительной полярности, который свидетельствует о том, что. сигнал обращения к памяти принят и вычислительная машина может снять запрос на обращение к памяти. При появлении ответного сигнала на входе !8 на выходе элемента И 3 формируется импульс положительнрй полярности, который поступает на выход 23 и на вход триггера )9, при этом устанавливается или подтверждается высокий потенциал на первом входе элемента И !. После поступления на второй вход элемента И 1 импульса положительнои полярности с выхоца элемента 17 задержки на выходе элемента НЕ 9 формируется импульс отрицательной полярности, ко-орый поступает на первый вход элемента И 5 и устанавливает на выходах элементов И 5 и 7, НЕ 11 и 12 потенциалы, соответствующие исходному состоянию устройства. Величина задержки ответ40 ного сигнала в элементе 17 задержки выбрана такой, что к моменту окончания действия импульса отрицательной полярности на первом входе элемента И 5 первая вычислительная машина снимает запрос на обращение к памяти.

С приходом на первый вход элемента

И 5 отрицательного импульса в устрой— стве заканчивается цикл обработки запроса на обращение от первой вычислительной машины и оно готово без задержки приступить к обработке последующих запросов, поступающих от первой или второй вычислительной машиные

Если во время обработки устройством запроса на обращение к памяти от первой вычислительной машины поступает запрос на обращение к памяти от

877541 второй вычислительной машины, то под действием низкого потенциала на входе 21 устанавливается высокий потенциал на четвертом входе элемента И 6.

Однако на выходе элемента И 6 сохра" няется низкий потенциал до тех пор, пока на его втором входе действует низкий запрещающий потенциал, который снимается только после окончания обработки запроса на обращение к па- 10 мяти от первой вычислительной машины.

После этого без какой-либо задержки устройство приступает к обработке запроса на обращение к памяти от вто" рой вычислительной машины, устанав- )S ливая высокий потенциал на выходе элементов И 6, ИЛИ 15 и низкий запрещающий потенциал на втором входе элемента И 5, тем самым запрещая обработку запроса на обращение к памяти от первой вычислительной машины.

Возможно одновременное поступление от обеих вычислительных мзшин запросов на обращение к памяти, В этом случае очередность обработки запросов устройством произвольна и определяется отклонениями параметров сигналов запроса и элементов схемы устройства.

Применение предлагаемого устройства в вычислительных системах позволяет нри организации работы двух вычислительных машин на общее поле памяти свести к минимальной величине потери времени на обработку запросов на об35 ращение к памяти.

Формула изобретения

Устройство управления обращением к памяти, содержащее элемент ИЛИ, два элемента И и триггер, выходы которого соединены соответственно с первыми входами первого и второго элементов И, 45 отличающееся тем,что,с целью повышения быстродейстьия устройства, и него введены шесть элементов И, шесть элементов HE и элемент задержки, причем ответный вход устройства соединен с первычи входами третьего и четвертого элементов И, выходы которых соединены соответственно с единичным и нулевым входами триггера, выход элемента задержки соединен со вторыми входами первого н второго элементов И, выходы которых соединены соответственно через первый и второй элементы HE с первыми входами пятого и ыестого элементов И, выходы которых соединены с соответствующими входами элемента ИЛИ, выход которого является выходом обращения устройства, первый и второй ответные выходы устрой" ства соединены с выходами соответственно третьего и четвертого элементов И, выход пятого элемента И соединен со вторым входом третьего элемента И и через третий элемент HE co вторым входом шестого элемента И и с первым входом седьмого элемента И, второй вход которого является первым запросным входом устройства, выход шестого элемента И соединен со вторым входом четвертого элемента И и через четвертый элемент 1)Е со вторым входом пятого элемента И и с первым входом восьмого элемента И, второй вход которого является вторым запросньи входом устройства, третьи входы пятого и шестого элементов И соединены с установочным входом устройства, четвертые входы пятого и шестого элементов И соединены соответственно через пятый и шестой элементы ))Е с выхода" .и седьмого и восьмого элементов И.

Источники информации, принятые во внимание при экспертизе

Авторское свидетельство СССР

9 556444, кл. 6 06 F 13/06, 1977. 2. Авторское свидетельство СССР

37460!, кл. 06 E 9/00, )973 (прототип .

877541

Составитель М, Кудряшев редактор B. Петраш Техред Т.Маточка Корректор Г. ОгаР

Заказ 9616773 Тираж 748 Подписное

ВНИИИИ Государственного комитета СССР по делам изобретений и открытий

113035 Москва Ж-35 Раушская наб. л. 4/5

А Л.. А

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4