Устройство для контроля реверсивных регистров сдвига

Иллюстрации

Показать всеРеферат

(72) Авторы изобретения

А.А. елисеев, В.И. Ленкова, В,Ю. Гарин и С.Е. Короленко (7l) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ PEBEPCHBHblX

РЕГИСТРОВ СДВИГА

Изобретение относится к вычислительной технике.

Известны устройства для контроля реверсивных регистров сдвига, в одном из которых, содержащем регистры сдвига, используется метод контроля на небет $11.

Недостатком указанного устройства является ограниченность области его применения.

Наиболее близким к предлагаемому является устройство для контроля реверсивных регистров сдвига, содержащее трехступенчатый сдвигатель, узлы суммирования по модулю два каждой ступе- 1 ни и результата и компаратор j2 )Недостатком устройства яйляется низкое быстродействие вследствие того, что для формирования контрольного разряда результата требуется дополнитель-щ ное время.

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, что устройство для контроля реверсивных регистров сдвига, содержащее сумматоры по модулю два и компаратор, первый вход которого подключен к вы" ходу первого сумматора по модулю два, а второй вход - к выходу второго сумматора по модулю два и является контрольным выходом устройства, выход компаратора является индикаторным выходом устройства, входы первого сумматорапо модулю два являются одними из информационных входов устройства, первый и второй входы второго сумматора по модулю два являются соответственно контрольным и первым управляющим входами устройства, содержит дешифратор, шифратор и селекторы, причем входы шифратора соединены с выходами дешифратора, а выходы — с одними из входов первого селектора, одни из входов второго селектора подключены к выходам первого селектора, а выход соединен с тветьим входом второго сумматора по

877544 модулю два, другие входы второго селектора являются другими информацион. ными входами устройства, вход дешифратора и другой вход первого селекто. ра являются соответственно вторым и 5 третьим управляющими входами устройства.

При этом шифратор целесообразно выполнить содержащим m-1 элементов,ИЛИ, где m — число входов шифра- Ið тора, причем первые входы элементов

ИЛИ соединены с последними входом и выходом шифратора, вторые входы эле ментов ИЛИ подключены к предпоследнему входу шифратора, последующие вход-;1 ды элементов ИЛИ со второго по (m-1)! и соединены соответственно со следующими в порядке убывания входами шифратора, выходы элементов ИЛИ являются соответствующими выходами шифратора.

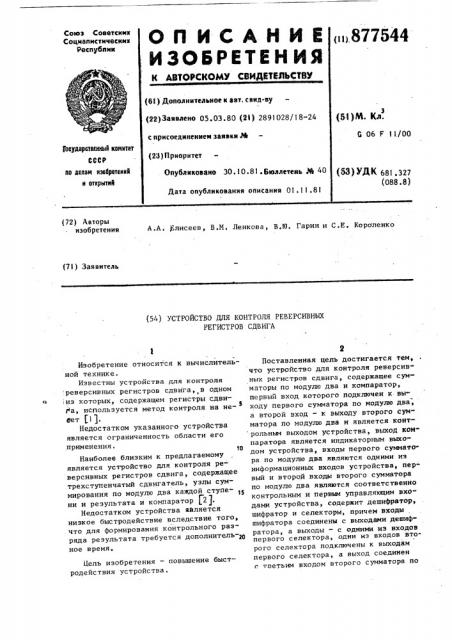

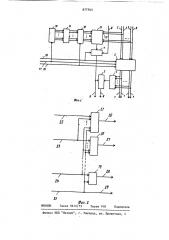

На фиг. 1 изображена функциональ20 ная схема предлагаемого устройства; на фиг .::2 — функциональная схема шифратора.

Одни (фиг. 1) информационные входы 1 устройства подключаются к выходам

Ф контролируемого реверсивного регистра 2 сдвига, к информационным .входам которого подключаются другие информационные входы 3 устройства. Устройст- Зо во содержит первый сумматор 4 по модулю два, компаратор 5 с выходом 6, второй сумматор 7 по модулю два с первым входом 8 и выходом 9,дешифратор 10 шифратор 11, первый селектор 12, второй селектор 13 с одними 14 и другими 15 входами, первый 16, второй 17 и третий 18 управляющие входы, кото.рые соединяются соответственно с уп. равляющими входами контролируемого > реверсивного регистра сдвига.

Первый вход компаратора 5 подклю" чен к выходу первого сумматора 4 по модулю два, а второй вход — к вьгходу 9 второго сумматора 7 по модулю два

45 и является контрольным выходом уст,ройства. Выход 6 компаратора 5 явля1 ется индикаторным выходом устройства, Входы первого сумматора 4 по модулю два являются одними из информационных входов 1 устройства. Первый 8 и второй входы второго сумматора 7 по модулю два являются соответственно контрольным и первым управляющим входом 16 устройства. Входы шифратора 11 соединены с выходами дешифратора 10, а вы-. ходы — с одними из входов первого селектора 12, Одни из входов 14 второго селектора 13 подключены к выходам первого селектора 12 а выход соединен с третьим входом второго сумматора 7 по модулю два ° Другие входы 15 второго селектора 13 являются другими информационными входами 3 устройства. Вход дешифратора 10 и другой вход первого селектора 12 являются соответственно вторьм 17 и третьим 18 управляющими входами устройства.

При этом шифратор 11 целесообразно, выполнить содержащим (фиг. 2)1М -1 элементов ИЛИ 19-21, где у!- число входов 22-25 шифратора и выходы 26-29.

Первые входы элементов ИЛИ 19-21 соединены с последними входом 25 и выходом 29 шифратора. Вторые входы элементов ИЛИ 19-21 подключены к предпоследнему входу 24 шифратора. Последующие входы элементов ИЛИ 19-21 со второго 20 по(й1-1) -й 21 соединены со-, I ответственно со следующими в порядке убывания входами 23 и 22 шифратора..

Выходы элементов ИЛИ 19-21 подключены к соответствующим выходам 28,- 27 и 26 шифратора, Устройство работает следующим образом.

Информация поступает на информационные входы 3 устройства и информационные входы контролируемого реверсивлого регистра 2 сдвига, где сдвигается на число разрядов, определяемое ко- дом на 11-разрядном втором управляющем входе 17 устройства. Тип(арифметический или логический) и направление сдвига определяются сигналами соответственно на первом 16 и третьем 18 управляющих входах устройства. Сдвинутая информация с И выходов контролируемого реверсивного регистра 2 сдвига поступает на входы первого сумматора 4 по модулю два, где формируется контрольный разряд результата, Со второго управляющего входа 17

И бит информации, определяющей количество сдвигов, поступают на вход дешифратора 10, с 1м выходов которого она передается на входы шифратора 11.

В шифраторе 11 информация преобразуется следующим образом: в разряде, соответствующем активному выходу дешифратора 10 и в более старших разрядах формируются единицы, а в младших разрядах формируются нули. Таким образом, формируется код, у которого в старших разрядах расположены единицы, число х„оторых равно числу сдвигов.

C выходов шифратора 11 информация

5 87 поступает на И4 входов первого селектора 12, который управляется сигналом с третьего управляющего входа 18 устройства. При сдвиге влево информация с выхода шифратора 11 передается через первый селектор 12 прямо,при сдвиге вправо — накрест: первый разряд вместо N-го, второй вместо(М-1) -го и т.д. С !и выходов первого селектора 12 информация поступает на одни из входов 14 со второго по (N+I )-й второго селектора 13 где с ее помощью селектируется информация, поступающая на другие входы 15 второго селектора 13 с других информационных входов 3 устройства.

При этом на вход второго селектора 13 передаются только разряды, соответствующие единицам в выходной информации первого селектора 12, что соответствует сдвинутым разрядам контролируемого реверсивного регистра 2 сдвига, которые затем передаются на третий вход второго сумматора 7 по модулю два, формирующего контрольный разряд, который поступает на контрольный выход 9 устройства и второй вход компаратора 5. Этот контрольный разряд сравнивается в компараторе 5 с контрольным разрядом, формируемым первым сумматором 4 по модулю два. Если эти контрольные разряды не совпадают, то на выходе 6 компаратора 5 формируется сигнал сбоя, поступающий на инди" каторный выход устройства.

Технико-экономическое преимущество предлагаемого устройства заключается в том, что в нем формирование контрольного разряда результата сдвига информации выполняется параллельно с операцией сдвига в контролируемом реверсивном регистре сдвига, за счет чего значительно повышается быстродействие устройства.

7544 6 первый вход которого подключен к выходу первого сумматора по модулю два, а второй вход - к выходу второго сумматора по модулю два и является контрольнымм выходом ус т ро йс тв а, выход к омпаратора является индикаторным выходом устройства, входы первого сумматора по модулю два являются одними иэ информационных входов устройства, пер-!

0 вый и второй входы второго сумматора по модулю два являются соответственно контрольным и первым управляющим входами устройства, о т л и ч а ю щ е е с я тем, что, с целью повьппения быстродействия устройства, оно содержит дешифратор., шифратор и селекторы, причем входы шифратора соединены с выходами дешифратора, а выходы — с одними из входов первого селектора, од" ни из входов второго селектора подключены к выходам первого селектора, а выходы соединен с третьим входом второго сумматора по модулю два, другие входы второго селектора являются другими информационными входами устройства, вход дешифратора и другой вход первого селектора являются соответственно вторым и третьим управляющими входами устройства.

2. Устройство по и. 1, о т л и ч а ю щ е е с я тем, что шифратор содержите-1 элементов ИЛИ, где упчисло входов шифратора, причем первые входы элементов ИЛИ соединены с последними входом и выходом шифратора, вто35 рые входы элементов ИЛИ подключены к предпоследнему входу шифратора, последующие входы элементов ИЛИ со второго no(re-!) -й соединены соответственно со следующими в порядке убывания входами шифратора, выходы элементов ИЛИ являются соответствующими выходами шифратора.

Формула изобретения

1. Устройство для контроля реверсивных регистров сдвига, содержащее сумматоры по модулю два и компаратор, Источники информации, 45 принятые во внимание при экспертизе

1. Патент Франции М 2151032, кл. G 11 С 29/00, опублик. 1973.

2. Патент ФРГ Р 2140858, кл ° G 06 F 9/00, опублик. 1973 (про50 тотип) °

877544 .94ь7

1 )

S g

j

Диг. 8

ВНИИПИ Заказ 9616/73 Тираж 748 Подписное

Филиал ППП "Патент", г . Ужгород, ул. Проектная, 4