Запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Респубпин

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТ8У

< >877613 (61) Дополнительное к авт. свид-ву (5 l ) M. Кл. (22) Заявлено 16. 12. 76 (21) 2430152/18-24 с прнсоедннениент заявки № (23) Приоритет

G l1 С I I/00

Гоаударствснный комитет по делу нзооретеннй н OTKpHTIIN

Опубликовано 30.10,81. Бюллетень № 40 (53) УДК628.327..6(088.8) ю

Дата опубликования описани» 30 . 1 О. 8 1

В.Ф. Гусев, Г.Н. Иванов, Г.И. Кренгель, Г;.M. Йерсов, M.3, Шагивалеев и А.У. Ярмухаметов !

Г (72) Авторы изобретения (7I) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам процессоров и каналов вычислительных .машин, и может быть использовано при построении

3ВМ, средств автоматики, управления производственными процессами и коммутации сообщений.

Известны запоминающие устройства, содержащие блок памяти, вход которо10

ro подключен к информационной шине, а выход — к вентилям сумматора. ЭБМ снабжена запоминающим устройством, содержащим восемь общих регистров, которые можно использовать в качестве

1$ аккумуляторов, указателей, содержащих адреса ячеек. памяти, а также индексных регистров длиной в полное слово (1.1.

Однако запоминающее устройство позволяет либо записасть информацию, либо прочитать ее в течение одного цикла. Адресация памяти осуществляется программой. Указанные недостат с ки существенно снижают функциональные возможности данного запоминающего устройства.

Наиболее близким техническим решением к предлагаемому является запоминающее устройство, содержащее блок памяти адресов, информационные выходы которого подключены к соответствующей информационной шине, а один из адресных входов — к дешифратору, блок памяти микропрограмм, выход которого подключен к блоку счетчиков (2).

Данное устройство обладает рядом существенных недостаткон. Во-первых, блок памяти имеет только один адрес" ный вход, что позволяет прочитать и записать информацию в него только по одному адресу, т ° е. в течение одного такта работы процессора доступна только одна ячейка, тогда как в большинстве случаев необходимо иметь доступ к двум операциям и записать результат по третьему адресу.

77613

5 !

О

При существующей системе невозможно какое-либо распараллеливание пересылок информации, так как память имеет всего лишь один вход. При выборе длинного операнда, замещенного более чем в двух подряд расположенных ячейках памяти, необходима обработка адреса на арифметических блоках так как отсутствуют схемы перебора адресов памяти. Входящий в состав устройства блок счетчиков для целей переадресации не используется. Средства увеличения четного адреса на единицу позволяют выбрать не более двух подряд расположенных ячеек, причем старшее слово должно быть помещено в четную ячейку. Обратный перебор адресов от большего к меньпему вообще не предусмотрен.

Цель изобретения — расширизь o6"" ласть применения устройства путем циклического выполнения микропрограммы, Поставленная цель достигается тем, что устройство содержит дополнительные дешифраторы, регистр признаков адресов и коммутаторы, выходы которых подключены к соответствующим входам всех дешифраторов, выходы дополнительных дешифраторов, подключе" ны к другим адресным входам блЬка памяти адресов, первый, второй и третий входы коммутаторов соединены с выходами блока памяти микропрограмм, блоком счетчиков и регистром признаков адресов соответственно, четвертый вход коммутаторов подключен ко входу устройства, а вход регистра при знаков адресов подключен к блоку памяти микропррграмм.

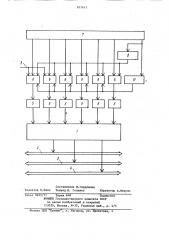

На чертеже дана блок-схема устройства.

Устройство содержит блок 1 памяти адресов, информационные пины 2-4, дешифратор 5, дополнительные дешифраторы 6, коммутаторы 7, блок 8 памяти микропрограмм, блок 9 счетчиков (на чертеже не указан) регистр !О признаков адресов. вход устройства, дешифраторы микропризнаков.

Запоминающее устройство работает следующим образом.

При выполнении операций над числами, помещенными в блок 1 памяти адресов, в первом полутакте работы устройства они вызываются на информа-. ционные шины 2-и, а во втором полутакте работы устройства информации с информационных шин 2-4 записывает4 ся в блок 1 памяти адресов. Таким образом, в течение одного такта работы устройства участвуют шесть адресов ячеек блока памяти адресов— три адреса чтения и три адреса за писи. Это позволяет осуществлять независимые и одновременные пересылки по трем информационным шинам, вызывать на обработку одновременно два операнда в первом полутакте и записывать результат во втором и т.д.

Адреса ячеек блока памяти адресов задаются несколькими источникамн. Например, это может быть адрес, заданный по входу устройства от пульта управления (не показан) для выбора содержимого ячейки блока памяти адресов на индикацию. Другим источником адреса служит блок памяти микропрограмм, имеющий группы разрядов (поля), активизируюшие соответствующий адресный вход блока памяти адресов l. Третьим источником является блок счетчиков 9. Какой из источников

25 адреса должет быть подключен к соответствующему дешифратору 5 и 6, on" ределяется коммутаторами 7. Коммута= торы подключают к дешифраторам юйбо наиболее приоритетный источник — таковым является вход устC ройства (с пульта вмешивается оператор - ему дан высший приоритет), либо тот источник, подключение которого определяется состоянием регистра 10 признаков адресов дополнитель-, ными разрядами блока 8 памяти микропрограмм.

При адресации блока l памяти адресов из блока 8 памяти микропрограмм коммутаторы 7 работают следующим образом (фиг. 2): часть разрядов (поле) адреса задает номер ячейки блок4 памяти адресов, а другой разряд является признаком поля. Если состояние

45 этого разряда единичное, то значение разрядов поля пропускается коммутатором и воспринимается как активный адрес блока I памяти адресов. Если же состояние признака поля нулевое, то в данном такте работ устройства

50 нет чтения (записи) на соответствующую информационную пину 2, 3 или 4.

При этом разряды поля используются для выборки прочих MHKponpHKBSoB через дешифраторы микроприказов

55 для записи (чтения)информации на соответствующую информационную шину от прочих источников вычислительной машины (блоков, регистров, ком5 87761 бинационных схем, не указаны). Нулевое значение поля и признака поля означает отсутствие операции, т.е. нет адреса и нет микроприэнака. Укаэанное соединение блоков значитель- 5 но повышает гибкость использования устройства, облегчает микропрограммирование и экономит объем блока 8 памяти микропрограмм вследствие использования одних и тех же разрядОЮ как для адресации блока 1 памяти адресов, так и для кодирования микроприказов. Таким образом, эадаютс% адреса явно и однозначно, что и необходимо при выполнении большинства алгоритмов обработки.

Однако при обработке длинных операндов, формат которых в несколько раз больше чем формат слова блока 1 памяти адресов, необходим дополни- 20 тельный аппарат, так как на обработку информация может выбираться только по частям словами блока 1 памяти адресов, и над каждым словом должна быть проведена одна и та.же 25 операция. При явном задании адресов памяти микропрограмма будет линейной и займет много ячеек блока 8 памяти микропрограмм. Если учесть, что каждая процедура в действительности Зр не ограничивается одной ячейкой па" мяти, а составляет 6-10 ячеек, то стает очевидной громоздкость такой системы адресации.

Для обработки длинных операндов

3S используется переадресация памяти через блок 9 счетчиков, на которые заносится адрес первых из обрабатываемых подряд расположенных ячеек памяти. Микропрограмма выполняется циклически, при этом в каждом цикле значение счетчиков продвигается (уменьшается или увеличивается на определенную величину). В каждом цикле обрабатывается новая группа ячеек..Оче" видна экономия ячеек блока 8 памяти микропрограмм.

При выполнении сложных микропро-. грамм, каковыми являются операции обработки длинных операндов возника

50 ет необходимость работать как с явной адресацией, так и с переадресацией, причем часть адресов может задаваться явно, другие. могут задаваться бло ком 9 счетчиков, а то и вовсе не использоваться, в то время как соответствующие поля кодируют микроприказы управления. Число сочетаний рк шести адресах огромно и все сочетания могут быть использованы.

Как видно из описания работы предлагаемого устройства, система адресации очень гибкая и позволяет максимально использовать воэможность адресования к блоку памяти по нескольким адресам.

Устройство реализовано в ЭВМ

ЕС-1033 и показывает высокую эффективность. Так производительность ЭВМ на десятичных и логических операциях, где используются длинные операнды составляет 150 тыс. on/c, что в 4 раза больше, чем у ее предшественницы ЕС-1030.

Объем блока памяти микропрограмм сократился с 4096 ячеек до 2048, причем для микропрограмм обработки используется около 1200 ячеек, т.е. в 3 раза меньше чем в EC-1030.

Формула изобретения

Запоминающее устройство, содержащее блок памяти адресов, информационные выходы которого подключены к соответствующей информационной шине, а один иэ адресных входов — к дешифратору, блок памяти микропрограмм, выход которого подключен к блоку счетчиков, о т л и ч а ю щ е е:с я тем, что, с целью расширения области.применения устройства путем циклического выполнения микропрограммы, оно содержит дополнительные дешифраторы, регистр признаков адресов и коммутаторы, выходы которых подключены к соответствующим входам всех дешифраторов, выходы дополнительных дешифраторов подключены к другим адресным входам блока памяти адресов, первый, второй и третий входы коммутаторов соединены с выходами блока памяти микропрограмм, блоком счетчиков и регистром признаков адресов соответственно, четвертый вход коммутаторов подключен ко, входу устройства, а вход регистра признаков адресов подключен к блоку памяти микропрограмм.

Источники информации, принятые во внимание при экспертизе

1. Соучек Б. Мини-ЭВМ в системах, обработки информации. "Мир", 1976, стр. 285-304.

2. Хассон С. Микропрограммное управление. "Мир", 1974, вып. 2, с. 166-169 (нрототип).

877613

Составитель В.Гордонова

Редактор Е.Папп Техред, И. Голинка Корректор А.Ференц !

Заказ 9625 77 Тираж 648 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

)l3035, Москва, Ж-35, Раушская наб, д. 4!5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4