Цифровой коррелятор для обнаружения эхосигналов

Иллюстрации

Показать всеРеферат

ОПHCA HE

ИЗОБРЕ П:ЛИЯ

К АВТОРСКОМУ СВИ ЕТЕДЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 071279 (21) 2876354/18-24

Союз Советскид

Социалистических

Расйубйии, < 11879595

G 06 F 15/336 с присоединением заявки М (23) Приоритет

Государстве иный коиитет

СССР ио делаи изобретений и отирытий.Опубликовано 0711.81. Бюллетень М 41

Дата опубликования описания 07.1181 (53) УДт(681. 323 (088. 8) В.Д. Анисимов, Ю.A. Иванов, Е.Н. Литман и В.Г. Чулошников (72) Авторы изобретения (71) Заявитель (54) ЦИФРОВОЙ КОРРЕЛЯТОР ДЛЯ ОБНАРУЖЕНИЯ

ЭХОСИГНАЛОВ

Изобретение относится к области вычислительной техники и предназначено для взаимнокорреляционной обработки зхосигналов.

Измерение взаимной корреляционной функции (ВКФ) между входным сигналам и опорным в реальном масштабе времени требует обработки всего массива :й выборок (определяемого длительностью сигнала.и точностными параметрами измерения) эа время между двумя соседними выборками, поступающими на вход коррелятора.

-й выборок входного сигнала и и выборок опорного попарно (й пар выборок) поступают на арифметическое устройство (АУ), где традиционным способом осуществляется вычисление одной ординаты ВКФ, соответствукщей данному временному сдвигу (времени запаздывания) входного сигнала относительно опорного..Таким образом, при большом М.и малом интервале между входными выборками сложно реализовать корреляторы, работакщие в реальном масштабе времени. Процесс вычисления в АУ приходится распараллеливать (из-за ограничеиия по быстродей:ствию элементной базы), что приводит к увеличению аппаратурных затрат.

Известен многоканальный цифровой коррелятор (1J, который содержит аналого-цифровые преобразователи, регистры, коммутатор, цифровую линию задержки, распределитель каналов, АУ с соответствующими связями. Данный коррелятор использует слабопрореженные выборки,-что позволяет при некотором ухудшении точностных параметров уменьшить аппаратурные затраты.

Получить значительный выигрыш в аппаратурных затратах при незначитель

15 ных вносимых погрешностях такой коррелятор не позволяет.

Наиболее близким по технической сущности и схемному решению к изобретению является цифровой коррелятор

20 (2, который содержит два цифровых устройства задержки с памятью и АУ.

Выход каждого устройства задержки соединен с соответствующим входом Ау.

Недостатком такого цифрового кор25 релятора являются большие аппаратур ные затраты, определяемые тем, что для реализации АУ при обработке сигналов большой сложности в реальном масштабе времени, требуется значите"

30 .льное количество параллельных кана879595 лов, выполняющих операции умножения и усреднения.

Целью изобретения является упрощение коррелятора, снижение потребляемой мощности.и увеличение его на" дежности, за счет сокращения количества каналов АУ, а также уменьшение объема памяти в одном из устройств задержки.

Поставленная. цель достигается тем, что в цифровой коррелятор для обнаружения эхосигналов, содержащий два блока задержки, входы которых являются соответственно первым и вторым входами коррелятора, и арифметический блок, первый вход которого соединен с выходом первого блока задержки. Управляющие входы арифметического блока и блоков задержки соединены с соответствующими выходами блока управления, введен накапливакщий сумматор, вход которого подключен к выходу второго блока задержки, выход соединен со вторым входом арифметического блока, а вход синхронизации накапливающего сумматора объединен с управляющим входом арифметического блока.

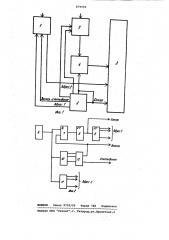

На фиг.1 показана структурная схема цифрового коррелятора для обнаружения эхосигналов; на фиг.2 структурная схема блока управления.

Коррелятор содержит два блока 1, 2 задержки, арифметический блок 3, накапливающий сумматор 4, блок 5 управления, генератор б тактовых импульсов, элемент И 7, счетчики 8-11 и дешифратор 12.

Цифровой коррелятор для обнаружения эхосигналов работает следующим .образом.

B блок 1 задержки (c памятью) объемом М/8 записываются (обычно в момент излучения зондирующего сигнала) прореженные М/В выборок опорного сигнала, где 0 — количество непрореженных выборок входного сигнала на интервале между двумя соседними прореженными выборками опорного сигнала. В блок 2 задержки (с памятью М) непрерывно поступают непрореженные выборки входного сигнала. За время между двумя выборками, поступающими на вход блока 2, происходит опрос блоков 1,2, прячем скорость опроса блока 1 в 3 раз меньше, чем скорость опроса блока 2. Накапливающий сумматор 4 осуществляет суммирование E непрореженных выборок из блока 2.

Результат суммирования совместно с соответствующей прореженной выборкой (поступающей из блока 1 в момент снятия результата суммирования) образуют пару выборок, которая поступает в арифметический блок 3, где выборки, образующие пару, перемножаются, а результаты перемножения суммируются и накапливаются в арифметическом блоке 3. Таким образом, за время между двумя непрореженными

2О

55 выборками, последовательно поступающими на вход коррелятора, осу ществлен полный опрос памяти блоков

1 и 2, образовано М/1 пар выборок, произведено перемножение выборок, составляющих пары, а результат умножения усреднен. Вычисление очередной ординаты происходит на следующем интервале между выборками, поступаницими на вход аналогичным методом.

При этом самая "старая" выборка в памяти блока 2 заменяется вновь поступившей. Вычисление ВКФ происходит непрерывно, информация снимается с выхода коррелятора в темпе поступления информации на вход, т.е. коррелятор обеспечивает обработку сигнала в Реальном масштабе времени.

Это поз воляет, не изменяя шага дискретности вычисления ВКФ,уменьшать количество выборок, поступающих в блок 3 на интервале усреднения, что приводит к уменьшению аппаратурных затрат в арифметическом блоке 3 и объема памяти одного блока задержки

Блок 5 управления работает следующим образом. Генератор б периодически формирует пачки по N+1 импульсов. Первые импульсы в пачках совпадают с моментами прихода входных выборок на коррелятор. Выход генератора б соединен с соответствующими входами элемента 7 И и счетчиков 10 и

11. На выходах счетчика 11 (количест во состояний счетчика равно М) устанавливается адрес блока задержки 2.

По каждому первому тактовому импульсу в пачке осуществляется запись в соответствующую ячейку блока 2 входной выборки .сигнала. Счетсик 11 последовательно формирует М адресов (каждому первому тактовому импульсу в пачке соответствует свой адрес), а после М -го адреса цикл повторяется. После блока 2 очередная входная выборка записывается в ячейку, в которой хранилась самая "старая" выборка. Таким образом, информация блока 2 постоянно обновляется, и в нем хранится Мпоследних текущих выборок входного сигнала. Каждый первый тактовый импульс в пачке, поступающий на счетчик 10, устанавливает его состояние, при котором на выходе.дешифратора 12 формируется команда, переводящая блок 2 в режим записи и запрещающая прохождение тактовых импульсов через элемент И 7.

Со второго по М+1 тактовыми импульсами в пачках осуществляется onрос всех ячеек блоков 1 и 2. Счетчик

10 совместно с дешифратором 12 вторыми тактовыми импульсами в пачках формируют вместо команды "Запись" — команду "Считывание" и снимает запрет на прохождение тактовых импульсов через элемент 7.

N тактовых импульсов (с 2-ro no

N+1) в каждой пачке поступают на счетчик 8 (работающий в режиме деле879595 ния частоты на 8) и далее на счетчик 9 который последовательно по каждому

3 -му тактовому импульсу формирует адрес, опрашивающий ячейку блока 1.

Каждый й+1 тактовым импульсом в пачке счетчик 10 (количество состояний счетчика равно N +1) обнуляется и режим считывания прекращается. С приходом следующего первого тактового импульса в следующей пачке цикл работы повторяется. При этом первым формируется адрес второй ячейки (режим записи), затем третьей (режим считывания),..., A -й, первой, и заканчивается цикл считыванием из второй ячейки.

Запись опорного прореженного сиг- 35 нала в блок 1 осуществляется в момент излучения сигнала. При этом формируется команда "Запись". Далее эта команда в блок 1 не подается (на структурной схеме фиг.2 не показана 2G коммутация команды "Запись" — "Считывания" на блок 1) . С выхода счетчика 8 синхроимпульсы поступают на блок 3 и накапливающий сумматор 4.

Таким образом, изобретение поз- 5 воляет уменьшить весогабаритные ха- . рактеристики, стоимость и потребляемую мощность, а также увеличить надежность устройства в целом.

За счет уменьшения объема аппаратуры, потребляемой мощности, стоимости и увеличения надежности расширены функциональные возможности тракта обработки сигналов. Например, использование описанного устройства позволяет без увеличения габаритов либо реализовать более высокие точностные параметры обнаружения и анализа (использование квадратурных каналов, преобразования Гильберта и др), либо увеличить число одновременно обраба- 40 тываемых каналов (параллельное соединение нескольких предлагаемых корреляторов) . Последнее имеет большое практическое значение, так как большинство реальных систем обработки сигналов характеризуется высокой многоканальностью обработки, как по частоте, так и по пространству.

Описанный коррелятор может быть использован как в устройствах обнаружения, так и в измерительных системах. Коррелятор реализован на ИМС серий 133 и К 565.

Формула изобретения

Цифровой коррелятор для обнаружения эхосигналов, содержащий два блока задержки, входы которых являются соответственно первым и вторым входами коррелятора, и арифметический блок, первый вход которого соединен с выходом первого блока задержки, управляющие входы арифметического блока и блоков задержки соединены с соответствующими выходами блока управления, о т л и ч а юшийся тем, что, с целью упрощения коррелятооа. в него. введен накапливакщий сумматор„, вход которого подключен к выходу второго блока задержки, а выход соединен со вторым входом арифметического блока, вход синхронизации накапливающего сумматора объединен с управляющим входом арифметического блока.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 646341, кл. G 06 F 15/34, 1977.

2. Патент CIJA Р 3950635, кл. 235-156, опублик. 1977 (прототип) .