Запоминающий элемент

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВ ЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 310380 (21) 2902980/18-24

«i>879647

Р1)М. Кл.

G 11 С 9/00 с присоединением заявки Но

Государственный комитет

СССР по делам изобретений и открытии (23) Приоритет

Опубликовано 0711.Ч1 Бюллетень Н9 41 (53) УДК 681. 327. 66 (088.8) Дата опубликования описания 07. 11. 81 (72) Авторы

В. A. Миклашевич и В. В. Мочалов (54) ЗАПОМИНАЮ(цИИ ЭЛЕМЕНТ

Изобретение относится к области автоматики и вычислительной техники и предназначено для применения в цифровых устройствах, в частности в буферных запоминающих устройствах для оперативного запоминания и хранения мгновенных значений двоичного сигнала.

Известен. запоминающий элемент (1), содержащий RS-триггер.

Недостатками указанного запоминающего элемента являются невозможность управляемой выборки и хранения дискретной информации и, кроме того, неопределенность состояния при опре- 15 деленных запрещенных комбинациях сигналов на установочных R u S-входах. Так, для RS-триггера, построенного на ячейках И-НЕ, запрещенной комбинацией является R =0 и S = 0, 20 а для триггера, построенного на ячейках ИЛИ-НŠ— R =1 и S = 1.

Наиболее близким из известных по технической сущности явялется sanoминающий элемент, содержащий основной 25

RS-триггер, имеющий сигнальный (информационный) и управляющий входы, дополнительный RS-триггер, R-вход которого подключен к Q - -выходу основного триггера, подключенного R-, . 3Q входом. к информационному входу sanoминающего элемента, причем S-входы обоих RS-триггеров, подключены к управляющему входу запоминающего эле мента, выходом которого является вход дополнительного RS-триггера Ю . ,Недостатком этого устройства, выбранного за прототип, является наличие ложных срабатываний дополнительного RS-триггера при определенной последовательности появления сигналов на информационном и управляющем входах запоминающего элемента. Так, в режиме приема информации на управляющем входе существует нулевой запрещающий сигнал., Пусть на информационном входе запоминающего элемента существует единичный сигнал. В это время на установочных

R- u S-входах дополнительного RSтриггера присутствуют нулевые сигналы. Теперь сигнал на информационном входе сменим на нулевой. Как только на Q - выходе основного RS-триггера появится единичный сигнал, в это врЕмя на управляющем входе сформируется также единичный сигнал. Таким образом, на установочных входах дополнительного элемента происходит переход сигналов-с запрещенного сос

879647

5 lO

3 тояния на нормальное, при котором дополнительный триггер должен принять единицу по своему R-входу, а на выходе сформировать нулевой сигнал, так как на информационном входе запоминающего элемента этот (нулевой) сигнал уже существует.

Однако, у дополнительного RS-триггера перед этим было неопределенное состояние, поэтому вместо единицы по

В-входу дополнительный RS-триггер может принять либо единицу либо нуль, хотя входной информационный сигнал запоминающего элемента раньше, чем была произведена смена сигнала на управляющем входе, обращен в нулевой сигнал. Поэтому, несмотря на сдвиг во времени событий смены сигналов на информационном и управляющем входах на величину задержки в схеме И-НЕ, устройство имеет тенденцию к ложному срабатыванию и хранению ложного информационного сигнала на выходе запоминающего элемента, не соответствующего входному сигналу.

Цель изобретения — повышение надежности запоминающего элемента.

Поставленная цель достигается тем, что в запоминающий элемент, содержащий первый триггер, выход которого соединен с первым входом второго триггера, выход которого является выходом запоминающего элемента, входы первого триггера подключены соответственно к информационной и управляющей шинам, введены элемент И-НЕ и элемент задержки, вход которого соединен с первым входом элемента

И-НЕ и с первым входом первого триггера, выход которого соединен со вторым входом элемента И-НЕ, второй и третий входы второго триггера соединены соответственно с выходами элемента -HE и элемента задержки.

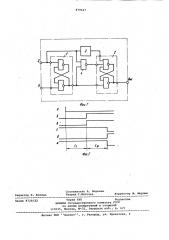

На фиг. 1 изображена функциональная схема предложенного запоминающего элемента; на фиг. 2 — временная диаграмма его работы.

Он содержит триггеры 1 и 2, .элемент задержки 3, элемент И-НЕ 4, управляющую шину 5, информационную шину б.

Устройство работает следующим образом.

В исходном состоянии к шине 5 запоминающего элемента приложен нулевой (разрешающий) сигнал, который принудительно выключает триггер

1, а также элемент .4. На выходе триггера 1 сформирован единичный сигнал, который, будучи приложен к первому входу триггера 2,.открывает путь для прохождения информационного сигнала с входа на выход запоминающего элемента без изменения фазы в результате двойного инвертирования на элементах

И-НЕ триггера 2. Если при этом на шине б запоминающего элемента присутствует единичный сигнал, то на выходе триггера 1 возникает нулевой сигнал, который поступает на первый вход триггера 2, возбуждает на выходе триггера 2 и выходе запоминающего элемента единичный сигнал. Аналогично при наличии на шине б нулевого сигнала на выходе запоминающего элемента также возникает нулевой сигнал.

В режиМе запоминания элемент работает следующим образом.

При наличии нулевого сигнала на шине 6 при подаче единичного (запрещающего) сигнала. на. шину 5, на

15 выходе второго элемента И-HE триггера Формируется нулевой сигнал, который блокирует информационный сигнал на шине б.

Триггер 2 в это время не меняет своего состояния, так как его вто26 рой вход блокирован нулевым потенциалом с выхода запоминающего элемента.

Такое состояние запоминающего элемента (режим хранения. информации) может оставаться сколь угодно долго, независимо от того, изменится сигнал на шине 6 запоминающего элемента или нет. Если сигнал на шине 5 снова обратить в нуль, т.е. прекратить режим хранения информации, то запоминающий элемент на своем выходе либо сохранит прежний нулевой сигнал, при наличии на шине б нулевого.сигнала, либо сформирует на выходе запоминающего элемента единичный сигнал, при единичном сигнале на шине

6 запоминающего элемента. При этом запоминание и хранение нулевого значения на шине б осуществляется на триггере 1, а единичного значения сигнала — на триггере 2. Таким обра40 зом, в запоминающем элементе обеспечивается запоминание и хранение знасения сигнала на шине б запоминающего элемента, которыЯ существовал к моменту установки на шине 5 единичного

45 (запрещающего) сигнала, при ем информация хранится на все время при:сутствия этого единичного сигнала на шине 5.

Неблагоприятные условия для запощ минания значения сигнала на шине б наступают тогда, когда одновременно на установочных входах триггера 2 сигналы сменяются с нулевых на единичные значения. Поскольку для RSтриггера, построенного на элементах

И-НЕ, установочная комбинация R = 0 и S = 0 запрещена, то после существования такой комбинации сигналов, т.е. когда R = 1 и S = 1, состояние триггера 2 будет неопределенным: он

d0 может оказаться или в нуле или в единице. Поэтому для исключения неопределенности состояния триггера 2 при смене сигналов на К- и S-входах триггера 2 с нулевых на единич65 ные в запоминающий элемент дополни879647 тельно введены элемент И-НЕ и элемент задержки.

3а пояснением устранения ложных срабатываний обратимся к временной диаграмме работы запоминающего элфментана:. фиг. 2. 5

Прй смене значения сигнала а на шине 6 с 1 на 0 через время задержки t на выходе триггера 1 появится единичный сигнал б. Пусть в это же время на шине 5 подан сигнал 1п в . Через время t4. равное времени задержки в,элементе 4, на его выходе произойдет смена сигнала r c 1 на 0, который блокирует: работу первого элемента И-НЕ триггера 2 нулевым потенциалом на входе триггера 2, а единичный сигнал д на . втором входе триггера 2 установится только после того, как сигнал в пройдет через линию задержки 3 с некоторым запаздыванием на время 20 0Ъ t. Следовательно, единичный сйгнал б на входе триггера 2 устаФ навливается раньше, чем произойдет смена сигнала д на выходе элемента

3 с нуля на единицу и триггер 2 с 25 единичного состояния перейдет в нулевое в соответствии с нулевым сигналом а на шине 6, который уже существует на протяжении времени t .

Поэтому сигнал б проинвертнровавшись на втором элементе триггера 2 и обратившись в нулевой сигнал ж, поступает на выход запоминающего элемента ° К этому времени в тригге» ре 1 происходит запоминание инвертированного значения сигнала а на шине 6, так как вход второго элемента И-НЕ триггера 1 сблокирован выходным нулевым потенциалом с выхода первого элемента триггера 1 и даль- 40 нейшее продвижение информации по входу (по шине 6 ) прекращено.

В результате анализа состояния информации на шине 5 и входе триггера 2 совершается целенаправленная 4 установка триггера 2 в состояние, которое соответствует на момент сигнала а в промежутке времени tg, Существенно при этом, что общее время, необходимое для произведения. операции запоминающая,в любом случае не превысит удвоенной задержки одного элемента И-НЕ.

Следовательно, введенные в запоминающий элемент И-НЕ и элемент saдержки, который, например, может быть выполнен на двух инверторах, не только устраняют ложное срабатывание триггера 2, но и дозволяют до мийимума сократить время, иеобходи" мое для осуществления операции запоминания.

В случае равенства времени задержки распространения сигналов и t время выборки для sanoмйнания можцо уменьшить до величины, не превышакщей длительности переходного процесса на входах второго триггера.

Таким образом, предложенный элемент обладает повышенной точностью выборки и хранения двоичной информации с обеспечением высокого быстродействия работы запоминающего элемента. Это позволяет ускорить процессы обработки информации в вычислительных комплексах при высокой точности выборки и хранения случайных перно" дических, стационарных или одиночных информационных сигналов, представленных в двоичной форме.

Формула изобретения

Запоминающий элемент, содержащий первый триггер, выход которого соединен с первым входом второго триг гера, выход которого является выходом запоминающего элемента, входы первого триггера подключены соответственно к информационной и управ" ляющей шинам, о т л и ч а ю щ и йс я тем, что, с целью повышения надежности запоминающего элемента, в него введены элемент И-НЕ и элемент задержки, вход которого соединен с первым входом элемента И-НЕ и с первым входом первого триггера, выход которого соединен со вторым входом элемента И-НЕ, второй и третий входы второго триггера. соединены соответственно с выходами элемента

-HE и элемента задержки. е

Источники информации, принятые во внимание при экспертизе

1. Гутииков В.С. Интегральная электроника в измерительных приборах, Л., Энергия 1974, с. 42-43 °

2. Авторское свидетельство СССР

9 479225 кл. 6 11 С 9/00, 1975, (прототип) .

879647

Составитель A. Воронин

Техред Т.Маточка

Корректор М. Шароши

Редактор Н. Коляда

Тираж 648 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 9729/22

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4