Запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗО6РЕТЕН ИЯ . К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Соила Советсиик

Социалистичесиик

Реслублии (t ii879648 (63 ) Дополнительное к авт. саид-ву(22) Заявлено 11.01. 80 (21) 2868897/18-24 с присоединением заявки РЙ— (23) Приоритет 19. 12. 77

Опубликовано 07. 11.81. Бюллетень %41 (Sl)M Кя.

G 11 С 11/00

3Ьеудэрстеэквый квинтет

СССР вЬ делэм вэабретепкй и открытн33 (53) УДК681. 327 (088.8) Дата опубликования описания 09 ° 11.81 (72) Автор изобретения

М. Я. Эйнгорин

Горьковский исследовательский физико-технический институт при Горьковском государственном университете им. Н. И. Лобачевского (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к области запоминающих устройств.

Известно выполненное по системе

ЗД с матричной селекцией

Недостатком этого устройства явля ется большое число селектирующих шин.

Из известных устройств наиболее близким техническим решением к изобретению является ЗД содержащее накопитель, дешифраторы, формирователи им10 пульсов выборки и логические элементы (2).

Это устройство требует большого числа селектырующих шин, соединяющих дешифраторы с накопителем, при хоро1S шем избирающем отношении, что снижает надежность устройства.

Целью изобретения является сокращение числа селектирующих шин соединения дешифраторов с накопителем при

20 заданном объеме накопителя или увеличении объема накопителя при сохране нии числа селектирующих шин, т.е. повьппение надежности ЗУ.

Поставленная цель достигается тем, что в ЗУ, содержащее дешифраторы, накопитель, группы формирователей двухполярных импульсов, группу элементов

НЕ, причем выходы первого дешифратора подключены к одним из входов формирователей двухполярных импульсов, выходы которых соединены с соответствующими входами накопителя, управляемые входы элементов НЕ соединены с управляющим входом устройства, а входы дешифраторов являются адресными входами устройства, введен функциональный преобразователь, входы которого подключены к выходам второго дешифратора, а выходы соединены с другими входами управляемых элементов НЕ, выходы которых подключены соответственно к другим входам формирователей двухполярных импульсов, входящих в одну группу.

При этом целесообразно функциональный преобразователь выполнить в виде преобразователя двоичного кода в кои

40

3 8796

Адомара К-ro порядка (где К ) 4 - елое) .

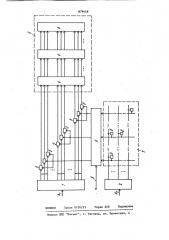

На чертеже изображена функциональная схема предложенного ЗУ, Устройство содержит дешифраторы 1 и 2, накопитель 3, состоящий из К запоминающих матриц 4, группы формирователей двухполярных импульсов 5, группу управляемых элементов НЕ б и функциональный преобразователь 7, со- 10 держащий коммутирующие элементы 8.

Входы преобразователя 7 подключены к выходам дешифратора 2. Одни входы элементов НЕ 6 соединены с управляющим входом устройства, другие входы— с выходами преобразователя 7. Одни входы формирователей S подключены к выходам дешифратора 1, а другие — к выходам элементов НЕ 6.

ЗУ работает следующим образом.

На вход дешифратора 1 подается часть двоичного кода адреса А4, определяющего выбор одной из ячеек в каждой матрице 4. Дешифратор 1 на основе двоичного кода А на своих выходах формирует К ортогональных па.— раллельных адресных кодов, каждый из которых содержит одну единицу и (п-1) нулей (где п — число формирователей

5 в группе и определяет коды, которые поступают на один из входов формирователя 5 и определяют выбор одной из ячеек в каждой запоминающей матрице 4. На вход дешифратора 2 подается вторая часть кода А, который

35 после его преобразования преобразо н вателем ? в код Адомара поступает через управляемые элементы НЕ 6 на другие входы формирователей 5, относящихся к различным ортогональным групрпам. Код А определяет запоминающую матрицу 4, из которой производится селекция по первой части адреса А .

Наличие "1" или "0" на одном входе формирователя 5 определяет полярность выходного сигнала формирова. 45 теля, имеющего активизированный основной вход. Все коды Адомара, кроме одного. имеют К/2 нулей и К/2 единиц, в кодой ортогональной системе активирован один выход, следователь- но, на накопитель 3 поступают k/2 положительных и К/2 отрицательных сигналов по К.п шинам, из которых (n-1) k имеют нулевой выходной сигнал.

Управляющий вход 9 устройства служит для управления инвертированием сигналов, поступающих на другие вхо48 ды формирователей в режимах: "запись или "чтение". п

В случае, если матрицы 4 выполнены на полупроводниковых приборах, например МНОП-транзисторах, формирователи должны иметь два входа: прямой и инверсный..

Технико-экономические преимущества описанного устройства состоят в следующем. Если без функционального преобразователя селектировался объем матрицы 4, равный п или п слов, то с функциональным преобразователем в раз больше, при том же числе шин, соединяющих накопитель с дешифратором или, что то же самое,, сокращено число шин селекции при объеме накопителя К блоков по п или и слов.

Формула изобретения

1. Запоминающее устройство, содержащее дешифраторы, накопитель, группы формирователей двухполярных импульсов, группу элементов НЕ, причем выходы первого дешифратора подключены к одним из входов формирователей двух полярных импульсов, выходы которых соединены с соответствующими входами накопителя, управляемые входы элементов НЕ соединены с управляющим входом устройства а входы дешифраторов являются адресными входами устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, оно содержит функциональный преобразователь, входы которого подключены к выходам второго дешифратора, а выходы соединены с другими входами управляемых элементов НЕ, выходы которых подключены соответственно к другим входам формирователей двухполярных импульсов, входящих в одну группу.

2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что функциональный преобразователь выполнен в виде преобразователя двоичного кода в код Адомара К-го порядка (где К ) 4— целое).

Источники информации, принятые во внимание при экспертизе

1. Огнев И. В. и Шамаев Ю. М. Проектирование запоминающих устройств.

M., "Высшая школа", 1979,, с. 127.

2. Ричардс P. К. Элементы и схемы цифровых вычислительных машин. М., "Иностранная литература"., 1966, с с. 61-80 (прототип).