Устройство для вычисления функции у @ =а @ у @ -1+в @

Иллюстрации

Показать всеРеферат

Союз Советсиин

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ iii881737

l (6I ) Дополнительное к авт. саид-ву (22) Заявлено 16.11.79 (21) 2842070/18 — 24 (5 I ) M. Кл.

G 06 F 7/544 с присоединением заявки ¹â€”

Гоеудорсткнный комнтет

СССР (28) Приоритет

IIo делам нзобретеннй н открытнй

Опубликовано 15.11.81. Бюллетень № 42 (53) УД К681.3 (088.8) Дата опубликования описания 15.11.81 (72) Авторы изобретения

В. И. Жабин, В. И. Корнейчук, В. С. Козак, Ю. В.

А. С. Покаржевский, А. П. Скочко, В. П. Тарасенко (7! ) Заявитель

Киевский ордена Ленина политехнический институт

Великой Октябрьской социалистической революции (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ У A1Yt -1+B

Изобретение относится к вычислительной технике и может найти применение в специализированных цифровых вычислительных устройствах.

Известно устройство, содержащее регистр аргумента, блоки памяти, умножитель и сум- S матор (1) .

Недостатками устройства являются низкие функциональные возможности и низкое быстродействие, 10

Наиболее близким по техническои сущности к предлагаемому является устройство, содержащее и сумматоров коэффициентов, связанных со входами и выходами п регистров суммы и выходами и коммутаторов, имеющих

1S цепи выдачи прямого кода, первыи регистр коэффициента, соединенный со входами первого коммутатора, блок управления, соедятенный с цепями приема кода на регистр суммы (2).

Цель изобретения — повьппение быстродействия.

Поставленная цель достигается тем, что в устройство, содержащее п сумматоров коэффи2 циентов (n — количество вычисляемых значений), и регистров сумм, и коммутаторов, . первый регистр коэффициентов и блок синхронизации, выход которого подключен к управляющим входам регистров сумм, выход первого регистра коэффициентов соединен с первым входом первого коммутатора, выходы коммутаторов подключены к первым входам соответствующих сумматоров коэффициентов, вторые входы которых соединены с выходами соответствующих регистров сумм, первые выходы сумматоров коэффициентов соединены со входами соответствующих регистров сумм, дополнительно введены и — 1 регистров коэффициентов, и регистров переносов, и выходных сумматоров и и дешифратороь, причем второй вход первого коммутатора соединен со входом устройства и с первым входом первого дешифратора, выходы регистров коэффициентов со второго до n-ro соединены с первыми входами соответствующих коммутаторов, управляющие входы регистров переносов соединены с выходом блока синхронизации, вторые входы сумматоров коэффициен881737 4 соответствии с системой переключательных функций

При этом

y. () -к

К тов соединены со входами соответствующих регистров переносов, выходы которых соединены с третьими входами соответствующих сумматоров коэффициентов, выход i-ro дешифратора (i — 1, 2, ..., n-.l) соединен с четвертым входом i-ro сумматора коэффициентов, вторым входом (i+1)-ro коммутатора и первым входом (i+1)-го пешифратора, выход

n-ro дешифратора соединен с четвертым входом и-го сумматора коэффициентов, выходы старших разрядов регистров сумм и переносов соединены с первыми и вторыми входами соответствующих выходных сумматоров, выходы которых соединены с входами соответствующих дешифраторов, выходы которых являются выходами устройства.

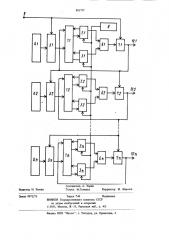

На чертеже представлена блок-схема устройства.

Устройство содержит и сумматоров 11 — 1П коэффициентов, и регистров 2„1 — 2. и сумм, и регистров 3,1 — Зп переносов, и регистров

4,1 — 4. и коэффициентов, и коммутаторов

5,1 — 5,п, и выходных сумматоров 6,1 — 6 ° и, пдешифраторов 7,,1 — 7. и, блок 8 синхронизации, вход 9 устройства, выходы 10,1 — 10, и устройства. Сумматоры 1 и регистры 2 и 3 содержат по (q+2) разрядов (q — разрядность коэффициентов А и В}, причем -ый разряд. регистра суммы 2. i (g — 1, q+2; первыми считаются старшие разряды) соединен со входом с -го и с выходом (ь +1)-го разрядов сумматора li, а 3 -ый разряд регистра переносов 3, i связан со входом p -ro и выходом (Я +2)-ro разрядов сумматора 1. i.

Выходы четырех старших разрядов регистра

2. i и регистра 3, i связаны со входами четырехразрядного выходного сумматора с групповым переносом 6, i, выходы которого подключены ко входам дешифратора 7. i. Первый, второй и третий выходы дешифратора 7. i подключены к выходу 10. i, а также соответственно к цепям выдачи дополнительного, прямого и удвоенного прямого кодов коммутатора 5. i (входы первого коммутатора S подключены ко входной шине 9), а первый выход дешифратора 7. i, кроме того, соединен со входами дешифратора 7. i + 1. Четвертый и пятый выходы дешифратора 7. i связаны со входами первого и второго разрядов сумматора 1, i соответственно. Выходы q-разрядного регистра коэффициентов 4, i подключеныко входам коммутатора 5,1, выходы которого подключены ко входам q младших разрядов сумматора 1i i. Каждый i-й выход блока 8 синхронизации связан с цепями приема кода на регистры 2. i и 3. i.

Дешифратор 7. i содержит логические weменты И, ИЛИ, связанные между собой в

<1 1<1<4. ??„4 ??>

1 1 3 1с йс 4и с с 44

% =

4Ъ с 4 1

4" з с где индексы функций соответствуют размерам выходов дешифратора 7. i, индексы аргументов Я вЂ” номерам разрядов сумматора б.i, Ь вЂ” вход дешифратора 7. i, связанный с пер. вым выходом i — 1-го дешифратора 7, Блок синхронизации 8 содержит и-разрядный сдвиговый регистр и и двухвходовых элементов И. Выход i-го разряда регистра сое.

20 динен с первым входом i-ro элемента И, выход которого является i-м выходом блока синхронизации. Кроме того, вход первого разряда регистра связан с входом логической единицы, цепи сдвига регистра соединены с тактирующим входом, а тактирующий вход связан со вторыми входами элементов И.

Устройство работает по следующему алгоритМу:

В исходном состоянии

30 Na

6) 1

В каждом к-м цикле (К=1 -, ".,и+ 1)

S " = М " <, - ) А,, „) х1 где Ч ХB$7,0,1,%J-- цифра к-го разряда> числа

В исходном состоянии в соответствии с выражением (2) в каждом регистре суммы

2. i записано — В .В регистре коэффициен1

1. тов 4. i записан коэффициент А .. В регистрах

3 переносов записаны нули.

В каждом к-м цикле вычисления происходит сдвиг регистра блока синхронизации, а на вход 9 поступает цифра к-го разряда числа (0 М,, которая с помощью коммутатора (0)

SJ управляет выдачей в младшие разряды

50 сумматора 1.1 содержимого регистра 4.1 таким образом, что в соответствии с выражением (3) на сумматор 1.1 выдается дополнительный код, если цифра У „ равна 1, прямой код, если она равна 1 удвоенный прямой

55 код, если цифра равна 2 и код не выдается, если соответствующая цифра равна нулю. Одновременно с этим выходной сумматор 6, j (j — 1, 2, ..., к) осуществляет суммирование

881737 содержимого четырех старших разрядов регистров суммы 2,j и переносов З,j. Анализируя полученную сумматором 6 ° j сумму, дешифратор 7, j формирует цифру Y которая (И выдается из устройства на выход 10. j u аналогичным образом управляет выдачей кода с регистра 4, j + 1 на сумматор 1. i + 1.

Кроме того, на каждый сумматор 1 j поступают в соответствии с выражением (3) следующие величины: удвоенный код содержимого регистров 2. jи3,,j (2йх 1 ) и код с

<3) выхода дешифратора 7. j 2Ч< „(выдается (4) в два старших сумматора). После окончания переходного процесса сформированный на выходе сумматора 1, j код принимается в виде поразрядных сумм и переносов на регистры суммы 2. j и переносов 3. j.

Для вычисления всех функций Ч„= A) f„ +

+ В„(i = 1, и) с точностью до q цифр необходимо выполнить n + q + 1 циклов вычисления.

Предлагаемое устройство позволяет вычислить результат с разрядностью q за n + q + 1 циклов. Длительность цикла вычисления в предлагаемом устройстве состоит из времени суммирования без распространения переноса, времени срабатывания дешифратора и коммутатора и времени приема кода на регистры

2 и 3. Округляя в сторону увеличения, можно принять ц,, п едл.= < + c*S где ь — время суммирования в одноразряд-. ном сумматоре; — время приема кода на регистр сдЬ (время сдвига).

В известном устройстве длительность цикла состоит из времени суммирования в q-разрядном сумматоре с распространением переноса и времени сдвига, т.е. 1,„и.ь =с Ф t ii,,Можно принять Ь о е, = 0,5 Г, тогда предлагаемое устройство, обладая более широкими функциональными возможностями, дает выигрыш в быстродействии по сравнению с известным в

7и>В n5 Lq < О,Б )

?ФЪ, 1т редл. 2,5 (n+g+q)

Например, при разрядности q = 24 и

n = 3 предлагаемое устройство позволяет вычислять функции Y„â 25,2 раэ быстрее известного.

Формула изобретения

Устройство для вычисления функции

- A„M; „+ B;,ñoät:ðæàùåe .п суммато. ров коэффициентов (и — количество вычисляемых значений), п регистров сумм, п коммутаторов, первый регистр коэффициентов и блок синхронизации, выход которого подключен к управляющим входам регистров

10 сумм, выход первого регистра коэффициентов соединен с первым входом первого коммутатора, выходы коммутаторов подключены к первым входам соответствующих сумматоров коэффициентов, вторые входы которых

15 соединены с выходами соответствующих регистров сумм, первые выходы сумматоров коэффициентов соединены со входами соответ:ствующих регистров сумм, о т л и ч а ющ е е с я тем, что, с целью повышения

20 быстродействия, в него введены и — 1 регистров коэффициентов, прегистров переносов,,и выходных сумматоров и и дешифраторов, причем второй вход первого коммутатора соединен со входом устройства и с первым входом первого дешифратора, выходы регистров коэффициентов со второго до n-ro соединены с первыми входами соответствующих коммутаторов, управляющие входы регистров переносов соединены с выходом блока синхрони30 зации, вторые выходы сумматоров коэффициентов соединены со входами соответствующих регистров переносов, выходы которых соеди нены с третьими входами соответствующих сумматоров коэффициентов, выход i-го дешифратора (i = 1, 2, ... и — 1) соединен с четвертым входом i-го сумматора коэффициентов, вторым входом (i+1)-го коммутатора и первым входом (i+1)-го дешифратора, выход и-го дешифратора соединен с четвертым входом и-ro сумматора коэффициентов, 40 выходы старших разрядов регистров сумм и переносов соединены с первыми и вторыми входами соответствующих выходных сумматоров, выходы которых соединены с входами соответствующих дешифраторов, выходы кото4> рых являются выходами устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР N 575647, кл. G 06 Е 7/38, 1977.

2. Авторское свидетельство СССР N 451088, кл. G 06 F 15/20, 1973 (прототип), 881737

Составитель А. Зорин

Техред М,Гопника

Корректор М, Шароши

Редактор Н. Ромжа

Тираж 748 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий.

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Заказ 9972/73

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4