Микропрограммное устройство управления

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Х АВТОРСИОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 04. 01. 80 (21) 2864123/18-24 с присоединением заявки ¹â€” (23) Приоритет

Опубликовано 15.11.81. Бюллетень № 42

Дата опубликования описания 151181 (51)М. Кл.з

Ст06 F 9/22

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 681. 325 (088. 8) (72) Авторы изобретения

1. "(.. (,/)

В.П.Фролов, С.С.Дьяковский и Г.И. :лащев .. йс: ° ! ( (71) Заявитель (541 МИКРОПРОГРАММНОЕ УСТРОЙСТВО

УПРАВЛЕНИЯ

Изобретение относится к вычислительной технике и может быть использовано при построении цифровых вычислительных машин.

Известно микропрограммное устройство управления, содержащее блок памяти, регистры, схемы приема информации, генератор импульсов, счетчик тактов, дешифратор, формирователь адреса микропрограммных слоев, элементы

И, НЕ 1) .

Недостатком такого устройства является его сложность.

Наиболее близким по технической сущности к изобретению является мик- 15 ропрограммное устройство управления, содержащее блок памяти, регистр адреса, генератор тактовых импульсов, дешифратор кода операций, дешифратор приз наков, триггер условных перехо- 20 дов, триггер совмещения операций, дешифратор адреса, элементы И (2).

Однако этому устройству присуще низкое быстродействие, обусловленное выполнением одного типа микрокоманд за два такта.

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство микропрограммного 30 управления, содержащее два блока элементов И, три дешифратора, регистр адреса, элемент И, блок памяти, генератор тактовых импульсов, информационный регистр, причем управляющий вход регистра адреса соединен с выходом элемента И, информационный выход регистра адреса соединен с информационным входом первого дешифратора, управляющий вход которого соединен с выходом генератора тактовых импульсов, выход первого дешифратора соединен с входом блока памяти, выход которого соединен с информационным входом информационного регистра, первый, второй, третий информационные выходы которого соединены соответственно с входами второго, третьего дешифраторов и с первым входом элемента И, выходы дешифраторов соединены соответственно с первыми входами .первого и второго блоков элементов И, группа выходов второго блока элементов И является группой выходов устройства, второй вход первого блока элементов И является информационным входом устройства, введены два элемента ЗАПРЕТ, причем выход первого блока элементов И соединен с запрещающим входом первого элемента ЗА881750

ПРЕТ,c информационным входом второго элемента ЗАПРЕТ и со вторым входом элемента И, запрещающий вход второго элемента ЗАПРЕТ соединен с четвертым информационным выходом информационного регистра, управляющий вход устройства соединен с информа0ионным входом первого элемента ЗАПРЕТ, выход первого элемента ЗАПРЕТ соединен с информационным входом регистра адреса.

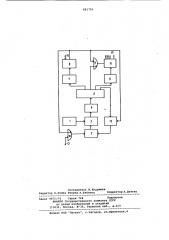

На чертеже представлена блок-схема устройства.

Устройство содержит генератор тактовых импульсов 1, регистр адреса 2, дешифратор 3, блок памяти 4, информационный регистр 5, дешифратор 6, 35 дешифратор 7, блок элементов И 8, элементы ЗАПРЕТ 9 и 10, блок элементов И 11, элемент И 12, входы 13 и

14 устройства и выход 15 устройства.

Устройство работает следующим об- Щ разом.

Микрокоманды делятся на два типа.

В микрокомандах первого типа возможно совмещение по времени выполнения данной элементарной операции и анализа признаков. Разряд совмещения в данной микрокоманде равен, единице.В микрокомандах второго типа элементарная операция может выполняться только при отсутствии анализируемого признака. Разряд совмещения равеннулю. В блоке памяти 4 для микрокоманды любого типа отводится одна ячейка.

Генератор тактовых импульсов 1 вырабатывает сигналы считывания из блока памяти 4. Информация, считанная из блока памяти 4 по адресу, установленному в регистре адреса 2, передается в информационный регистр

5. Если считывается микрокоманда 40 первого типа, то сигнал с выхода разряда совмещения запирает первый элемент ЗАПРЕТ 9 по запрещающему . входу и, независимо от наличия признаков, на выходах 15 формируется сиг- 45 нал элементарных операций, соответствующий коду операции. Одновременно с этим анализируется наличие признаков. При наличии признака сигнал с выхода блока элементов И 8 закрывает gg второй элемент ЗАПРЕТ 10, блокируя прибавленные единицы к содержимому регистра адреса 2, одновременно разрешая, Передачу адреса перехода из адресных разрядов информационного регистра 5 через элемент И 12 в регистр адреса 2. Если признака нет, то к содержимому регистра адреса 2 прибавляется единица через элемент

ЗАПРЕТ 10. При считывании микрокоманды второго типа элемент ЗАПРЕТ 9 d0 не блокируется, поэтому выполнение микрокоманды определяется только наличием или отсутствием признаков.

Если значение признака равно единице, то сигнал с выходов элемента 65

И 8 через открытый элемент ЗАПРЕТ 9 запрещает формирование сигналов элементарных операций на выходах 15, одновременно разрешая передачу в регистр адреса 2 перехода.

При отсутствии признака сигнал запрещения формирования элементарных операций на выходы 15 не поступает, поэтому микрокоманда выполняется как обычно, а к содержимому регистра адреса 2 через открытый элемент ЗАПРЕТ

10 добавляется единица.

Применение изобретения позволяет повысить быстродействие устройства.

Формула изобретения

Микропрограммное устройство управления, содержащее два блока элементов И, три дешифратора, регистр адреса, элемент И, блок памяти, генератор тактовых импульсов, информационный регистр, причем управляющий вход регистра адреса соединен с выходом элемента И, информационный выход регистра адреса соединен с информационным входом первого дешифратора, управляющий вход которого соединен с выходом генератора тактовых импульсов, выход первого дешифратора соединен с входом блока памяти, выход которого соединен с информационным входом информационного регистра, первый, второй и третий информационные выходы которого соединены соответственно с входами второго, третьего дешифраторов и с первым входом элемента И, выход второго и третьего дешифраторов соединены соответственно с первыми входами первого и второго блоков элементов И, группа выходов второго блока элементов И является группой выходов устройства, второй вход первого блока элементов И является информационным входом устройства, о т л и ч а ю щ е е с я тем, что, с. целью повышения быстродействия, устройство содержит два элемента ЗАПРЕТ, причем выход первого блока элементов И соединен с запрещающим входом второго элемента ЗАПРЕТ с информационным входом второго элемента ЗАПРЕТ и со вторым входом элемента

И, запрещающий вход. второго элемента

ЗАПРЕТ соединен с четвертым информационным выходом информационного регистра, управляющий вход устройства соединен с информационным входом первого элемента ЗАПРЕТ, выход первого элемента ЗАПРЕТ соединен с информационным входом регистра адреса.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 416696, кл. 5 06 F 9/16, 1971.

2. Авторское свидетельство СССР

У 463970, кл. 0-06 F 9/16, 1975 (прототип .

Составитель М.Кудряшев

Редактор Н.Ромжа Техред A.Áàáèíåö Корректор А.Дзятко

Заказ 9975/74 Тираж 748 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", r.Óæãîðîä, ул.Проектная,4