Цифроаналоговый микропроцессор

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Реслублнк

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ н>881760 (6! ) Дополнительное к ввт. саид-ву (22) Заявлено 250280 (2! } 2887481/18-24 с присоединением заявки Ио— (23) Приоритет

Опубликовано 151181 Бюллетень Мо 42

Дата опубликования описания 1 11,81 (51)М. Кл.3

G 06 F 15/32

Государственный комитет

СССР но делам изобретений и открытий (53) УДК681. З25 (088.8) (72) Автор изобретения

В.В.Аристов

Институт электродинамики AH Украинской ССР (71) Заявитель (54).ЦИфРОАНАЛОГОВЫЯ МИКРОПРОЦЕССОР

Изобретение относится к вычислительной технике и может быть испольI зовано в цифроаналоговых вычислительных и моделирующих системах.

Известны цифровые микропроцессоры состоящие из цифровых, коммутирующих, запоминающих и арифметикологических блоков и позволяющие эа счет микропрограммирования формировать широкий 0 набор логических и вычислительных функций И .

Основным недостатком цифровых микропроцессоров эа счет последовательного принципа функционирования является малое быстродействие при вычислении сложных функций, например от многих переменных.

Наиболее близким по технической сущности и достигаемому результату к иЗобретению является цифроаналоговое устройство, содержащее управляющий регистр, набор вычислительных и функциональных блоков, коммутатор входов, коммутатор выходов и комму- 25 татор соединений блоков p).

Однако такому устройству присущ большой объем оборудования.

Цель. изобретения — сокращение оборудования. 30

Поставленная цель достигается тем .что в цифроаналоговый микропроцессор содержащий функциональный преобразователь и блок вычислений вектора, дополнительно введены суммирующий усилитель и блок формирования уровня напряжения, причем первый вход микропроцессора соединен с первыми входами блока вычислений вектора и суммирующего усилителя, первый и второй выходы блока вычислений вектора являются соответственно первым и вторым выходами микропроцессора третий выход которого соединен с выходом сум мирующего усилителя, со вторыми входами функционального преобразователя и блока вычислений вектора и с входом блока формирования уровня напряжения первый выход блока вычислений Вектора соединен со вторым входом суммирую щего усилителя, третий вход которого соединен с выходом функционального преобразователя и четвертым выходом микропроцессора,. второй вход которого соедйнен с управляющими входами суммирующего усилителя и функционального преобразователя и блока вычислений вектора, третий вход которого соединен с выходом блока формирования уровня напряжения.

881760

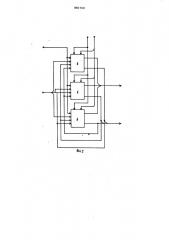

Кроме того, блок вычислений вектора содержит три решающих узла, причем первый и второй входы каждого решающего узла соединены с первым и вторым входами блока соответственно, третий вход каждого решающего узла соединен с третьим входом блока,. четвертый вход каждого решающего узла соединен с управляющим входом блока, первые выходы решающих узлов соединены с первым выходом блока, пятые входы первого и третьего решающих узлов соединены со вторым выходом второго решающего узла, пятый вход второго и шестой вход третьего решающих узлов соединены с выходом первого решающего узла, шестые входы первого и второго решающих узлов соединены с выходом третьего рещающего узла, вторые выходы решающих узлов соединены со вторым выходом блока.

Каждый решающий узел содержит три 2Q сумматора, умножитель, три коммутатора, причем первые входы первого и второго сумматоров соединены с третьим входом узла, вторые входы первого и второго сумматоров соединены 25 с выходом умножителя, первый вход умножителя соединен с первым входом узла, второй вход умножителя соединен с выходом третьего сумматора, первый, второй и третий входы третьего сумматора соединены с выходами первого и третьего коммутаторов соответственно, первый, второй входы первого и третьего коммутаторов соединены со вторым и четвертым входами узла соответственно, первый, второй входы второго коммутатора соединены с выходом второго сумматора, третьи входы коммутаторов соединены с пятым входом узла, четвертые входы коммутаторов соединены с шестым входом уз- 40 ла.

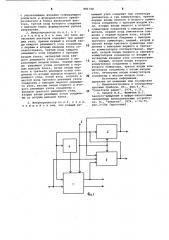

На фиг.1 изображена блок-схема предлагаемого цифроаналогового микропроцессора; на фиг.2 — блок-схема вычислений вектора, на фиг.3 — функциональная схема решающего узла блока вычислений вектора.

Устройство содержит блок 1 вычислений вектора, суммирующий усилитель

2, функциональный преобразователь 3 и блок 4 формирования уровня напряжения, вход 5 микропроцессора.

Блок вычислений вектора 1 содержит решающие блоки б, которые содержат три сумматора 7-9, узел умножения 10 и т и коммутатора 11.

Последовательность работы устройства состоит в задании кода операций в виде комбинаций высоких и низких уровней напряжения по входу 5, задании в виде напряжений на первый и вто-60 рой входы устройства соответственно значений переменных, являющихся компонентами вектора, и съем результатов в виде напряжений, формируемых на всех четырех выходах устройства. 65

Код операций характеризуется знаа м ° - а (° . мм е ++)$5>Vxw 9н бхай где а ; и ; — компоненты матриц A и 8 соответственно.

Код операций задается на входы узлов б блока 1, блока 2 и функционального преобразователя 3. В зависимости от кода коммутатор 11 решающего узла б запрещает или разрешает прохождение прямого или инверсного сигнала со входа или второго выхода блока 1 на соответствующий вход сумматора 9. Сигнал в виде уровня напряжения, подаваемый с выхода блока 4 на четвертые входы всех коммутаторов 11, одновременно инвертирует напряжение на всех входах сумматоров 9 решающих узлов 6..

Составляющие кода операций, поступая на входы блока 2, разрешают или блокируют прохождение напряжения через блок 2, обуславливая тем самым наличие или отсутствие информационных связей в блоке 2. Кроме того, часть кода операций поступает на управляющий вхол функционального преобразователя 3, поэтому на выходе преобразователя 3 в зависимости от этого кода формируется напряжение, изменяющееся по закону А t,h.

Зтот базовый вариант только двух функций от одной переменной позволяет формировать множество, исчисляемое сотнями и более иных нелинейных функций, в том числе и от многих переменных.

Применение изобретения позволяет сократить объем оборудования.

Формула изобретения

1.:Дифроаналоговый микропроцессор, содержащий функциональный преобразователь и блок вычислений вектора, отличающийся тем, что, с целью сокращения оборудования, он содержит суммирующий усилитель и блок формирования уровня напряжения, причем первый вход микропроцессора соединен с первыми входами блока вычислений вектора и суммирующего усилителя, выходы блока вычислений вектора являются соответственно первым и вторым выходами микропроцессора, третий выход микропроцессора соединен с выходом суммирующего усилителя, со вторыми входами функционального преобразователя и блока вычислений вектора и с входом блока формирования уровня напряжения, первый выход блока вычислений вектора соединен со вторым входом суммирующего усилителя, третий вход которого соединен с выходом функционального преобразователя и четвертым выходом микропроцессора, второй вход микропроцессора соединен

В81760 с управляющими входами суммирующего усилителя и функционального преобразователя и блока вычислений вектора, третий вход которого соединен с выходом блока формирования уровня напряжения.

2. Микропроцессор по п.1, о т л и ч а ю шийся тем, что блок вычислений векторов содержит три решающих узла, причем первый и второй входы каждого решающего узла соединены с первым и вторым входами блока соответственно, третий вход каждого решающего узла соединен с третьим входом блока, четвертый вход каждого решающего узла соединен с управляющим входом блока, первые выхо- 15 ды решающих узлов соединены с первым выходом блока, пятые входы первого и третьего решающих узлов соединены со вторым выходом второго решающего узла, пятый вход .второго и 29 шестой вход третьего решающих узлов соединены с выходом первого решающего узла, шестые входы первого и второго решающих узлов соединены с выходом тРетьего решающего узла, 5 вторые входы решающих узлов соединены со вторым выходом блока.

3. Микропроцессор по п.1, о т л ич а ю шийся тем, что каждый решающий узел содержит три сумматора умножитель и три коммутатора, причем первые входы первого и второго сумматоров соединены с третьим входом узла, вторые входы первого и второго сумматоров соединены с выходом умножителя, первый вход умножителя соединен с первым входом узла, второй вход умножителя соединен с выходом третьего сумматора, первый, второй и третий входы третьего сумматора соединены с выходами первого и третьего коммутаторов соответственно, первый, второй входы первого и третьего коммутаторов соединены со вторым и четвертым входами узла соответственно, первый, второй входы второго коммутатора соединены с выходом второго сумматора, третьи входы коммутаторов соединены с пятым входом узла, четвертые входы коммутаторов соединены с шестым входом узла.

Источники информации, принятые во внимание при экспертизе

1. Микроэлектроника и полупроводниковые приборы. Сб., вып.4, М., "Советское радио", 1979, с.11.

2. Смолов В.Б., Фамичев В.С.

Аналого-цифровые и цифро-аналоговые нелинейные вычислительные устройства. Л., "энергия", 1974, с.74-75, рис.3-10а (прототип).

881760

Составитель М.Кудряшев

Техред А.Бабинец Корректор М.Шароши

Редактор Н.Ромка.

Филиал ППП "Патент", r.Óàãîðîä, ул.Проектная,4

Заказ 9975/74 Тираж 748 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5