Устройство для моделирования запаздывания релейных систем

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ (u)881771 (61) Дополнительное к авт. свид-ву (22) Заявлено 080280 (21) 2881016(18-24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 15.1181 бюллетень № 42

Дата опубликования описания 151181 (51) . }(л 3

G 06 G 7/25

Государственный комитет

СССР но делам изобретений н открытий (53) УДК 681 333 (088. 8) (72) Автор изобретения

Я.Н. Нефедьев

t

Научно-исследовательский и экспериментальйий-институт автомобильного электрооборудования и автоприборов (71) Заявитель (54) УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ЗАПАЗДЫВАНИЯ

РЕЛЕИНЫХ СИСТЕМ

Изобретение относится к электрон-т ной вычислительной технике, в частности к аналоговому моделированию запаздывания таких релейных систем,как электромагнитные клапаны и т.п.

Известно устройство для моделирования запаздывания релейных систем, которое содержит электронные блоки интегрирования, дифференцирования, суммирования, перемножения, воспроизведения нелинейных функций и пороговые элементы. Оно предназначено для изучения путей усовершенствования структуры релейной системы (1) ..

Однако для нужд воспроизведения ее функций в составе иных комплексных объектов такого рода устройства излишне сложны.

Наиболее близким к изобретению является устройство для моделирования 2О релейных систем, содержащее интегратор, выход которого подключен ко входу порогового элемента. Для воспроиз ведения постоянства запаздывания оно содержит ряд логических блоков и ключей, связывающих между собой входы и выходы интегратора и порогового элемента j2) .

Недостатком этого устройства является его сложность.

Цель изобретения — упрощение устройства.

Указанная цель достигается тем, что в устройство для моделирования запаздывания релейных систем, содержащее интегратор, выход которого подключен ко входу порогового элемента, введен блок дифференцирования, выход которого подключен к первому входу интегратора, второй вкОд которого является входом устройства, а выход порогового элемента соединен со входом блока дифференцирования и является выходом устройства.

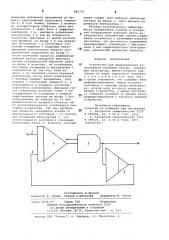

На чертеже представлена схема устройства для моделирования запаздывания релейных систем.

Устройство содержит интегратор 1, пороговый элемент 2, выход которого является выходом устройства, а вход соединен с выходом интегратора 1, блок 3 дифференцирования подключен выходом ко входу 4 интегратора 1, а входом — к выходу порогового элемента 2. Входом устройства является второй вход 5 интегратора 1.

Устройство работает следующим образом.

На включение напряжения на вход 5 интегратор 1 отвечает линейным уве881771

Формула изобретения

СоСтавитель Е.Фролов

Редактор Н. Ромжа Техред C.Ìèãóíoâà Корректор М. Коста

Заказ 9976/75 Тираж 748 Подписное

ВНИИПИ 1осударственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 личением выходного напряжения до момента срабатывания порогового элемента 2, В этот момент элемент 2 включает положительную обратную связь для интегратора 1 через блок 3 дифференцирования, т.е. выходное напряжение интегратора 1 в той же полярности полностью приложено (с малой постоянной времени) ко входу 4 и тем переводит интегратор 1 в ус ойчивое состояние насыщения с заданным запаздыванием относительно момента возникновения напряжения на входе 5..

После окончания процесса дифференци- рования фронта выходного импульса сигнал положительной обратной связи на входе 4 исчезает, но устойчивое состояние насыщения в интеграторе 1 сохраняется до тех пор, пока ко входу 5 не приложат сигнал обратной полярности. После этого интегратор

1 линейно снижает напряжение, подводимое к пороговому элементу 2, и возвращается в исходное состояние аналогично изложенному. Выходной сигнал устройства исчезает также с запаздыванием по отношению к моменту переключения сигнала на входе 5.Это запаздывание не зависит ни от продолжительности входного сигнала, ни от продолжительности устойчивого состояния устройства, так как переходные процессы начинаются всегда от фиксированного состояния — от состояния насыщения интегратора 1, что обеспечивается наличием и укаэанным включением блока 3. Величину запаздывания задают либо выбором амплитуды сигнала на входе 5„ либо выбором параметров интегратора 1.

Технико-экономическая эффективность изобретения состоит в ускорении оборудования рабочего места исследователя комплексных систем,содержащих устройства с релейными характеристиками, что достигнуто упрощением моделирующего устройства с обеспечением в нем характеристики запаздывания, адекватной реальному процессу.

15 Устройство для моделирования запаздывания релейных систем, содержащее интегратор, выход которого подключен ко входу порогового элемента, о т л и ч а ю щ е е с я тем, что, с целью упрощения, оно содержит блок .дифференцирования, выход которого подключен к первому входу интегратора, второй вход которого является входом устройства, а выход порогового элемента соединен со входом блока дифференцирования и является выходом устройства.

Источники информации, принятые во внимание при экспертизе

Зо 1. Авторское свидетельство СССР

Р 409246, кл. G 06 G 7/62, 1974, 2. Авторское свидетельство СССР

9 389526, кл. G 06 G 7/62, 1973 (прототип).