Динамический элемент памяти

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

<1881859 (61) Дополнительное к авт. свмд-ву

<я)м. к (22) Заявлено 13.1279 (21) 2850681/18-24 с присоединением заявки ¹ (23) Приоритет

С 11 С 11/40

Государственный комитет

СССР по делам изобретений н открытий

Опубликовано 1511.81, Бюллетень № 42

Дата опубликования описания 15. 11. 81 (53) УДК 681. 3 27. 67 (088. 8) (72) Автор изобретения

Г.И,Фурсин

Московский ордена Трудового Красного Знамени физикотехнический институт (71) Заявитель (54 ) ДИНАМИЧЕСКИЙ ЭЛЕМЕНТ ПАМЯТИ

Изобретение относится к автоматике и вычислительной технике.

Известны различные варианты динамических элементов памяти, которые за счет наличия распределенной памяти динамического типа позволяют осуществлять ассоциативную и параллельную обработку информации. Динамический принцип обработки информации при этом позволяет резко повысить помехозащищенность вычислительных устройств на основе укаэанных элементов (1).

Наиболее близким по технической сущности к предлагаемому является динамический элемент памяти, содержащий последовательно соединенные транзисторы п-р-п-типа, информационные шины, входные и выходные шины и шину нулевого потенциала (2) .

Однако известный элемент характеризуется недостаточной надежностью.

Цель изобретения — повышение надежности элемента памяти.

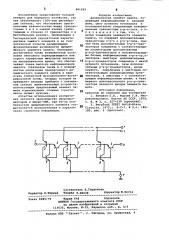

Поставленная цель достигается тем, что динамический элемент памяти содержит дополнительные транзисторы

n-p-и-типа и р-п-р-типа, причем базы дополнительных п-р-и-транзисторов соединены с соответствующими коллекторами дополнительных р-и-р-транэисторов и соответствующими базами информационных п-р-п-транзисторов, эмиттеры дополнительных и-р-п-транзисторов соединены с шиной нулевого потенциала, базы дополнительных р-п-р-транзисторов, кроме первого, подключены к эмиттерам соответствующих информационных транзисторов, а

10 эмиттеры — к соответствующим инфорМационным шинам, а база первого дополнительного р-п-р-транзистора явля ется входом элемента памяти.

Динамический элемент памяти работает следующим образом.

При подаче сигнала положительной полярности на шину 2 происходит включение (насыщение) всех транзисторов и последовательное перемещение сиг20 нала к шине 4, время задержки распространения сигнала фиксировано, не зависит ни от коэффициентов объединения по входу и разветвления по выходу, ни от изменения температуры (в рабочем диапазоне) и обратно пропорционально частоте импульсов питания. Отсутствие влияния выхода на вход (т.е. паразитной обратной связи) приводит к дополнительному повышению помехоустойчивости.

881859

Составитель В.Гордоиова

Редактор Л.Тюрина Техред З.фанта . Корректор М.Коста

Тираж 648 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий .

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 9985/79 филиал ППП Патент, r. Ужгород, ул. Проектная, 4

Изобретение представляет большой интерес для народного хозяйства, так как обеспечивает 100%-ную регенерацию сигнала, что обусловлено оригинальными взаимосвязями между транзис.торами 5 и 6 в каждой ячейке.(работающими в отличие от транзистора 3 в бистабильном режиме), приводящими к гистерезисной передаточной характеристике каждого элемента и за счет логической полноты расширяющими функциональные возможности предложенного элемента памяти. Последнее достигается также возможностью остановки несколько перекрывающихся или строго парафазных импульсов питания на неограниченное время, что обеспечивает очень высокую информационную емкость (связанную также и с возможностью реализации предлагаемого динамического элемента памяти в виде очень компактной функционально-интегрированной схемы, площадь которой не превышает площадь приборов с плазменной связью) вычислительных устройств, использующих предлагаемый элемент памяти и реализующих.сложные (практически любые) функции.

Областью использования изобретения является производство микропроцессоров и микро-3ВМ, где из-за особенностей предложенного элемента осуществляется ассоциативная и параллельная обработка информации, Формула изобретения

Динамический элемент. памяти, содержащий информационные и входные шины, шину нулевого потенциала и последовательно соединенные информа" ционные транзисторы п-р-п-типа, о тл и ч а ю шийся тем, что, с целью повышения надежности элемента памяти, он содержит дополнительные транзисторы и-р-и и р-п-р-типа, причем базы дополнительных и-р-и-транзисторов соединены с соответствующи. ми коллекторами дополнительных р-и-р"транзисторов и соответствующими базами информационных п-р-л-тр..нзисторов, эмиттеры дополнительных

15 и-р-и-транзисторов соединены с шиной нулевого потенциала, базы дополнительных р-п-р-транзисторов, кроме первого, .подключены к эмиттерам со,ответствующих информационных тран26 эисторов, а эмиттеры — к соответствующим информационным шинам, а база первого дополнительного р-п-р-транзистора является входом элемента памяти.

Источники инФормации, принятые во внимание при экспертизе

1. Векшина Е.В °, Фурсин Г.И. Микроэлектроника. Изд-во АН СССР, 1979, т. 8, М 3, с. 227-239 (прототип).

2. Berg9und XEEEX Solid-State

Зо Circuits, 1972, ". $-С-7, Р 2,с. 180185, рис. 2 (прототип) .