Устройство для контроля блоков постоянной памяти

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (п)881874

ИЗОБРЕТЕНИЯ

Союз Советски и

Соцнапнстнческни

Респубики

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву(22)Заявлено 18.06.79 (21) 2794982/I8-24 (5l)lN. Кл. с присоединением заявки МG 11 С 2.9/00

Гоеудврстееиый комитет

СССР (23) ПриоритетОпубликовано 15, 11. 81. Бюллетень М 42

Дата опубликования описания 17. 11т-.-84 ио делан иэебретеиий и открытиЯ (53) УДК 68! . 327. . 6(088.8) (72) Авторы изобретения

Г.А. Бородин и В.М. Константиновский т (71) Заявитель

I (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ

ПОСТОЯННОЙ ПАМЯТИ

Изобретение относится к вычислительной технике, в частности к устройствам для контроля блоков постоянной памяти.

Известно устройство для контроля блоков постоянной памяти, содержащее блок управления, соответствующие выходы которого соединены со входами блока постоянной памяти, сумматоравычитателя, блока установки контрольных чисел, блока сравнения (1) . l0

Недостатком известного устройства является низкая надежность контроля из-за образования единиц переполнения или заема, которые, никак не учиты15 ваются.

Наиболее близким техническим решением к изобретению является устройство для контроля, содержащее сумматор, первый вход которого соединен с первым выходом блока управления., а второй — с выходом контролируемого блока постоянной памяти, первый вход кото1 рого соединен со вторым выходом блока управления, а второй — с первым выходом блока задания циклов суммирования, второй выход которого соединен с первым входом блока управления, а вход — с третьим выходом блока управления, четвертый выход блока управления соединен со входом блока установки контрольных чисел, а пятый выход — с первым входом блока сравнения, второй вход которого соединен с выходом блока установки контрольных чисел, а выход — со вторым входом блока управления. Проверяемый блок постоянной памяти, кроме контролируемых чисел, дополнительно хранит контрольные константы, с помощью которых осуществляется контроль (2).

Недостатком данного устройства является необходимость хранения большого количества контрольных чисел в блоке памяти, что уменьшает полезный объем памяти и увеличивает вероятность появления ошибки в самих

881874

50 контрольных словах, что уменьшает надежность проведения контроля.

Цель изобретения — повышение надежности устройства.

Поставленная цель достигается 5 тем, что в устройство для контроля блоков постоянной памяти введены формирователь контрольных разрядов по модулю и коммутатор, при этом первый вход формирователя контроль- 10 ных разрядов по модулю соединен с выходом сумматора, второй вход — с шестым выходом блока управления, а выход — с первым входом коммутатора, второй вход которого соединен с седьмым выходом блока управления, третий вход — с третьим выходом блока задания циклов суммирования, а выход — с третьим входом блока сравнения. 20

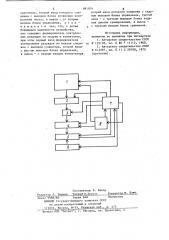

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит контролируемый блок постоянной памяти 1, сумматор 2, чормирователь контрольных разрядов по модулю 3, коммутатор 4, блок сравнения 5, блок установки контрольных чисел 6, блок управления 7, блок задания циклов суммировайия 8.

Устройство работает следующим образом.

При подаче на вход блока постоянной памяти 1 кода адреса импульса запроса из блока управления 7 и сигна.— ла, определяюшего адреса слов, ко35 торые просуммированы в очередном цикле из блока задания циклов суммирования 8, числа считываются и суммируются в сумматоре 3. После того, как все числа, подлежащие суммированию

40 в очередном цикле, обработаны, по сигналам управления, поступающим из блока управления 7, производится определение контрольных разрядов в формирователе контрольных разрядов

45 по модулю 3 и запись из через коммутатор 4 в соответствующие разряды блока сравнения 5, адреса которых задаются блоком задания циклов суммирования 8 и управляются через ком- . мутатор 4. Сумматор 2 после этого обнуляется по сигналу из блока управления 7 и начинается следующий цикл суммирования. После заполнения всех разрядов регистра блока сравнения 5 в нем производится сравнение полученного кода с контрольным числом, поступающим из блока установки контрольных чисел 6 по команде из блока управления 7, куда не поступает результат операции сравнения.

Таким образом, применение предлагаемого изобретения позволяет реализовать поставленную задачу контроля и хранить при этом значительно меньше контрольных чисел в блоке памяти, что увеличивает полезный объем блока памяти и увеличивает надежность хранения контрольной информации, поскольку вероятность возникновения ошибки в большом количестве контрольных чисел больше, чем в меньшем. Известно, что с помощью контрольных разрядов по любому модулю (вычета числа) можно определить ошибки в этом числе, следовательно, несколько контрольных разрядов позволяют выполнить функцию определения ошибки, ка-. кая в известном устройстве выполняется с помощью полноразрядного контрольного числа. Пусть используются формирователи контрольных разрядов по модулю А. Тогда количество контрольных разрядов равно k=log<(A+1).

Если разрядность чисел, хранимых в блоке памяти М, то это позволяет в

М/K раз уменьшить количество контроль ных чисел и во столько же раз уменьшить вероятность возникновения ошибки в них. Аппаратные затраты при этом невелики, использоваться устройство контроля может для контроля нескольких блоков долговременной памяти, что еще более увеличивает преимущества от применения предлагаемого устройства, которые позволяют повысить надежность контроля блоков постоянной камеры.

Формула изобретения

Устройство для контроля блоков постоянной памяти, содержащее сумматор, первый вход которого соединен с первым выходом блока управления, а второй — с выходом контролируемого блока постоянной памяти, первый вход которого соединен со вторым выходом блока управления, а второй — с первым выходом блока задания циклов суммирования, второй выход которого соединен с первым входом блока управления, а вход — с третьим выходом блока управления, четвертый выход блока управления соединен со входом блока установки контрольных чисел, а пятый выход — с первым входом блока

5 88 сравнения, второй вход которого соединен с выходом блока установки контрольных чисел, а выход — со вторым входом блока управления, о т л и— ч а ю ш е е с я тем, что, с целью повышения надежности устройства, оно содержит формирователь контрольных разрядов по модулю и коммутатор, при этом первый вход формирователя контрольных разрядов по модулю соединен с выходом сумматора, второй входс шестым выходом блока управления, а выход — с первым входом коммутатора, 1874 6 второй вход которого соединен с седьмым выходом блока управления, третий вход — с третьим выходом блока задания циклов суммирования, а выход— с третьим входом блока сравнения.

Источники информации, принятые во внимание при экспертизе

Авторское свидетельство СССР о 0- 135105, кл. G 06 F 11/12, 1960.

2. Авторское свидетельство СССР

11- 612287, кл. G 11 С 29/00, 1975 (прототип).

Составитель В. Вакар

Редактор Л. Тюрина Texpeg О.Легеза

Корректор М. Пожо

Подписное

Заказ 9986/80 Тираж 648

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035 Москва, Ж-35д Раушская наб. д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4