Устройство тактовой синхронизации регенератора радиоканала

Иллюстрации

Показать всеРеферат

()882012

Союз Советскми

Соцмалмстмческмк

Реслублмк

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1

> (61) Дополнмтельмое к авт. свмд-ву (22) Заявлено 15.02.80 (21) 2889784/18-09 с присоединением заявки М (23) Прморнтет— (5I)M. Кл.

Н 04 L 7/08

3всуяарстаеиый камитет

СССР

Io делам изебретеиий и открытий (53) УД К 621.394. .662 (088.8) Опубликовано 15.11.81. Бюллетень № 42

Дата опубликования описания 15.11.81 (72) Авторы изобретения

А. Е. Красковский и Ю. А. Липовецкий

Ленинградский ордена Ленина институт инженеров железнодорожного транспорта им. акад. В, Н. Образцова (71) Заявитель (54) УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ

РЕГЕНЕРАТОРА РАДИОКАНАЛА

Изобретение относится к радиотехнике и может использоваться в аппаратуре передачи данных, в частности в регенераторах радиоканала.

Известно устройство тактовой синхронизации регенератора радиоканала, содержащее последовательно соединенные опорный генератор, блок компенсации расхождения частот, управляющий элемент, основной делитель, формирователь временных эон, блок селекции, фазовый дискриминатор и блок усреднения, выходы которого под- О ключены ко входам блока компенсации расхождения частот н управляющего элемента, а также блок коммутации, блок управления и последовательно соединенные блок вьщеления фронтов и блок вьщелення одного фронта эа такт, при этом второй и третий выходы опорного генератора подключены соответственно ко входу блока выделения фронтов н второму входу фазового дискриминатора, к третьему входу которого н второму входу блока выделения одного фронта за такт подключен второй выход основного делителя, а выходы блока управления подключены к .второму и третьему входам блока селек цин, третьему и четвертому входам блока усреднения (11.

Однако известное устройство имеет низкую помехоустойчивость., Цель изобретения — повышение помехоустойчивости.

Для этого в устройство тактовой синхронизации регенератора радиоканала, содержащее последовательно соединенные опорный генератор, блок компенсации расхождения частот, управляющий элемент, основной делитель, формирователь временных зон, блок селекции, фазовый дискриминатор и блок усреднения, выходы которого подключены ко входам блока компенсации расхождения частот и управляющего элемента, а также блок коммутации, блок управления ° и последовательно соединенные блок выделения фронтов и блок выделения одного фронта эа такт, при этом второй и третий выходы опорного генератора подключены соответственно ко входу блока вьщеления фронтов и второму входу фазового дискриминатора, к третьему входу которого и второму входу блока выделения одного фронта за такт подключен второй вы88201

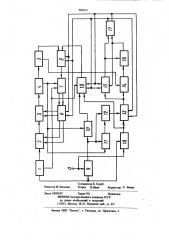

40 решающий блок 14, интегратор 15, формирователь 16 сигнала потери синхронизма, блок 17 управления, асинхронный интегральный приемник 18, блок 19 коммутации, 45

В блоке 9 выделени фронтов осуществляется дискретизация временного положения фронл. тов входного сигнала, для чего на один из входов блока 9 поступает сигнал с выхода опорного генератора 1. Выделенные фронты попадают на вход блока 10 выделения одного фронта за такт, с выхода которого они в синхронном режиме через блок 19 коммутации поступают на вход блока 8 селекщ1и. В указанном режиме блок 8 осуществляет селекцию фрон- ы тов входного сигнала по величине краевых искажений, т.е. на подстройку поступают лишь

50 ход основного делителя, а выходы блока управления подключены к второму и третьему входам блока селекции, третьему и четвертому входам блока усреднения, введены последовательно соединенные асинхронный интегральный приемник, ключ, решающий блок и формирователь сигнала потери синхронизма, а также интегратор и последовательно соединенные анализатор зашумленного сигнала и блок памяти, к второму входу которого, объединенному с первым входом анализатора зашумленного сигнала, подключен выход блока выделения фронтов, а выход блока памяти подключен к второму входу ключа, к третьему и четвертому входам которого, а также к первым и вторым входам интегратора и блока коммутации подключены выходы блока управления, к первому входу которого и второму входу формирователя сигнала потери синхронизма подключен выход интегратора, к третьему входу которого подключен выход ключа, а к четвертому входу интегратора и второму входу блока управления подключен выход формирователя сигнала потери синхронизма, при этом к третьему, четвертому и пятому входам блока коммутации подключены соответственно третий выход опорного генератора, выход блока выделения одного фронта за такт и выход асинхронного интегрального приемника, первый и второй входы которого объединены с соответствующими входами блока выделения фронтов.

На чертеже представлена структурная элект- рическая схема предложенного устройства.

Устройство тактовой синхронизации регенератора радиоканала содержит опорный генератор 1, блок 2 компенсации расхождения частот, управляющий элемент 3, основной делитель 4, формирователь 5 временных зон, блок 6 усреднения, фазовый дискриминатор 7, блок 8 селекции, блок 9 выделения фронтов, блок 10 выделения одного фронта за такт, анализатор 11 зашумленного сигнала, блок 12 памяти, ключ 13, фронты, попавшие в зону доверительного интер1О

2 4 вала, которая формируется в формирователе 5 временных зон и поступает на другой вход блока 8 селекции. В режиме поиска состояния синхронизма фронты входного сигнала поступают на подстройку, минуя зону доверительного интервала.

Подстройка частоты опорного генератора 1 при фазовом рассогласовании осуществляется косвенным способом с помощью управляющего элемента 3, на вход которого в синхронном режиме поступают усредненные импульсы добавления и вычитания с выхода блока 6 усреднения. В режиме поиска состояния синхронизма импульсы добавления и вычитания, вырабатываемые фазовым дискриминатором 7, поступают на управляющий элемент 3 без усреднения. Блок 2 компенсации расхождения частот выполняет операцию компенсации расстройки частоты опорного генератора 1 относительно частоты входного сигнала, т.е. сводит к нулю статическую ошибку синхронизации.

В режиме поиска синфазного состояния фронты сигнала поступают на подстройку и анализ

I состояния системы синхронизации с выхода асинхронного интегрального приемника 18, который выполняет функцию преобразования дроблений сигнала в краевые искажения. Полезный сигнал поступает на вход асинхронного интегрального приемника 18, а на его выходе осуществляется дискретизация временного положения фронтов преобразованного сигнала, для чего на один из его входов подается сигнал с выхода опорного генератора 1. Выделенные фронты поступают через блок 19 коммутации на подстройку, а через ключ 13 на вход интегратора 15, в котором для сокра|цения времени поиска состояния синхронизма включен малый коэффициент интегрирования.

При наличии сигнала на выходе интегратора 15 с помощью блока 17 управления производится включение дополнительных делителей импульсов подстройки в блоке 6 усреднения, включение действия зоны доверительного интервала в блоке 8 селекции. При этом также включается большой коэффициент интегрирования в интеграторе 15 и подключаются анализатор 11 зашумленного сигнала и блок 12 памяти„а на подстройку проходят через блок 19 коммутации фронты с выхода блока 10 выделения одного фронта за такт. Одновременно сигнал с выхода интегратора 15 обнуляет формирователь 16 сигнала потери синхронизма. Действие асинхронного интегрального приемника 18 осуществляется только в режиме поиска синхронизма. При этом в блоке 19 коммутации осуществляется корректировка фазы смещенных в процессе преобразования в асинхронном интегральном приемнике 18 фронтов входного сигнала.

882012

В синхронном режиме для исключения формирования ложного сигнала потери синхронизма с помощью анализатора 11 зашумленного сигнала и блока 12 памяти определяется качество входного ситнала, Действие блока 12 памяти основано на запоминании количества фронтов в одном тактовом интервале, т.е. в интервале между стробимпульсами, расположенными в середине относительно элементарной посылки.

Если их количество равно двум (или более), io то анализатор 11 зашумленного сигнала, вырабатывающий сигнал на выходе с приходом второго фронта в укаэанном интервале, обнуляет интеграторы блока 12 памяти, При этом полностью исключается возможность формирования ложных импульсов преобладания в синхронном режиме.

При действии на вход устройства тактовой синхронизации (УТС) сплошного шума в тактовом интервале формируется большое количество фронтов (более одного). Но через ключ 13 они не проходят за счет действия анализатора

11 и, следовательно, не формируется сигнал потери синхронизма, что особенно важно во время перестройки рабочих частот передатчиков и приемников радиолинии.

Признаком отсутствия состояния синхронизма является наличие преобладания фронтов входного сигнала в одной половине временной зоны анализа, поступающей на вход решающего блока 14 с другого выхода формирователя 5 временных зон. В решающем блоке 14 происходит определение фазового положения.анализируемых фронтов, В формирователе 16 сигнала потери синхронизма производится выделение импульсов преобладания и их усреднение. При наличии на выходе формирователя 16 сигнала потери синхронизма с помощью блока 17 управления производится отключение действия зоны временного доверительного интервала в блоке 8 селекции и дополнительных делителей в

»локе 6 усреднения. Интегратор IS обнуляется, и включается малый коэффициент интегрирования, также отключается анализатор 11 зашумленного сигнала и блок 12 памяти, а на подстройку (через блок 19 коммутации) и анализ 45 (через ключ. 13) поступают фронты с выхода асинхронного интегрального приемника 18, Таким образом, предложенное устройство по сравнению с известным имеет следующие преимущества: обеспечивает оптимальный алгоритм определения синфазного и несинфазного состояния системы синхронизации в условиях аддитивных и мультипликативных помех, высокую цикловую устойчивость при наличии в канале постоянных преобладаний, превышающих значе- ы ние зоны временного доверительного интервала, универсальность определения режимов работы тактовой синхронизации независимо от типа. фазового дискриминатора.

Реализация этих положений позволяет существенно повысить помехоустойчивость и пропускную способность канала связи.

Формула изобретения

Устройство тактовой синхронизации регенератора радиоканала, содержащее последовательно соединенные опорный генератор, блок компенсации расхождения частот, управляющий элемент, основной делитель, формирователь временных эон, блок селекции, фазовый дискриминатор и блок усреднения, выходы которого подключены ко входам блока компенсации расхождения частот и управляющего элемента, а также блок коммутации,.блок управления и последовательно соединенные блок выделения фронтов, и блок выделения одного фронта за такт, при этом второй и третий выходы опорного генератора подключены соответственно ко входу блока выделения фронтов и второму входу фазового дискриминатора, к третьему входу которого и второму входу блока выделения одного фронта за такт подключен второй выход основного делителя, а выходы блока управления подключены к второму и третьему входам блока селекции, третьему и четвертому входам блока усреднения, о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости, введены последовательно соединенные асинхронный интегральный приемник, ключ, решающий блок и формирователь сигнала потери синхрониэма, а.также интегратор и последовательно соединенные анализатор зашумленного сигнала и блок памяти, к второму входу которого, объединенному с первым входом анализатора зашумленного сигнала, подключен выход блока выделения фронтов, а выход блока памяти подключен к второму входу ключа, к третьему и четверто; му входам которого, а также к первым и вторым входам интегратора и блока коммутации подключены выходы блока управления, к первому входу которого и второму входу формирователя сигнала потери синхронизма подключен выход интегратора, к третьему входу которого подключен выход ключа, а к четвертому входу интегратора и второму входу блока управления подключен выход формирователя сигнала потери синхронизма, при этом к третьему четвертому и пятому входам блока коммутации подключены соответственно третий выход опорного генератора, выход блока выделения одного фронта за такт и выход асинхронного интегрального приемника, первый и второй входы которого объединены с соответствующими входами блока выделения фронтов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР N 640440, кл. Н 04 1 7/08, 1976 (прототип).

882012

Составитель E. Голуб

Редактор М. Циткнна Техред И,Кинц Корректор р. Билак

Заказ 10000/87 . Тираж 701 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4