Анализатор спектра

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕИИЯ

К АВТОРСКОМУ СВИДЕТЕЯЬСТВУ (61) Дополнительное к авт. саид-ву (22) Заявлено 28.0380 (21) 2899826/18-21 (5f)AA. Кл.

G R 23/00 с присоединением заявки ¹

Государственный комитет

СССР во делам изобретений и открытий (23) Приоритет

Опубликовано 231181 Бюллетень № 43 (53) УДК621. 317. 757

f 088. 8) Дата опубликования описания 23. 11 ° 81 (72) Автор изобретения

О. Л. Карасинский (71) Заявитель

Институт электродинамики AH Украин (54) АНАЛИЗАТОР СПЕКТРА

Изобретение относится к измерительной технике и может быть использовано для определения амплитуд гармоник периодических сигналов.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее блок умножения, формирователь констант, счетчик, умножитель частоты, преобразователь кода в число импульсов, нуль.органы, интегратор и регистратор(1).

Однако точность измерений известного устройства недостаточна.

Цель изобретения — повышение точности измерений.

Поставленная цель достигается тем, что в анализатор спектра, содержащий блок умножения, вход которого подключен к последовательно соединенным формирователю, умножителю частоты и преобразователю кода в число импульсов, счетчик, выходы которого через блок формирования . констант соединены с управляющими входами блока умножения, интегратор, два нуль-органа, два элемента И и регистратор, дополнительно введены второй интегратор, комбинационный сумматор, два ключа, три триггера и делитель напряжения, причем ключи включены между выходом блока умножения и вхо- дом интеграторов„ выход первого из которых подключен к регистратору и к делителю напряжения, управляющие входы обоих ключей соединены с выходами первого триггера, один из которых соединен также с управляющим входом комбинационного сумматора, включенного между выходами старших разрядов счетчика и входами старших разрядов блока формирования констант, выходы делителя напряжения и второго интегратора подклю15 ко входам обоих нуль-органов, выходы которых соединены со входами второго,и третьего триггеров, другие входы которого соединены с выходами формирователя, связанного

20 также с управляющими входами обоих интеграторов и с одним из входов первого триггера, другой вход которого подключен к выходу умножителя частоты, инверсные выходы второго

25 и третьего триггеров подключены через первый элемент И к первому входу счетчика, а прямой выход третьего триггера через второй элемент И соединен со вторым входом счетчика, Щ выход преобразователя кода в число

883772 импульсов соединен с соответствующими Входами второго и третьего триггеров и обоих элементов И.

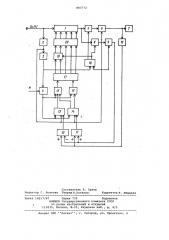

На чертеже представлена структурная схема предлагаемого анализатора.

Г1налиэатор содержит блок 1 умножения, формирователь 2, умножитель 3 частоты, преобразователь 4 коца в число импульсов, ключ 5, интегратор

6, регистратор 7, второй ключ 8, второй интегратор 9, нуль-органы 10 и 11, дели гель 12 напряжения, триггеры 13 и 14, элементы И 15 и 16, счетчик 17, триггер 18, сумматор

19 и блок 20 формирования.

Работает анализатор следующим образом.

Исследуемый сигнал поступает на формиронагель 2, ьыходные импульсы которого после умнОжения В умнОжи теле 3 частоты поступает на преобразователь 4 кода =- число импульcoz. На 2О управ>1я>о131их входах преобразователя 4 устанавливается код, равный номеру исследуемой гармоники. При этом после каждого импульса на входе преобразователя 4 на его выходе формируется д

11ач к а имп ульс он . КОличесгвО импуль

coB H I!a IIcE равно К. Эти импульсы пОстy11ают Hа ВxОды gòсTаlIОВКИ >3 0 триггеров 13 и .14 и подтверждают их сос>гоя1:ие равное " 0 . Так как

J.

ЗО три1 гера 13 11 14 находяTca в состоя-! I ни 0 ТО злемеHT И 1 .> Открыт а элемент И 16 закрыт, При этом

11М11у>..ьcû с Выхода преобразователя 4 и о с 1 : I I a;gг 11 а:3 1 е т 1гы и В х од с ч е тч и— ка 17. . четчик 17 имеет К устойчивьгх с!.>стоя HI!A . Е11.11и исxopHOP с 1етчика 17 равно g то, в ooT нетствии с вьш1ескаэаннБ3м, состояние счетчика 17 после и-го импульса на 4О выходе умножителя 3 частоты равно -" 3 mOd 1,1 (g 0 + (1)

Так как счетный. вход триггера 18 подклк1чен к выходу умножителя 3 частоты, то его состояние при нечетных и ранчо 1, а при четных 0, соответственно на управляющий

ВХОД сумматора 19 поступает 1 при четных и, и он прибавляет код ."{ 4 к выходному счетчику 17. 50

Каждому состоянию у на входах блока 20 формирования констант соответствует код на его выходе sin — g, М который поступает на управ.ляющие входы блока 1 умножения.

Выходное напряжение блока 1 на четных тактах умножителя частоты поступает через ключ 5, на интегратор 6, а на нечетных тактах — через ключ 8 на интегратор 9. В конце измерительного периода Т31 на выходах 60 интеграторов б и 9 будут напряжения, пропорциональные с точностью до постоянного 1..оэффициента косинусной а < и синусной В составляющим К-OA гармоники ряда Фурье, в ко- Я торый раскладывается напряжение

tJ„(t) . Отметим, что а „ и В получены по разным выборкам напряжения

tJq(t), т.е. В по четным, а а по нечетным, однако это на точность измерения не влияет, так как моменты выборок напряжений и фазы функций

Х- г гл

il

Sin - 9 и сон - - 9 совпадают. Напря>кения В „ и а с выходов интеграторов б и 9 поступают на нуль-органы 10 и 11.

Сигнал логическая 1 на выходе нуль-органа 10 будет в конце периода Т только при условии

К „В + а„(0 (1) где Кд13-*коэффициент передачи делителя 12 напряжения.

Сигнал логическая 1 на выходе нуль-Органа 11 будет только при услов ии

К4„ — а <о {2)

После начала очередного периода измерений формирователь 2 вырабатывает короткий импульс, который синхронизирует установку в 1 одного иэ триггеров 13 и 14, а также производит установку в 0 триггера

18 и сброс интеграторов б и 9.

Если выполнилось условие (1), то триггер 13 устанавливается в 1, при этом закрывается элемент И 15, и очередной импульс с выхода преобразователя 4 не поступит на вход счетчика 17. Это приводит к тому, что исходное состояние счетчика 17 в начале периода Т„ уменьшится на

/ единицу. г

Если ныполнилось условие {2), то триггер 14 устанавливается н 1, при этом закрывается элемент И 15 и открывается элемент И 16. Тогда очередной импульс с выхода преобразователя 4 поступает на счетный вход счетчика 17, а его состояние увеличится на две единицы, что соответствует увеличению его исходного состояния g в начале периода на единицу. Этот импульс с выхода преобразонателя 4 поступает на входы установки в 0 триггеров 13 и 14, сбрасывает их. После этого тольКо элемент И 15 будет открыт.

Если не выполнилось ни одно из условий (1) и (2), то ни один из триггерон 13 и 14 не устанавливаетсН в 1 .

После этого цикл работы устройства начинается сначала, но теперь величина 1З изменилась таким образом чтобы модуль разности фа.-. M и 1 g уменьшился. Процесс измене Ч ния go будет продолжаться до тех пор, йока не выполняется ни одно из условий (1) или (2) . При этом

1ак(а," .) ((н

Для устойчивой работы устройстна величину К „ следует выбирать не более )Г/N.

883772

Амплитуда К-ой гармоники равна ь откуда следует, что А =-«b <,если

Ц* Полагая Кдн= пр); Вы.н полнении условия (3), имеем 5

t=t IH) т.е. мультипликативная погрешность измерения А< не превосходит величину С,1 Ъ при N>72 и не превосходит (g величину 1 % при N)24.

Повышение точности и помехоустойчивости в предложенном устройстве достигается вследствие того, что максимальное значение величины В< находится в результате ее сравненйя с величиной а в соответствии с формулами (1}, {2) и {3) . При этом результаты сравнения не зависят от абсолютных значений а. и в а только от угла сдвига фазы гаомо ;. — 20 ки и исходногo сОст янин счетчика 0

В начале периода измерений. Скачки амплитуды гармоники не г риводят к сбоям в работе ус rpoAcòâa, так как величины а и в изменяются в одина- 35

КОВых прОпОрциях: а нуль Орга.н фиксн— рует только знак Выражений (1) и (2) .

Формула изобретения

Анализатор спектра, содержащий блок умножения, вход которого подключен к последовательно соединенным фОрмирОВателю умнОжителю частоты и преобразователю кода в число импульсов, счетчик, выходы которого через блок формирования констант сое-, динены с управляющими входами блока умножения, интегратор, два нуль-органа, два элемента И и регистратор, от личающийся тем,что с целью повьиаения точности измерений, в него дополнительно введены

Второй интегратор, комбинационный сумматор, два ключа, три триггера и делитель напряжения, причем ключи включены между выходом блока умножения и входом интеграторов, выход первого иэ которых подключен к регистратору и к делителю напряжения, управляющие входы обоих ключей соединены с выходами первого триггера, один из которых соединен также с управляющим входом комбинационного сумматора, включенного между выходами старших разрядов счетчика и входами старших разрядов блока формирования констант, выходы делителя напряжения и второго интегратора подключены ко входам обоих нуль-opraEIo.ç, выходы которых соединены со

Входами Второго и третьего триггеров, другие входы которого соединены с выходом формирователя, связанно=» o также с управляющими входами

Обоих интеграторов и с одним из входов гервого триггера, другой вход которого подключен к выходу умножителя частоты, инВерсные ВыхОды ВтОрого и третьего триггеров подключены через первый элемент И к первому входу счетчика а прямой выход третьего триггера через второй элемент И соединен со вторым ВХодом счетчика, выход преобразователя кода в число импульсов соединен с соотВетствующими входами второго и третьего триггеров и обоих элементов И.

И=точники информации, принятые Во внимание при экспертизе

1. Авторское свидетельство СССР

9 432411, кл. G 01 R 23/12, 1974.

883772

Составитель A. Орлов

Редактор Г. Волкова ТеКрЕд И. Лсталош;

Корректор Н. Швьщкая б

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4

Заказ 10217/б7 Тираж 735 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5