Преобразователь фаза-код с автоматической коррекцией погрешности преобразования

Иллюстрации

Показать всеРеферат

I (72) Авторы изобретения

%. А. Скрипник, А. И. Суд-Злочевский, И

Е. И. Савченко и А. С. Бойко.Ьт

Киевский технологический институт легк и промьнпленности (7l ) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ФАЗА — КОД С АВТОМАТИЧЕСКОЙ

КОРРЕКЦИЕЙ ПОГРЕШНОСТИ ПРЕОБРАЗОВАНИЯ управления (2).

Изобретение относится к информа ционно-преобразовательной технике и может быть использовано для кодирования значений фазовых углов с повышенной точностью.

Известен двухканальный преобразователь фаза--код с гетеродинным преобразованием частоты сигналов, сдвинутых по фазе. В этом устройстве введение третьего коммутируемого ка10 нала с гетеродинированием. для поочередного преобразования входных сигналов позволяет формировать управляющий сигнал, пропорциональный фазовой нендентичности основных каналовfl)

3%

Недостатком этого преобразователя является трудность выполнения двух избирательных усилителей в основных каналах с перекрестными (зеркальными) фазочастотными характеристиками.

Наиболее близким по технической сущности является измерительный преобразователь фаза †к, содержащий три преобразовательных канала, автбматические переключатели, два преобразователя фазового сдвига в число импульсов, реверсивный счетчик.с регистрами памяти на выходе, счетчик с регистром памяти на выходе и блок

Недостатком этого устройства является неполное исключение инструментальных погрешностей преобразования фазового сдвига в код. Так, погрешности основного преобразователя фазового. сдвига в число импульсов, в котором осуществляется промежуточное преобразование фазового сдвига во временной интервал,.не обнаруживаются системой коррекции и поэтому. не исключаются. Погрешности кодирования временного интервала, возникаю» щие от нестабильности частоты счетных импульсов и нестабильности фронтов кодируемого интервала, также не корректируются.

883784

Цель изобретения — повьпвение точности преобразования.

Поставленная цель достигается тем, . что в преобразователь, содержащий в каждом из трех преобразовательных каналов смеситель и последовательно соединенный с ним избирательный усилитель, общий для всех преобразовательных каналов гетеродин, два преобразователя фазового сдвига в число импульсов, причем входы одного из них соединены с выходами избирательных усилителей первого и второго .преобразовательных каналов, входы . другого — с выходами избирательных усилителей второго и третьего преобразовательных каналов, счетчик импульсов с двумя регистрами памяти на выходе, реверсивный счетчик ияпульсов с регистром памяти на выходе, входы счетчиков импульсов соединены с выходами первого и второго преобразователей фазового сдви- s га в число импульсов соответственно, автоматический переключатель, своими входами соединенный с сигнальными входами смесителей первых двух преобразовательных каналов, а выходом — с сигнальным входом смесителя в третьем преобразовательном канале, блок управления, выходы которого соединены с управляющими входами счетчиков импульсов, регистров памяти и автоматического переключателя, введены формирователь коротких импульсов и три триггерных делителя частоты, входы которых соединены с выходом формирователя коротких импульсов, входом подключенного к общему гетеродину, выход первого триггерного делителя частоты соединен с управляющим входом смесителя первого преобразовательного канала, первый выход второго триггерного делителя частоты соединен с управляющим входом смесителя второго преобразовательного канала, а второй с первым входом блока управления, первый вход третьего. триггерного делите" ля частоты подсоединен к управляющему входу смесителя третьего преобразовательного канала, а второй выход:=. ко второму входу блока управления, установочные входы -первого триггерного. делителя частоты соединены с выходом регистра памяти реверсивного счетчика импульсов, выходы регистра памяти другого счетчика

О. =U в р Ми(цу +tq +q,), . %" (® 4 11Г)

43

0В - 1УУ1 <1© < l> (®g4+Vg ЧГ) где(Ю и 1 — частота и фаза гетеродинГ Г ного напряжения;

IJ „ цц) = — — амплитуда и частота .прямоугольного напряжения на выходах триггерных делителей частоты; и1 — фаэовые сдвиги, вносимые

Ъ, 4 - 5 делителями частоты 4;5 и

6 соответственно.

С помощью избирательных усилителей

13, 14 и 15 в каждом иэ каналов выде."

SO соединены с установочными входами второго триггерного делителя частоты.

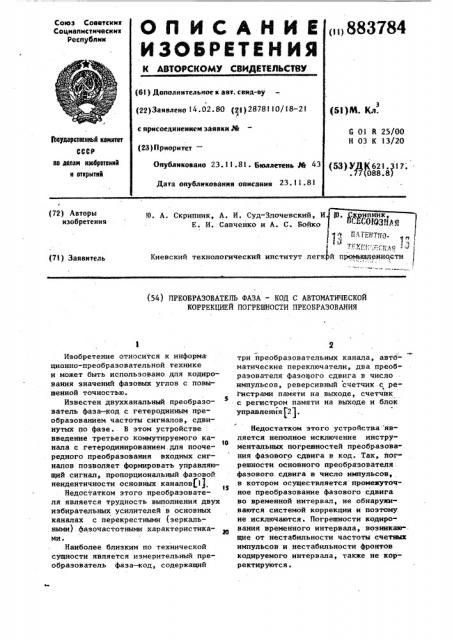

На чертеже показана структурная схема устройства.

Устройство содержит автоматический .переключатель 1, гетеродин 2, формирователь 3 коротких импульсов, триггерные делители 4-6 частоты, смеси>0 тели 7-9, блок lá управления, регистры 11 и 12, избирательные усилители

13-15, преобразователи 16 и 17 фаза— число, реверсивный счетчик 18 импульсов, счетчик 19 импульсов, регистр 20..

1S, Устройство работает следующим образом.

Цикл преобразования состоит из трех тактов, длительность которых задается блоком 10 управления. В наgo чале первого такта счетчики 18 и 19 импульсов, регистры ll, 12 и 20 памяти, делители 4-6 частоты с помо.щью импульса блока 10 управления переводятся в исходное (нулевое)

25 состояние. Автоматический переключа- . тель 1 соединяет сигнальный вход сме сителя 7 с сигнальным входом смесителя 9. Входное напряжение

Ц1 U sin(CN

883784

-ющего в режиме "Сложение", преобразуется в промежуточный код М

О 0 COS (В Ь+ЧХ Щ,+Ф ), 0„= U Ä COS(и)ф,+а%, + У4), 8 п18 гдето,1 „, дЯ и дф - фазовые сдвиги, вносимые смесителем и избирательным усилителем каждого из капалов.

Фазовый сдвиг между выходными.напряжениями избирательных усилителей

13 и 14 с учетом фазовой неидентичности каналов определяется выражением

Л2 Х 1д 4

15 где йт аЧЛ Дтт- фазовая погрешность. вносимая неидентичностью фазовых характеристик преобразовательных звеньев 7,8, 13 и 14.

Фазовый сдвиг между. выходными напряжениями избирательных усилителей

14 и 15 с учетом фазовой неидентичности каналов определяется выражением

45

1 " 1%у2 1 х И, + " 6) где К вЂ” масштабный коэффициент дре.1 . образования фаза. — код пре50 образователя 16 и счетчика

19;

Ьфб- погрешность преобразования фаза — код, вносимая блоками lб,и 19.

Фазовый сдвиг1 с помощью преобI разователя 17 фазового сдвига. в последовательность импульсов и реверсивного счетчика 18 импульсов, работа. ЯЕ,3 Х 12,Ь 4 6

Ю 50 гдето = 69<-М вЂ” фазовая погрешность, 2) $ вносимая неиндентичностью фазовых характеристик преобразовательных звеньев 8,9, 14 и 15.

Фаза, вносимая делителями 4-6 частоты, определяется начальной установкой их триггеров. При установке всех триггеров делителей в начальное состояние вносимые ими фазовые сдвиги равны Py =Yg = g> = 7<р . Фазовый сдвиг с помощью преобразователя 16 фазо40

Лф ого сдвига в последовательность импульсов и счетчика 19 импульсов преобразуется в код ЙЛ, который записывается в регистр 1.2

2 2 2,Ъ 2 4õ + 1 2,3+ Ж7)р где К вЂ” масштабный коэффициент преобразования фаза — код преобразователя 17 и счетчика

l8;

Ьф — погрешность преобразования фаза — код, вносимая блоками 17 и 18.

Во втором такте по сигналу блока

10 управления автоматический переключатель 1 соединяет сигнальный. вход смесителя 8 с сигнальным входом смесителя 9. При этом на. преобразователь

I 7 воздействует фазовый сдвиг удQ>>f с

+94 — V . Код, записанный в регистре 12 памяти, по принципу временной эадер:хки преобразуется в сдвиг фаэ напряжений Ug и 0, для этого делитель 6 частоты снова переводится в начальное состояние, т.е. 4 =Vо; в момент, когда все триггеры делителя, 6 переходят из состояния "Единица" в состояние "Нуль" на второй вход блока 10 управления поступает сигнал., по которому блок 10 управления выдает команду переписи числа Ng,записанноно в регистре 12, в делитель 5, вследствие чего все триггеры делителя 5 устанавливаются в состояния, определяемые кодом МЛ.

Таким образом, фазовый сдвиг вносимый делителем 5 частоты Определяется выражением

КЛ

4 О 1 lW< 0 фЛ ®(+Ю Д.+% )У где pq — масштабный коэффициент преобразования код — Aasa делителя 5 частоты.

На вход счетчика 18, переведенного во втором такте в режим "Вычитание"., поступает последовательность. импульсов, паопорциональная фазовому сдвигу . При этом в счетчик

18 заносится промежуточный код

ИР) КЯ Ь др вФ1Р4 \Рб+ у ) =КДКФ®Л (1Ь+

+ И1,а.< 4 + < e,ъ+ + 3В результате двух тактов преобра" зования в реверсивном счетчике 18 формируется раэностный код (Ng- М )< который при выборе К =Ф равен

Л lЛ

Йд "-Й2 1 1 К .(1,2 д б)у

883784 т.е. разностный код пропорционален фазовой погрешности от неидентичности фазовых характеристик каналов и кодирующих блоков. Разностный (кор- . ректирующий) код по сигналу блока

10 управления записывается в конце такта в регистр 11 памяти.

В третьем такте по сигналу блока 10 делитель 5 частоты переводится в начальное состояние (Vg= Vg).

В момент, когда все триггеры делителя 5 переходят из состояния "Единица" в состояние "Нуль", на первый вход блока 10 поступает сигнал, по которому блок 10 выдает команду переписи числа N4 записанного в регистре ll, в делитель 4, вследствие чего триггеры делителя 4 устанавливаются в состояния, определяемые кодом Й . После этого сдвиг фаз напряжений 0 и 114 определяется выражением

К2 4="о+"4А= о 1,>+ Vs) где г3 — масштабный коэффициент пре(2. образования код — фаза делителя 4 частоты.

Код, соответствующий фазовому сдвигу между сигналами избирательных усилителей 13 и 14 с учетом гетеродинных напряжений равен ()(+ Ж1Д+ Ъ 4+ б)=

К

-к, ч„+ч„,,- -" -;м„,,+

Кя

+1 % 1Ь) . При выборе К фазовый сдвиг, вносимый делителем 4 частоты, компенсирует фазовую погрешность от неидентичности преобразовательных характеристик звеньев в первом и втором преобразовательных каналах и погрешность кодирования преобразовательных звеньев 16 и 19, и результирующий код И К, 1 <, Ло сигналу IO уггравления этот код переносится в регестр 20, где хранится до следующего цикла преобразования, состоящего из трех тактов.

Предлагаемый преобразователь реализуется на современной элементной ,базе — интегральных микросхемах. Благодаря цифровой коррекции погрешнос.ти преобразователя снижаются требова" ния к стабильностями и идентичности характеристик микросхем и их внешних элементов, что позволяет. применять

1О

1S

3S

5S более простые и дешевые элементы и узлы.

Формула изобретения

Преобразователь фаза — код с автоматической коррекцией погрешности преобразования, содержащий в каждом из трех преобразовательных каналов смеситель и последовательно соединенный с ним избирательный усилитель, общий для всех преобразовательных каналов гетеродин, два преобразователя фазового сдвига в число импульсов, причем входы одного из них соединены с выходами избирательных усилителей первого и второго преобразовательных каналов, входы другого — с выходами избирательных усилителей второго и третьего преобразовательных каналов, счетчик импульсов с двумя регистрами памяти на выходе, реверсивный счетчик импульсов с регистрами памяти на выходе, входы счетчиков импульсов соединены с выходами первого и второго преобразователей фазового сдвига в число импульсов, соответственно, автоматический пере- ключатель, входами соединенный с сигнальными входами смесителей первых двух преобразовательных каналов, а выходом " с сигнальным входом смесителя в третьем преобразовательном канале, блок управления, выходы которого соединены с управляющими входами счетчиков импульсов, регистров памяти и автоматического переключатет ля, отличающийся тем, что, с целью повышения точности преобразования, введены формирователь коротких импульсов и три триггерных делителя частоты, входы которых соединены с выходом формирователя коротких импульсов, входом подключенного к общему гетеродину, выход первого триггерного делителя частоты соединен с управляющим входом смесителя первого преобразовательного канала, первый выход второго триггерного делителя частоты соединен с управляющим входом смесителя второго преобразовательного канала, а второйс первым входом блока управления, первый выход третьего триггерного делителя частоты подсоединен к управ-, ляющему входу смесителя третьего преобразовательного канала, а второй выход — ко второму входу блока уп« равления, установочные входы первого триггерного делителя частоты соедине883784

Составитель Л. Агеева

Редактор О. Половка Техред М.Рейвес Корректор В. Синицкая

Заказ 10218/68 Тираж 735 Подписное

ВНИИХИ Государственного комитета..СССР по делам изобретений и открытий

)13035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 ны с выходом регистра памяти реверсивного счетчика импульсов, выходы регистра памяти другого счетчика соединены с установочными входами второго триггерного делителя частоты.

Источники информации, принятые во внимание.при экспертизе

) Авторское свидетельство СССР

N - 564100, -кл. Н 03 К 13/20, 1976.

2. Авторское свидетельство СССР по заявке ))- 2508398/)8-21, .1978 (прототип).