Устройство для потенцирования

Иллюстрации

Показать всеРеферат

Соеоэ Соеетскнк

Соцналнстнческнк

Раслублнк

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОИ:КОМУ C ТЕЛЬСТВУ

<щ883900 (61) Дополнительное к авт. саид«ву(22) Заявлено 190380 (21) 2898242/18-24 с присоединением заявки Но— (23)Приоритет

Опубликовано 2 Зд 1,8д Бюялетаяе 1494З

Дата опубликования описания 23.1 131 (51)М. Кл.з

G F 7/556

ГоеуяаРетаекный IL0NllTcT

СССР во делан изобретений к открытка

Ж) ПЖ 681.3! (088.8) (72) Авторы изобретения

A.A.ÌåëüíHK и Н.В.Черкасский

Львовский ордена Ленина политехнический нн ктут им. Ленинского комсомола (71) Заявитель (54) УСТРО ACTBO ДЛЯ ПОТЕНЦИРОВАНИЯ

Изобретение относится к вычисли- тельной технике и предназначено для использования в специализированных и универсальных вычислительных устройствах.

Известно устройство для вычисления элементарных функций (в том числе и потенцирования) табличного типа на основе постоянного заповжнающего устройства, в котором регистр адреса блока памяти используется в качестве регистра аргумента, а .регистр. числа блока используется в качестве регистра аргумента, а регистр числа блока памяти - s качестве регистра резуль- .IS тата устройства. Такое устройство имеет предельно высокой быстродействие (1).

Однако область применения ограничивается 8-12 двоичными разрядны аргумента,. поскольку объем блока памяти быстро растет с увеличением разрядности аргумента. Современные вычислительные системы работают с аргументами, имеющими разрядность до 64 разрядов.

Наиболее близким по технической сущности к предлагаемому изобретению является устройство для йотеицщ.- ровакия, содержащее регистр аргумен- ЗО та, два блока памяти, узел сдвига, триггер, блок управления,три коммутатора, выполненные в виде схем

И-ИЛИ, буферный регистр, регистр результата, сузееатор (2).

Однако известное устройство при достаточно высоком быстродействии имеет большие объемы блоков памяти.

Цель изобретения — сокращение аппаратурных затрат на блок памяти.

Поставленная цель достигается тем, что устройство, содержащее регистр аргумента, блок памяти, буферный регистр, три коммутатора и регистр результата, причем выход старuwx разрядов регистра аргумента подключен к первому информационному, входу первого коммутатора, выход которого через блок памяти соединен с входом буферного регистра, выход которого подключен к первому информационному входу второго коммутатора, содержит блок умножения, причем выход младших разрядов регистра аргумента и выход буферного регистра соединены соответственно со вторым и первым информационными входами соответственно первого н третьего коммутаторов, выходы второго и третьего;коммутаторов подключены к пер883900 вому и второму входам блока умножения, выход которого через регистр результатов соединен со вторыми инФормационными входами второго и третьего коммутаторов, первые и вторые управляющие входы коммутаторов соединены с соответствующими входами синхронизации устройства.

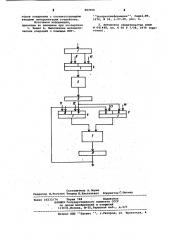

На чертеже представлена блок-схема устройства.

Устройство содержит регистр 1 аргумента,блок 2 памяти, коммутаторы Э5,буферный регистр б,блок 7 Умножения регистр 8 результата, выходы 9 - 14 сии хрон из ац ни.

Вычисление, функции двух от аргумента Х (OiX c 1) производится в устройстве на основе следующих соотношений. Если аргумент Х имеет разрядность,то примем, что Хl — число,образованное старшими разрядами

20 аргумента, Х 2 — число, образованное младшйми разрядами аргумента.

Тог Y = 2 2 2

Диапазон изменения числа Xl производится к диапазону изменения чис- Я5 ла Х2 путем преобразования

Хl = Xl-2

Тогда Y = (2 ) Y.2 °

И 1 М1

В последнем выражении числа Хl и 3()

Х2 находятся в том же диапазоне, поэтому для вычисления выражений

2"" и 2"< достаточно одного блока памяти. 6

Устройство работает следующим образомм.

Значение аргумента Х находится в регистре 1. В первом такте работы устройства сигнал, поступивший по управляющему входу 9, пропускает на 4 вход блока 2, хранящего таблицу преобразований 2.- 2 значение Xl С выхода блока 2 значение поступает в буферный регистр б. Во втором такте содержимое буферного регистра б поступает через коммутатор 4 по управ- 45 ляющему сигналу 12 и через коммутатор 5 по управляющему сигналу 14 на входы блока 7 умножения, на котором возводится в квадрат и записывается в регистр 8. В том же такте $0 по управляющему сигналу, поступающему по входу 10, значение Х2 иэ регистра

:,:1 аргумента поступает на вход блока 2, из которого считывается значение 2" - и записывается в регистр 6. у

Следующие . — -1 тактов повторяют. ся следующей ойерацией. По управляющйк сигналам, поступающим по входам

11 и 13, содержимое регистра 8 ре- д) зультата поступает через коммутаторы

4 и 5 на вход блока 7 умножителя, где возводится в квадрат и с его выхода снова записывается в регистр 8 результата. В .результате данных one- y раций в регистре 8 находится значение — 24 (2 ) ъ 2 X

В последнем такте по управляющему сигналу, поступающему по входу 13, содержимое выходного регистра 8 про ходит через коммутатор 5 на вход блока 7 умножения, а по управляющему сигналу, поступающему по входу 12 на другой вход блока 7 умножения, поступает содержимое буферного регистра б через коммутатор 4. В блоке умножения Формируется искомое значение, которое поступает в регистр 8 результата и из него на выход устройства.

В данном устройстве требуется обьем памяти, равный

m ,Ю- m m2 2 бит, при m = 24 получаем

Q *= 24 ° 2 = 98304 бит.

Суммарный объем используемой в известном устройстве памяти определяется выражением

Q< = g„2 + (m — k + 1 hogg(m-)<+1) где k = ) - — - (а функция f (X) =)Х (представляет собой наименьшее целое число, не менее Х.

Для m = 24 получаем Q 224400 бит.

В предлагаемом устройстве по сравнению с известным объем памяти уменьшен как минимум на величину

Q„- Q = (m — k + l) ) Cog<(m-k + 1)

f + 1 ) 2

Формула изобретения

Устройство для потенцирования, содержащее регистр аргумента, блок памяти, буферный регистр, три коммутатора и регистр результата, причем выход старших разрядов регистра аргумента подключен к первому:информационному входу первого коммутатора, выход которого через блок памяти соединен с входом буферного регистра, выход которого подключен к первому информационному входу второго ком- . мутатора, о т л и ч а ю щ е е с я тем, что,с целью сокращения аппара1турных затрат, оно содержит блок умножения, причем выход младших разрядов аргумента и выход буферного регистра соединены соответственно со вторым и первым информационными входами соответственно первого и третьего коммутаторов, выходы второго и третьего коммутаторов подключены,к первому и второму входам блока умножения, выход которого через регистр реэультатов соединен со вторыми информационными выходами второго и третьего коммутаторов, первые и вторые. управляющие входы коммуга883900

Составитель А. Зорин

Редактор Н.Рогулич Техред Ж.Кастелевич Корректор. . екмар

Заказ 10233/74 Тираж 748 Подписное

ВНИИПИ Гоеударствейного комитета СССР

% по делам изобретений и открытий

113035,Москва, И-35,Раужская наб., д.4/5

Филиал ППП Патент, г.Ужгород, ул Проектная, 4.торов соединены с соответствующими входами синхронизации устройства.

Источники информации, принятые во внимание при экспертизе

1. Хемел A. Выполнение математических операций с помощью ПЗУ-. Экспрессинформация, Серия,BT, 1970, 9 32, с. 27-29,, рис. 4.

2. Авторское свидетельство СССР

9 641448, кл. G 06 F 7/38, 1979 .(про тотип).