Устройство для деления частотно-импульсных сигналов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВ ИЕЛЬСТВУ

Сеюз Севетскни

Сецналнстнческнк

Ресвублнк (61} До олиительиое к аат. саид-ау (22) Заявлено 01О280 (23) 2882504/18-24 (51)М. Кл.

G 06 F 7 /68 с присоединением заявки Йо (23) Приоритет

Госудвретаенмый коинтет

СССР ао делан мзобретенрй а открытий (53) УДК 681..З (088. 8) Опубликовано 2З.1181, бюллетень 14о 4З

Дата опубликования описания 2 3.11.81 (72) Автор изобретения

В.В.Короник

Куйбышевский авиационный завод (71) Заявитель (54) УСТРОИСТВО ДЛЯ ДЕЛЕНИЯ ЧАСТОТНО-ИМПУЛЬСНЫХ

СИГНАЛОВ

Изобретение относится к автоматк- ке и вычислительной техникб и может быть использовано в устройствах обработки информации автоматических систем контрол я и управления.

Известны устройства для деления частотно-импульсных сигналов, использующие преобразования одного йз сигналов в пропорциональный временной интервал, либо в последовательность временных интервалов fl).

Недостатками таких устройств является то, что при их реализации всегда приходится выбирать между скоростью и точностью выполнения операции при одновременном учете сложности требующегося оборудования.

Известно также устройство для деления частотно-импульсных сигналов, содержащее два счетчика, ysen перезаписи, генератор тактовой частоты и схемы автоматики., позволяющее повысить быстродействие выполнения операции деления частотно-импульсных скг- налов (2).

Однако известное. устройство также не обеспечивает получения оптимапьных значений точности и быстродействия в широком диапазоне изменения значений входНых частот. Кроме того практическая реализация этого устройства затрудненанз-за достаточно высокой аппаратурной сложности.

Цель изобретения — расширение области применения устройства, за счет обеспечения при заданной точности вычислений получения оптимального быстродействия в широком диапазоне изменения частот входных сигналов.

Поставленная цель достигается тем, что устройство для деления частотноимпульсных сигналов, содержащее первый и второй счетчики, первый и вто15 рой ключи, вход первого ключа соединен со входом делимого устройства,, вход второго ключа соединен со входом делителя устройства, выходы первого и второго ключей соединены со

29 входом соответственно первого и второго ключей соединены со входом соответственно. первого н второго счетчиков, содержит две группы триггеров, две группы элементов И и элемент ИЛИ, второй счетчик содержит (Ч + п ) разрядов (где g=Ioga)(gp

1og Д; a — основание систеьн счисления, в которой работают счетчики; .d"|;- заданное, значение относи30 тельной статистической погрешности

883902 вычислений; Д - динамический диапазон изменения частоты делителя1

- максимальное значение частоты делителя;,„ „ -минимальное значение частоты делителя), выходы переполнения разрядов второго счетчика с gro по (g + h — 1) - и соединены с нулевыми входами триггеров соответственно с первого по h — и первой группы, единичный вйход каждого из которых подключен к первому входу соответствующего элемента И первой группы, выход которого соединен с единичным входом соответствующего триггера второй группы, единичный вы.ход которого соединен с первым выходом соответствующего элемента И второй группы, второй вход которого соединен с нулевым входом соответствующего триггера первой группы, первые управляющие входы первого и второго ключей, единичные уходы триггеров .первой группы и нулевые входы триг.геров второй группы соединены сь входом начала операции устройства, вторые входил.элементов И первой группы соединены со входом конца образцового интервала времени устройства, выходы элементов И второй группы и вы-ход переполнения (g + h)- го разряда второго счетчика, который является выходом переполнения второго счетчика, соединенк со входами элемента

И31И,выход которого подключен ко вторым управляющих входам первого и второго ключей.

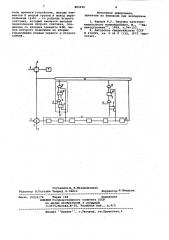

На чертеже изображена блок-схеМа устройства.

Устройствсь содержит ключи 1 и 2, вход 3 начала операции, на который подается сигнал в начале цикла вычислений, вход 4 конца образцового интервала времени, на который подается сигнал в конце образцового ин» тервала времени, вход 5 делимого и вход б делителя, счетчик 7, на котором формируется результат вычислений, счетчик 8, триггеры 9, трнгг ры 10, элементы И 11, элементы И 12 и элемент ИЛИ 13. Импульсы делимого (числителя) подаются на вход ключа 1, выход которого соединен с выходом счетчика 7, импульсы делителя (знаменателя) подаются на вход ключа 2, выход которого соединен со входом счетчика 8, содержащего (g +h ) разрядов, причем выходы разрядов, начиная с g " ro соединены с пулевыми входами триггеров 9 и входами элементов И 12 соответственно. Единичный выход каждого триггера соединен со входом соответствующего элемента И ll,второй вход которого подключен ко входу 4, выход каждого элемента К 11 соединен с единичным входом соответствующего триггера 10. Единичный вы- ход каждого триггера 10 соединен с другим входом соответствующего элемента И 12. Выходы всех элементов И

12 и выход переполнения счет Яка 8 соединены со входами элемента ИЛИ 13, выход которого подключен к управляющим входам ключей 1 и 2. Другие уп равляющие входы ключей 1 и 2, а также установочный вход каждого триггера 9 и вход обнуления каждого тригге;ра 10 соединены со входом 3 устройст, ва.

Устройство работает следующим образом.

Сигнал начала операции, поданный по входу 3, открывает ключи 1 и 2, переводит в единичное состояние триггеры 9 и осуществляет сброс триггеров

10. Импульсы частоты делимого f со входа 5 через ключ 1 начинают поступать на вход счетчика 7. а импульсы частоты делителя f со входа 6 че1 рез ключ 2 - на вход счетчика . Если

20 производится подсчет числа нмпульсоВ за время, равное 10 периодов частоты f < (в предположении, что основан ие используемой системя счисления а 10) то результат вычислений Nx может быть записан

Их " 10% 4а (")

Когда величины входных частот изменяются в широком диапазоне, при выборе полной емкости счетчика 8 (величины g + h ) приходится сталкиваться с противоречивыми, требованиями для нижней границы диапазона, иэ условий обеспечения заданного, быстродействия выполнения операции, полную емкость счетчика 8 следует делать небольшой, а для верхней границн диапазона, нз условия обеспечен ия з адан ной точно ст и выч ислен ий, большой. Возникает необходимость применения адаптивной схемы счетчика 8, 4О меняющего свою полную емкость в зависймости от величины частоты е1

Для обеспечения заданного значения относительной статйческой погреввости вычислений d, число импульсов

45 ых частоты йl поступивших за время

oriepaQftKt

0Ъ 4 lÌf. (2)

Учитывая, что Ny fyt<< и решая

5() выражение (2) относительно t><, получаем . 1 — <з>

Из выражения (3) следует, что ми- нимальное время выполнения операции

55 (t< ) для заданного значения + dy дет иметь место на нижнем краю диапазона входных частот Ю

1 0

С М (4)

60 . Полученное значение t округляют в большую сторону до значения ближайжго числа из ряда 10, где рлюбое целое действительное число.

В адаптивном режиме обеспечива65 ющем при заданной точности вычисле8839 02 ний оптимальное быстродействие, через время А после начала операции со входа 4 поступает сигнал на входы элементов И 11. При этом появляется импульс на выходе элемента И ll, который поступает на установочный вход соответствующего триггера 10 .и переводит его |в единичное состоян ие.

Тогда импульс перепоьзьения любого, разряда с g — го по (h - 1) — и при условии, что он 4ормнруется через время tent|1, поступая на вход соответствующего элемента И 12, формирует сигнал на его выходе, этот сигнал, пройдя через элемент ИЛИ 13, осуществляет запирание ключей 1,2 и выполня- ь5 ет останов операции.

Если импульс переполнения любого из разрядов, начиная с g-ro но (h-1)-й,формируется червз время t c, p, то им осуществляется сброс соответст-Щ вуощего триггера 9, после чего на выходе соответствующего элемента И 12 в данном цикле вычислений импульс останова операции появиться не сможет.

3Ьпзульс останова операции корми- з5 руется на выходе элемента и 12, рк " fqo1„„(Ó,,á10Ô„ элемента И 12k i при lo»" f1&n с f1< 10х

При максимальном значении входной частоты й„„„®р 10. й1

6 останов операции пройзводится импульсом переполнения последнего разряда счетчика 8. 35

Из.приведенного неравенства получают выражение для выбора h, Вф "-fg2, (5) i ЯЬ1Я где 0 — динамический диапазон измене- 4() ния входных частот.

Количество декад g счетчика 8 определяется из условия их заполнения юьпульсами входной частоты f щэи ее минимальном значении f „ эа время tz

10"-f1 t, откуда p k t . (6)

Решая совместно (6) и (4) полу" (ра — - (7)

Вычисленные на основании (5) и (7) значения Ь и д слецует округлить в большую сторону до ближайшего целого числа .

Выражение для выбора общего количества разрядов счетчика 8 записы, вают в следующем виде (8) аО

При этом время выполнения операции иэмеияетс,я от величины 10 йл на нижней границе каждого поддиапазона до величины t< иа его верхней границе, т,е. 65

o oo р,,у„(9)

4ttt3n Q 1ЮЮ С

Чаким образом, применение предлагаемого устройства, аднаптивного кзн ачен ию входной частоты, поз воляет вместо монотонного увеличения времени выполнения операции t „c уменьшением частоты делителя йолучить циклическую закономерность изменения в расчетном диапазоне, удовлетворяющем требованиям оптимального быстродействия при одновременном обеспечении заданной точности вычислений, что в целом расширяет область его применения.

Формула изобретения

Устройство для деления частотноимпульсных сигналов, содержащее первый н второй счетчики, первый и второй клан, вход первого ключа соеди— нен сс входом делимого устройства, вход второго ключа соединен со входом делителя устройства, выход первого и второго ключей соединены со входом соответственно первого н,второго счетчиков,о т л и ч а ю щ е ес я тем, что, с целью расширения области применения устройства,устройство содержит две группы тригге-, ров, две группы элементов И и элемент ИЛИ, второй счетчик содержит (g+h) разрядов (где д= logged<,.

h = Iog Д ; — основание системы счисления, в которой работают счетчики; о — заданное значение относительной статистической погрешности вычислений; Д = """ " - динами%1m1n ческий диапазон изменения частоты делителя; . f«< максимальное значение частоты делителя;. Е1,11, — минимальное значение частоты делителя), выходы переполнения разрядов второго счетчика с g — го по (g + h — 1) - и соединены с нулевыми входами триггеров соответственно с первого по

h -й первой группы, единичный выход каждого из которых подключен к первому входу соответствующего .элемента И первой группы, выход которого соединен с единичным входом соответствующего триггера второй группы, единичный выход которого соединен с первым входом соответствующего элемента И второй группы, второй вход которого соединен с нулевым входом соответствующего триггера первой группы, первые управляющие входы первого и второго ключей, и единичные входы триггеров первой группы и нулевые входы триггеров второй группы соединены со входом начала операции устройства, вторые входы элементов И первой группы соединены со входом конца образцового интер. 883902

Составитель В.Михайличенко

Редактор ц.рогулич Техред A,Ñàçêà . : Корректор1Н.Швыдкая

Жкаэ, 10233/74 Тираж 748 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открцтиЪ

113035,Москва,Ж»35, Раушская иаб., д.4/5

Филиал Патент, r.Óæãîðîä, ул.Проектная,4 вала времени устройства, выходы элементов И второй группы и выход переполнения (g+h) - го раэряда второго счетчика, который является выходом переполнения второго счетчика, соединены со входами элемента ИЛИ, выход которого подключен ко вторйм управляюцим входам первого и второго ключей.

Ю

Источники ивФор щии принятые во внимание при экспертиэе

1 Карпов Р,Г. Техника частотно 4мпУльснОГО моделйРОВанияу М,, Ма шиностроение, 1969, с.94-123.

" 2. Авторское свидетельство СССР

9 474005, кл. G 06 F 7/52, 1973 (прототип) .