Устройство переменного приоритета

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Рвслублик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

„„883906 (61) Дополнительное к авт. свид-ву— (22) Заявлено 020880 (21) 2809890/18-24 с присоединением заявки Нов (23) Приоритет— (51}М 1,(3

G 06 F 9./46

Государственный комнтет

СССР по делам нзобретеннй н открытнй (53} УДК 681.325 (088 ° 8) Опубликовано 231181. Бюллетень М 4З

Дата опубликования описания 2. 11181

П.С. Самарцев и Е.В. Лобанов (72) Авторы изобрет.ен и я

Институт физики высоких энергий AH казахской ССР (71) Заявитель (54) УСТРОЙСТВО ПЕРЕМЕННОГО ПРИОРИТЕТА

Изобретение относится к вычислительной технике н может быть использовано для организации систем иэ нескольких ЭВМ.

Известно устройство приоритета, содержащее регистр приоритета, дешифратор, блок выявления приоритетного разряда, счетчик, регистр сдвига и блок управления fl) .

Недостатком является низкая надежность °

Известно также устройство приоритета, содержащее регистр, дешифратор, коммутатор, шифратор, блок управления и блок разрешения конфликтных ситуа- 15 ций f2) .

Недостатком известного устройства являются низкие функциональные возможности.

Цель изобретения — расширение 20 функциональных возможностей за счет изменения приоритетных соотношений абонентов.

Поставленная цель достигается тем, что устройство переменного приоритета, содержащее блок из и регистров, блок нз и дешифраторов, блок управления, коммутатор, шифратор, причем группа информационных входов блока регистров является группой информа- 30 ционных входов устройства, группа разрядных выходов блока регистров соединена с группой входов блока дешифраторов, содержит дна блока элементов И, блок элементов ИЛИ, блок элементов НЕ, блок контроля, причем первая группа управляющих входов блока регистров является группой управляющих входов устройства, первая по и-ую группы выходов блока дешифраторов соединены с первой группой входов первого блока элементов И, с первой по и-ую группами входов блока контроля и с первой по и-ую группами информационных входов блока управления, Вторая группа входов первого блока элементов И соединена с группой за-. просных входов устройства, группа выходов первого блока элементов И соединена с первой группой входов коммутатора и с группой входов блока элементов ИЛИ, вторая группа входов коммутатора соединена с группой выходов второго блока элементов И, группа выходов блока элементов ИЛИ соединена с группой входов .блока элементов НЕ, с группой входов шифратора и с первой группой входов второго блока элементов И группа выходов . блока элементов НЕ соединена с груп-

883906 пой входов второго блока элементов

И, выход блока контроля является выходом ошибку устройства, группа выходов шифратора соединена с (и+1) -ой группой информационных входов блока управления, управляющий вход шифратора соединен с входом занятости уст1 ойства, вторая и третья группы управ яющих входов блока регистров соединены соотэественно с первой, второй группами управляющих выходов блока управления, группа выходов блока конт роля соединена с группой входов первого блока элемента И.

Кроме того, блок контроля содержит

k мажоритарных узлов, где k — количество выходов в каждой группе выходов блока дешифраторов, элемент ИЛИ, элементов НЕ, причем каждый вход

i-го мажоритарного элемента соединен с i-ым входом i-ой группы входов блока, выход каждого мажоритарного элемента соединен с соответствующим входом элемента ИЛИ, выход которого соединен с выходом блока, выход каждого i-го мажоритарного элемента соединен с i-ым выходом группы выходов блока через i-ый элемент НЕ;.

Кроме того, блок управления содержит 2п каналов, а в каждом канале k элементов И, и элемент ИЛИ, причем первый вход каждого i-ro элемента И

i-го канала соединен с i-ым входом (n + 1)-ой группы входов блока, второй вход каждого i-ro элемента И i-ro канала соединен с i-ым входом i-ой группы входов блока групп входов с первой по и- ую, выходы.эле«й» ментов ИЛИ каналов с первого no — ый

2 являются группой вычитающих выходов блока, выходы элементов ИЛИ каналов с — + 1 по и-ый являются группой сум.п

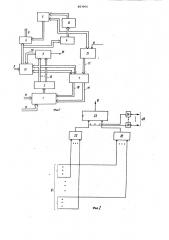

2 мирующих входов блока, На фиг, 1 приведена структурная схема устройства; на фиг. 2 — структурная схема блока контроля; на фиг. 3 — структурная схема блока управления.

Устройство содержит блок 1 регистр ов блок 2 дешифраторов, блок 3 конт

5 роля, блок 4 элементов ИЛИ, блок элементов И, коммутатор 6, блок 7 управления, группы выходов 8 блока дешифраторов, группа запросных входов 9 устройства, выход 10 ошибки устройства, группы информационных выходов 11 устройства, блок 12 элементов НЕ, блок 13 элементов И, группа управляющих входов 14 устройства, группа информационных входов 15 устй тва вход 16 занятости устройств группа выходов .17 шифратора, группы управляющих выходов 18 и 1

19 блока .управления, группа выходов ов 20 блока контроля и шифратор 21.

Блок контроля содержит мажоритарные узлы 22, элемент ИЛИ 23 и элемен ты НЕ 24. Блок управления содержит элементы И 25, элементы ИЛИ 26 и каналы 27.

Устройство работает следующим о6разом.

Коды приоритетов абонентов поступают в устройство по группе входов

15 и по сигналам управления, поступающим по группе входов 14, записываются в блок 1 регистров. Коды приоритетов, записанные в блоке 1, расшифровываются в блоке 2 и по группам выходов 8 блока 2 информация поступает в блок 13, в блок 3 и в блок 7.

В блоке 3 происходит контроль информации и если с двух или более выхо дов групп выходов 8 поступит одинаковая информация, то блок контроля по группе выходов 20 выдает блокирующие сигналы в блок 13 и запрос, поступающий по группе входов 9 в блок 13, обN рабатываться не будет, т. е. в двух или более регистрах блока 1 записаны одинаковые коды. В этом случае блок

3 по выходу 10 выдает сигнал ошибки и .управляющая ЭВМ производит перезаг2 рузки блока 1.

Если блок 3 не зафиксировал ошибочной ситуации, то запрос, поступивший по группе входов

9 в блок 3, проходит на выход этого р© блока и через коммутатор 6 при на личии сигнала от блока 5 на группу выходов 1.1 устройства. Информация с выхода блока 13 поступает в блок 4, а с выхода этого блока через блок 12 у и блок 5 наиболее приоритетный сигнал проходит с группы выходов блока

5 в коьвеутатор б, а с выхода 11 этого коммутатора — к абоненту. Если во время передачи запроса абоненту канал связи между устройством перемен4О ного приоритета и абонентом занят, то в устройство поступает сигнал по входу 16 занятости канала связи. По этому сигналу информация, поступившая на группу входов шифратора 21 с блока

45 4, зашифровывается и с группы выходов

17 шифратора 21 поступает в блок 7 управления. Блок управления обрабатывает эту информацию и информацию, поступившую с блока 2 дешифраторов

$O таким образом, что если сигнал занятости пришел перед передачей более приоритетного запроса более, то по группе выходов 18 в блок 1 выдается сигнал, уменьшающий содержимое соотг ветствующего регистра блока 1, и по группе выходов 19 — сигнал, увеличивающий содержимое соседнего регистра.

Таким образом, приоритет абонента, выставившего запрос, но не обслуженного в силу занятости канала связи, увеличивается, а приоритет следующего абонента уменьшается.

Применение предлагаемого изобретения позволяет расширить функциональ- у ные возможности устройства за счет

883906 оперативного изменения приоритетов абонентов и повысить надежность устройства за счет фиксации ошибочных ситуаций с помощью блока контроля.

Формула изобретения

Ф

1. Устройство переменного приоритета, содержащее блок из и регистров, блок из п дешифраторов, блок управления, коммутатор, шифратор, причем группа информационных входов блока регистров является группой информационных входов устройства, группа разрядных выходов блока регистров соединена с группой входов блока дешиф- >5 раторов> о т л и ч а ю щ е е с я тем, что, с целью расширения функциональ-ных:возможностей за счет изменения приоритетных соотношений абонентов, оио содержит два блока элементов И, ;ф блок элементов ИЛИ, блок элементов

НЕ, блок контроля, причем первая группа управляющих входов блока регистров является группой управляющих входов устройства, первая по и-ую группы выходов блока дешифраторов соединены с первой группой входов первого блока элементов И,.с первой по и-ую группами входов блока контроля и с первой по и-ую группами информа ционных входов блока управления, вторая группа входов первого блока элементов И соединена с группой запросных входов устройства, группа выходов первого блока элементов И соединена с первой группой входов коммутатора

И и с группой входов блока элементов

ИЛИ, вторая группа входов коммутатора соединена с группой выходов второго блока элементов И, группа выходов блока элементов ИЛИ соединена с ф) группой входов блока элементов НЕ, с группой входов шифратора и с первой группой входов Второго блока элементов И, группа выходов блока элементов НЕ соединена с группой вхоДов 4> второго блока элементов И, выход бло-. ка контроля является выходом ошибки устройства, группа выходов шифратора соединена с (и+1)-ой группой информационных входов блока управления, управляющий вход шифратора соединен с входом занятости устройства, вторая и третья группы управляющих вхо-. дов блока регистров соединены соответ" ственно с первой, второй группами управляющих выходов блока управления, группа выходов блока контроля соединена с группой входов первого блока элементов И.

2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок контро" ля содержит k мажоритарных узлов (k — количество выходов в каждой группе выходов блока дешифраторов), элемент ИЛИ, k элементов НЕ, причем каждый вход i-го.мажоритарного элемента соединен с i-ым входом i-ой группы входов блока, выход каждого мажоритарного элемента соединен с соответствующим входом элемента ИЛИ, выход которого соединен с выходом блока, выход каждого i-го мажоритарного элемента соединен с i-ым выхо-. дом группы выходов блока через i-ый элемент НЕ.

3. Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок управления содержит 2п каналов, а в каждом канале k элементов И и элемент .ИЛИ, причем первый вход каждого i-ro элемента И i-го канала соединен с

i-ым входом (и+1)-ой группы входов блока, второй вход каждого i-го эле мента И i-ro канала соединен с i-ым входом i-ой группы входов блока с первой по п-ую, выходы элементов ИЛИ и каналов с первого по --ый являются

2 группой вычитающих входов блока, выходы элементов ИЛИ каналов с -+ по и-ый являются группой суммирующих входов блока.

Источники информации, принятые во внимание при экспертизе

1.. Авторское свидетельство СССР

9 450174, кл G 06 F 9/18, 1972.

2. Авторское свидетельство СССР

В 512470, кл. 6 06 F 9/18, 1973 (прототип) .

883906

Составитель И. Кудряшев

Редактор Н . Рогулич Техред Ж.Кастелевич Корректор H. швьРiкая

° Фю

Заказ 10233/74 Тираж 748 .Подписное

"ВНИИПИ Государственного комитета СССР по делам изобретений,и открытий

ll3035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. ужгород, ул. Проектная, 4 . °