Вычислительный узел сеточной модели для решения дифференциальных уравнений в частных производных

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТО@СКОМУ С ТВЛЬСТВУ (61) Дополнительное к а|т. сей.-ву(22) Заявлено 29ЯЗ80. (21) 2898777/18-24 с присоединением заявки Nt(23) Приоритет

Соег Соаетскии

Социалистических

Ресоубли@ о1883913 (я)м. кл.з

G 06 F 15/32

Гесуяярственкмй квинтет

СССР яе Ааваи кзебретеняй я открытий

Опубликовано 2яд1я1.бюллетень Н9 (53) УДК681. 3 (088. 8) Дата опубликования описания 2311.81 (72) Лвторы игобретенмя

Р.H.Êàìàåâ, Ю.Н..Коломийцев, И.A.Френкель к Ю.М.Санько

Куйбышевский политехнический институт им.В.В.Куйбышева (71) Заявитель (54) ВЫЧИСЛИТЕЛЬНЫЙ УЗЕЛ СЕТОЧНОЙ МОДЕЛИ

ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ

В ЧАСТНЫХ ПЗОИЗВОДНЫК

Изобретение относится к области вычислительной техники к предназначено для моделирования уравнений в частных производных, в частности ти- . па теплопроводности.

Известны вычислктелъные узлы сеточных моделей (13 .

Оцнако известные устройства отличаются сложностью конструкции и ограниченным быстродействием, что обус- 10 .ловлено последовательным выполнением вычислительных и логических операций;

Наиболее близким по технической сущности к изобретению является вычислительный узел цифровой модели-,И сетки для решения дифференциальных уравнений в частных производных, содержащий многовходовой сумматор, входы которого соединены с информа» ционными входами узла, регистр сдви- 20

ra, управляющий вход и последовательный выход которого соединены соответственно с первым управляюцим входом узла и элемента И, группу элементов H входы и выходы которых сое- 2$ динены соответственно с выходом регистра сдвига, входом к выходом узла, а вторые входы элементов группы элементов И соединены с третьим управляющим входом узла, блок умноже- 39 ния, последовательный вход, параллельные входы и выход которого соединены

cooTBsTcTBBHHG c выходом многовходового сумматора; с кодовыми входами узла и последовательным входом регистра сдвига (2).

НедОстатками устройства являются сложность конструкции узла и моделей на его основе, особенно много.мерных, болъшив затраты времени при жщелировании, обусловленные последовательным выполнением арифметических и логических операций в процессе счета, сложность обеспечения устойчивости решения вследствие возникновения гонок в комбинацкокных цифровых жщвлях с обратньааи связями, особенно в многомерном случае, необходкмость существенных изменений не только в связях, но и в кочструкцки блоков при изменении разности задачи и моделирование только с постоянным равномерным шагом дискретизации.

В результате этого резко сужается область применения и эксплуатационные качества известного устройства.

Цель изобретения - повъыенив быстродвйствия и расширение класса ре883913 шаемых функций за счет возможности моделирования с произвольным шаroM дискретизации .

Поставленная цель достигается тем, что в вычислительный узел се точной модели для решения дифференциальных уравнений в частных производных, содержащий многовходовой сумматор и умножитель, содержащий группу цнфроаналоговых преобразователей, причем аналоговые входы цифроаналоговых преобразователей группы являются соответствующими информационными входами вычислительного узла, выходы цифроаналоговых преобразователей группы соединены с соответствующими входами группы входов мно. — 15 говходового сумматора, выход которого является выходом вычислительного узла, дополнительно введены блок регистров и блок задания констант, вы1 од которого соединен со входом ана- 2О логового многовходового сумматора, а вход блока задания констант подключен к выходу блока регистров, группа выходов которого соединена с цифровыми входами соответствующих цифроана-25 логовых преобразователей группы, вход блока регистров является управляющим цифровым входом вычислительного узла..

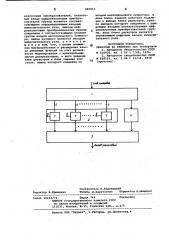

На чертеже представлена блок-схема вычислительного узла.

Узел содержит блок регистров 1, блок 2 умножения, выполненный на цифроаналоговых преобразователях, аналоговый многовходовой сумматор 3, блок задания констант. 4, входы 5 и 6, груп-З5 пу цифроаналоговых преобразователей 7.

Блок 1 регистров представляет собой набор цифровых регистров памяти с параллельным вводом и выполняется, например на триггерах. 40

Блок 2 умножения выполнен на цифроаналоговых преобразователях. Многовходовой сумматор 3 выполнен на аналоговом принципе и представляет собой многовходовой операционный усилитель. 45

Блок 4 может быть выполнен иа цифроаналоговом преобразователе с фиксированным опорным напряжением.

Рассмотрим работу вычислительного узла сеточной модели на примере ре- яо шения 3-х мерного уравнения Фурье с источником (аХ а а J йппроксимируем 1) на 8-ми точеч- 55 ном нерегулярном шаблоне

0" "-А 6 1 ) 6 б1 ° 5 | б1 9бб1

)+бл х "3М 60 где А»

1

Х» б ) д l eL Õ, "Х+б "Х )

) l

) 1 dQ +1 б 1 2 {,"2+hi ) l cA b б1 )

C > < %, ;-(- ф,2 1, t *

1 б 1, 1 +x+ »» ) (»„ »„) » -» » 1

»

1-1 ", .J=1 )»1,1..... 1 ) К g Я . К- !

Уравнение (2) записано относительно узла с номером i, j, k. Блок-схема узла представляет собой непосредственную реализацию уравнения (2) .

Значение К в форме параллельного цифрового кода задается в блок 1 регистров, который управляет блоком

4. На выходе блока 4 присутствует значение Р„,К в аналоговой форме: оно поступает на один из входов аналогового сумматора 3.

Все коэффициенты уравнения (2):

A ), А В, В, С, С также задаются в виде цифрового кода в блок 1 регистров, который служит для хранения информации. Коды коэффициентов из блока 1 регистров поступают на входы 5 блока 2 умножения, на входы 6 которого в аналоговой форме подаются значения неизвестных с выходов сумматоров 3 других узлов модели.

Величины неизвестных и кодов коэффициентов перемножаются цифроаналоговыми преобразователями блока 2 умножения, с выходов которого величины произведений, образующие правую часть уравнения (2), поступают на входы аналогового сумматора 3.

Очевидно, на выходе аналогового сумматора 3 формируется значение неиэвестногоЩ„ в аналоговой форме.

Вычислительный узел служит основой для создания сеточных моделей необходимой конфигурации и размерности.

Предлагаемый узел сеточной модели обеспечивает существенно большую скорость получения решения по сравнению с известным, так как процесс решения протекает в аналоговой форме.

Возможность моделирования с произвольным шагом дискретизации позволяет без дополнительных аппаратурных затрат решать задачи при весьма больших градиентах исследуемых физических, например, температурных полей.

Формула изобретения

Вычислительный узел сеточной модели для решения дифференциальных уравнений в частных производных, содержащий многовходовой сумматор и умножитель, содержащий группу цифро88391 3

Составитель В.Аедоницкий.

Техред E.баритончик КЬрректор Н.Швьщкая

Редактор В.Еремеева

Заказ 10233/74 Тираж 748 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 13035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", г.ужгород, ул.Проектная,4 аналоговых преобразователей, аналого« вые входы циФроаналоговых преобразователей группы являются соответствующими информационными входами вычислительного узла, выходы цифроаналоговых преобразователей группы соединены с соответствующими входами группы входов многовходового сумматора, выход которого является выходом вычислительного узла, о т л и ч а юшийся тем, что, с целью повыше« ния быстродействия и расширения класса решаемых функций за счет воэможности моделирования с произвольным шагом дискретизации, в него введены блок регистров и блок задания констант, выход которого соединен со входом многовходового сумматора, а вход блока задания констант подключен к выходу блока регистров, груп-. па выходов которого соединена с цифровыми входами соответствующих цифроаналоговых преобразователей группы, вход блока регистров является управляющим цифровым входом вычислительного узла.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

В 510925, кл. G 06 G 7/48, 1976.

2 Авторское свидетельство СССР

В 608165, кл. G.06 F 15/32,,1978 (прототип).