Множительно-делительное устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

Союз Соввтскии

Социайистичасник

Республин

<1>883920 (61) Дополнительное к авт. сеид-ву а 674042 (22) Заявлено 25,0280 (21) 2885423/18-24 с присоединением заявки Н9 (23) Приоритет

Опубликовано 2311 1 бюллетень Мо 43

Дата опубликования описания 231181 (51)М, Кл

G G 7 16

Государственный комитет

СССР по делам -изобретений и открытий (53) УДК 681. 335 (088.8) (72) Авторы изобретения

В.А. афаиасаен, Л.H. Инаиана, В. и. КалЬ лийЪ;И --ЛануГин

В.A. Овчеренко и B.H. Соболе

Новосибирский электротехнический инстигут

1 (71) Заявитель (54)МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ.УСТРОЙСТВО

Изобретение относится к области вычислительной техники и может быть использовано в качестве множитЕльноделительного устройства в гибридных вычислительных машинах.

По основному авт. св. 9 674042 известно множительно-делительное устройство содержащее реверсивный счетчик, прямой и реверсивный входы которОго связаны с соответствующими выходами переключателя, вход которого подключен к выходу элемента И, первый вход которого соединен с выходом тактового генератора, а второй— с соответствующим выходом генератора

15 синхроимпульсов, управляющий вход переключателя подключен.к выходу компаратора, выходы разрядов реверсивного счетчика соединены с соответствующими входами цифроаналогового преобразователя, аналоговый вход которого через первый и второй ключи связан соответственно с входами первого сомножителя и делителя, выход цифроаналогового преобразователя связан с первым входом компаратора и через третий ключ — с входом первого элемента памяти, через четвертый к ч вд перво элемента "ти 30 соединен с аналоговым входом цифроаналогового преобразователя, второй вход ком соединен через пятый. ключ с входом второго сомножителя,а через шестой ключ — с выходом первого элемента памяти, выход цифроаналогового преобразователя через седьмой ключ связан с входом второго элемента памяти, входы начальной установки реверсивного счетчика являются цифро"выми входами -устройства, выходы элементов памяти являются аналоговыми выходами, а выходы реверсивного счетчика являются цифровым выходом устройства, управляющие входы ключей и реверсивного счетчика подключены к соответствующим выходам генератора синхроимпульсов (1j .

Это устройство позволяет выполнить не более двух множительно-делительных операций эа 1 цикл, т.е. вычисляХ, Xg ют функции вида — ", или Х„

11 4 "1

Цель - изобретения — расширение функциональных воэможностей устройства за счет обеспечения вычислений функций вида т„.Х,1.... Х„

Y1. Yll- - -.ytn

Поставленная цель достигается тем, что в множительно-делительное устрой3

883920 ство введены два дополнительные ключа, управляющие входы которых подсоединены к соответствующим выходам генератора синхроимпульсов, информационные входы объединены и подключены к выходу второго элемента памяти, выход первого дополнительного ключа подключен к аналоговому входу цифроаналогового преобразователя, а выход второго дополнительного ключа подключен ко второму входу компарат-ора.

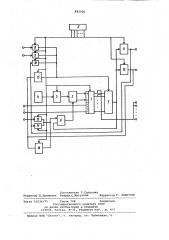

Яа чертеже представлена блок-схема множительно-делительного устройства.

Иножительно-делительное устройство содержит реверснвный счетчик 1, прямой и реверсивный входы которого связаны с соответствующими выходами переключателя 2, вход которого подключен к выходу элемента И 3, первый вход которого соединен с выходом тактового генератора 4, а второй вход— с соответствующим выходом генератора синхроимпульсов 5, управляющий вход переключателя 2 подключен к выходу компаратора 6, выходы разрядов реверсивного счетчика 1 соединены с соответствующими входами цифроаналогового преобразователя 7, аналоговый вход которого через первый ключ 8 и второй ключ 9 связан соответственно с входом первого сомножителя (делителя) с опорным напряжением, а через первый дополнительный ключ 10— с выходом первого элемента памяти 11, выход цифроаналогового преобразователя 7 связан с первым входом компаратора 6 и с входами первого и второго элементов памяти 11 и 12. Второй вход компаратора 6 соединен через третий ключ 13 с входом второго сомножителя и через второй дополнительный ключ 14 с выходом первого элемента памяти 11. Входы начальной устаиовки реверсивного счетчика 1 являются цифровыми входами устройства, выходы элементов памяти 11 и 12 являются аналоговыми выходами, а выходы реверсивного счетчика 1 являются цифровым выходом устройства.Сигнальные входы четвертого и пятого ключей 15 и 16 объединены и .подсоедииены к выходу второго элемента памяти 12, выход четвертого ключа 15 соединен с аналоговым входом цифроаналогового преобразователя 7, выход пятого ключа 16 соединен со вторым входом компаратора 6, управляющие входы всех ключей элемеитов памяти и рзверсивного счетчика 1 подключены к соответствующим выходам генератора синхроимпульсов 5.

Множительно-делительное устройство работает следующим образом..

Генератор синхроимпульсов 5 через ключи 8, 9 и 10 и ключ 15 подключает к аналоговому входу преобразователя 7 в соответствующем поряд-.

t0

d0 ке Е входные сигналы сомножителей делимого Х (делителя У ) или промежуточный результат преобразования, хранящийся в одном иэ элементов в памяти 11 и 12. Через ключи 13, 14 и 16 ко входу компаратора 6 генератор 5 подключает в соответствующем порядке входные сигналы сомножителей делимого Х л(делителя Ул) или -промежуточный результат преобразования, хранящийся в одном из элементов памяти 11 и 12.

Рассмотрим работу устройства для случая, когда необходимо получить произведение величины 2„=Х1л-ХЯ МЪ„Õ1I.XII X%I...X1< Xg< ХЗ (q) где Хл;,XC .X9; - сигнал сомножителей но нервом, второму, третьему входам устройства соответственно.

На вход компаратора 6 подается сигнал первого сомножителя Х1 на аналоговый вход преобразователя 7 подается Е . На тактовый вход счетф0 чика 1 поступают импульсы и производится цикл преобразований аналогового сигнала ХЛ„и выходной двоичный .код счетчика 1йл.

Затем подключается сигнал второго сомножителя Х9 к аналоговому входу преобразователя 7. Результат преобразования

2 =й„ X2„=X<„XI„(2) заполняется элементом памяти 11.Следующий сомножитель Х в цифровом коде заносится через входы начальной установки в реверсивный счетчик 1.На аналоновый вход преобразователя 7 подается результат преобразования по формуле (2) с элемента памяти 11.

Результат преобразования по формуле

Z =-2 а„=Х1„йл Х „(3) заносится в элемент памяти 12.

Затем подается следующий сомножитель Х1 1 на вход компаратора 6, к ана- логовому входу преобразователя 7 подключается Е д . Производится цикл преобразований аналогового сигнала Хл в выходной двоичный код счетчика 1, после чего на аналоговый вход преобразователя 7 подключается результат преобразования по формуле (3), хранящейся в элементе памяти 12. Результат преобразования по формуле

Z 2 ХЛ =Х „Ха, ХЭл Л (4) запоминается элементом памяти 11.Затем подается следующий сомножитель

Х2 и т.д. до получения результата по формуле (1).

Рассмотрим работу устройства для случая, когда необходимо произвести вычисления по формуле

2л р ()

Промежуточный результат вычисле" ний 2„ хранится в элементе памяти 11.

883920

Сомножнтвль делителя У1 подается на аналоговый вход преобразователя

7, делимое 2 „ из элемента памяти 11 через ключ 14 подается на вход компаратора 6. Резельтаты.преобразования по формуле

«21 5

Н1=—

Yi1 (6) на выходе счетчика 1 преобразуется затем в аналоговую форму, для чего на аналоговый вход преобразователя

7 подается Ес через ключ 9. После Е цикла преобразований кода k 1 в аналоговую величину получена на выходе преобразователя 7 результат по формеле

25= 4 оз (7)

1$ который запоминается элементом памяти 12..

Затем сигнал второго сомножите-. ля делителя У31 з цифровом коде 2© через входы начальной установки заносится в реверсивный счетчик 1.Подается на аналоговый вход преобразователя 7 Eqn, цифровой код УЗ пре" образуется в аналоговую величину и запоминается в элементе памяти 12.

Затем делимое 2 из элемента памяти 12 через ключ 16 подается на вход компаратора 6, а делитель

УЪ„ из элемента памяти 11 через ключ 10 подается на аналоговый вход . преобразователя 7.

Результат деления

2.<

И,,, =ц-.щ; — (8) преобразуется затем в аналоговую форму, для чего на аналоговый вход преобразователя 7 подключается Е и анаOII логовый результат запоминается в элементе памяти 11.

Следукщий сомножитель делителя 40

УЙ поступает через ключ 8 на аналоговый вход преобразователя 7,,проме-. жуточный результат предыдущего преобразования по формуле (8) через ключ 13 поступает на вход компаратора 6, после преобразования по формуле Ъ

"Ъ Ч2 а„ Е„ 1 (9)

Цифровой коД ИЗсчетчика 1 пРеобРаэУется в аналоговую величину и запоминается элементом памяти 12.

Затем подав. ся следующий сомножитель делителя 9 и т.д. до получения конечного зультата по формуле (5).

Таким образом, множительно-двлительное устройство позволяет выполнять умножение и деление без ограничения количества сомножителей и делителей. формула изобретения йножительно-делительное устройство по авт.cs. 9 674042; о т л ич а ю щ е е с я тем, что, с целью расширения функциональных возможностей эа счет обеспечения вычислений ,х,х<- -"х, функций вида, „,, в него

I7I введены два дополнительные ключа, управляющие входы которых подключены к сбответствувщим выходам генератора синхроимпульсов, информационные входы объединены и подключены к выходу второго элемента памяти, выход первого дополнительного ключа подключен к аналоговому входу цифроаналогового преобразователя, выход второго дополнительного ключа подключен ко второму входу компаратора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР ."1 674042, кл. С 06С 7/16, 1976 (прототип) .

883920

Составитель Т.Сапунова

Редактор B.Еремеева Техред C.Ìèróíoâà Корректор Г. Решетник

Заказ 10234/75

Тираж 748 Подписное

Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4