Линейный интерполятор

Иллюстрации

Показать всеРеферат

ОЙИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВН ЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (51)М К 3 (22) Заявлено 030380 {21) 2930739/18-24 (032032) с присоединением заявки М

6 06 G 7/30

Государственный комитет

СССР

IIo делам иэобретений и открытий (23) Приоритет (5З) УДК 681. 335 (088. 8) .Опубликовано 231181 Бюллетень Йо 43

Дата опубликован и я описания 2 31181 (72) Авторы изобретения

В.Н. Коробейников и A.Ф. Кургаев

Ордена Ленина институт кибернетики АН --Украинской ССР (71) Заявитель (54) ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР

Изобретение относится к области вычислительной техники и может быть использовано для воспроизведения функций при выводе информации на электронно-лучевые трубки, графопостроители и исполнительные механизмы в управляющих вычислительных системах.

Известно интерполирующее устройство, содержащее регистр, выход которого соединен с параллельными цепочками, каждая из которых содержит последовательно соединенные цифроаналоговый преобразователь и интерполяTîð 111 ° 15

Недостатком этого устройства явля-. ется низкая точность воспроизведения функций, связанная с неточностью работы интерполяторов, с накоплением ошибок интегрирования. 20

Наиболее близким по технической сущности и предлагаемому является линейный интерполятор с двумя аналоговыми запоминающими устройствами,содержащий регистр, соединенный с параллельными цепочками, в каждой иэ которых вход цифроаналогового преобразователя соединен с выходом регистра, а выход соединен с первым входом сумматора, выход которого через ключи30 соединен со входами аналоговых запоминающих устройств. Выходы аналоговых запоминающих устройств через ключи соединены со входом интегратора, чей выход соединен со вторым входом сумматора. Выход интегратора является выходом цепочки (2j .

Недостатком устройства является большой объем оборудования.

Цель изобретения — сокращение объема оборудования.

Поставленная цель достигается тем, что линейный.интерполятор, содержащий последовательно соединенные регистр и цифроаналоговый преобразователь, выход которого подключен ко входам каналов, каждый из которых состоит из сумматора, первый вход которого является входом соответствующего канала, а выход через первый и второй ключи соединен соответственно со входами первого и второго за- поминающих блоков, и интегратора, вход которого через третий и четвертый ключи подключен соответственно к выходам первого и второго запоминающих блоков, а выход соединен со вторым входом сумматора, р каждый канал,кроме последнего, введены дополнительные запоминающий блок и ключ, соеди883925!

О

35

ЬО ненные последовательно и включенные между выходом интегратора и третьим входом сумматора.

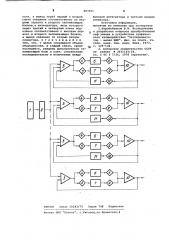

На чертеже представлена структурная схема линейного интерполятора.

Линейный интерполятор содержит регистр 1, выход которого соединен со входом цифроаналогового преобразователя 2. Выход цифроаналогового преоб-. разователя 2 соединен с первыми нхоцами сумматоров 3 параллельных каналов, в каждом из которых выход сумматора 3 через ключи 4 и 5 соединен со входами запоминающих блоков

6 и 7, чьи выходы через ключи 8 и

9 подключены ко входу интегратора

10. Выход интегратора 10 соединен со вторым входом сумматора 3 этого канала, третий вход которого в каждом из каналов, кроме последнего, подключен к выходу дополнительного запоминающего блока 11, чей вход через ключ 12 соединен с ныходом интегратора 10. Выходы интеграторов

10 являются выходами каналов и выходами интерполятора.

Интерполятор работает следующим образом.

До момента окончания очередного цикла интерполирования функций ключи

12 всех параллельных каналов замкнуты и в дополнительные запоминающие блоки 11 записываются напряжения с выходов интеграторов 10. В момент . времени окончания очередного цикла интерполирования с1, ключи 12 размыкаются и на выходе дополнительных. запоминающих блоков 11 устанавливаются напряжения, равные по величине, но протиноположные по знаку напряжению на выходах интеграторов 10. B этот же момент времени на выходе одного из запоминающих блоков, например 7, сформировалось напряжение, равное по величине приращению функции p x (t-.„) = x <(t;+„) -х (с() на интервале времени t<(t„, t +„) . В момент времени t замыкаются ключи 9 всех

1 параллельных каналов и ключ 4 первого канала. Остальные ключи генератора функций разомкнуты. В этот же момент времени на регистре 1 от электронной вычислительной машины поступает цифровое значение функции х (с„ о) .

Это значение преобразуется цифроаналоговым преобразователем 2 в соответствующее значение напряжения 0 » ах „(с; <)), где а коэффициент пропорцйональности. Это напряжение поступает на первый вход сумматора 3 первого канала и всех последующих.На второй вход сумматора 3 первого канала поступает линейноизменяющееся напряжение с выхода интегратора 10, которое имеет следующий вид

"А )- И ц - » (. — : —.»)»»(»;,»; „1

На третий вход сумматора 3 первого канала поступает постоянное напряжение с выхода дополнительного запоминающего блока 11, которое равно

0 1 = ах.,(с„) .

На выходе сумматора 3 первого канала формируется напряжение

0 с101 к 1О к3Ц т . т-ь где К„= 1, К 2 =, К =- — — козфь1 фициенты передачи сумматора 3 первого канала по соответствующим входам.

С учетом коэффициентов передач сумматора 3, а также выражений для

U», О, U 1„, напряжение на выходе сумматора 3 первого канала в момент времени t;+ d t будет равно

"ъ=-с(Х1{ +1)- { 1+,)l т.е. равно приращению функций х (с) на следующем интервале интерполйрования. В момент времени t; + д t ключ 4 первой цепочки размыкается и в аналоговом запоминающем устройстве 6 фиксируется напряжение

U = а (1„{,+ )- Х„(„«)) В этот же момент времени замыкается ключ 12 первой цепочки и в дополнительное аналогоное запоминающее устройство 11 этой цепочки вплоть до окончания цикла интерполирования, т.е. до момента времени t +,производится запись напряжения с выхода интегратора 10.

В момент времени с + д с замыкается ключ 4 второй цепочки и одновременно на регистр 1 от электронной вычислительной машины поступает цифровое значение функции. Описанный процесс работы повторяется до окончания процесса интерполяции функций кусочно-линейными напряжениями.

Положительный эффект достигнут за счет введения в каждый параллельный канал, кроме последнего, дополнительного запоминающего блока 11, ключа

12 и связей между узлами.

Благодаря данному предложению в устройстве используется только один цифроаналоговый преобразователь, а разрядность регистра уменьшена с

man до m, где в - разрядность представления в цифроном коде одной функции хк(с), а и — количество параллельных цепочек.

Формула изобретения

Линейный интерполятор, содержащий последовательно соединенные регистр и цифроаналоговый преобразователь, выход которого подключен ко входам каналов, каждый из которых сос:тоит из сумматора, первый вход которого является входом срответствующего ка883925

ВНИИПИ Заказ 10243/75 Тираж 748 Подписное

Филиал ППП "Патент", г.ужгород,ул.Проектная,4 нала, а выход через первый и второй ключи соединен соответственно со входами первого и второго запоминающих блоков, и интегратора, вход которого через третий и четвертый ключи подключен соответственно к выходам первого и второго запоминающих блоков, а выход соединен со вторым входом сумматора, отличающийся тем, что, с целью сокращения объема оборудования, в каждый канал, кроме последнего, введены дополнительно за-. поминающий блок и ключ, соединенные последовательно и включенные между выходом интегратора и третьим входом сумматора.

Источники информации, принятые во внимание при экспертизе

1.Коробейников В.Н. Исследование и разработка вопросов преобразования информации в устройствах графического взаимодействия "Экспериментатор — малая ЦНИ". Дис. на соиск. уч. степ. канд. тех. наук, Киев, 1973, с. 129"134.

2. Авторское свидетельство СССР по заявке Р 2631141/24, кл. С 06 6 7/26, 1978 (прототип).