Устройство определения фазы с наименьшим напряжением

Иллюстрации

Показать всеРеферат

О Il И С А Н И Е (884022

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Ресттубпин (6l) Дополнительное к авт. свид-ву— (22) Заявлено 25.08.78 (2l ) 2656998/24-21 (5l) М. Кл а с присоединением заявки №вЂ”

Н 02 h 3/!6 (23) Приоритет—

Государственный комнтет

Опубликовано 23.! l.8l. Бюллетень № 43 (53) УДК 62l.317..322(088.8) па делам нзобретеннй н открытий

Дата опубликования описания 28.ll.81 (72) Авторы изобретения (7I ) Заявители

ШЯ " (54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ФАЗЫ

С НАИМЕНЬШИМ НАПРЯЖЕНИЕМ

Изобретение относится к области электроизмерительной техники и может быть использовано для определения фазы с возросшей проводимостью изоляции в трехфазных сетях с нзобированной нейтралью.

Известно устройство для контроля симметрии трехфазного напряжения источника питания регулируемого электропривода, содержащее трансформаторы напряжения с выпрямителями, включенные на входы диодных логических блоков И н ИЛИ, выходы которых подключены к блоку сравнения, соединенному с реагирующим органом )l).

Однако это устройство, выделяя минимальное из трех напряжений, не указывает фазу с наименьшим напряжением.

Известно устройство для определения поврежденной фазы, содержащее фильтр напряжения нулевой последовательности и три пороговых элемента, реагирующих на повышение напряжения, причем пороговые элементы подключены к фазам контролируемой сети и через фильтр напряжения нулевой последовательности к искусственной нулевой точке (2).

Однако устройство надежно срабатывает при значительном напряжении нулевой

2 последовательности, определяющем зону нечувствительности устройства.

Цель изобретения — повышение чувствительности посредством устранения зоны нечувствительности устройства.

Цель достигается тем, что в устройство для определения фазы с наименьшим напряжением, содержащее три пороговых элемента, введены электронный ключ, нагрузочный резистор, источник питания с ключом и три интегрирующих цепочки с двумя группами ключей по два в каждой фазе, а каждый пороговый элемент выполнен в виде двух электрических цепей, первая нз которых состоит из последовательно соединенных резистивного делителя напряжения, динистора н выхода дифференциального фотореэисторного оптрона, а вторая цепь состоит иэ последовательно соединенных выхода фототиристорного оптрона, светодиода, входа фототиристорного оптрона и ограничивающего ток резистора, причем анод светодиода соединен со средней точкой делителя, рр вход дифференциального оптрона соединен между источником питания и коллектором транзистора электронного ключа, вход которого соединен с общей точкой ограничи884022

1о

2О

25 зо

Формула изобретения

55 вающих резисторов и нагрузочного резистора, входы интегрирующих цепочек через первую группу ключей соединены с фазными напряжениями, а их выходы с выходами фоторезистивных оптронов и через вторую группу ключей с общей шиной устройства, выходы фототиристорных оптронов объединены и соединены через ключ с источником питания, а конденсаторы интегрирующих цепочек, резистор нижнего плеча делителя и нагрузочныи резистор вторыми концами, соединены с общей шиной устройства.

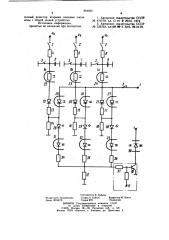

На чертеже приведена принципиальная схема устройства.

Устройство для определения фазы с наименьшим напряжением содержит источник

1 питания, две группы ключей 2 и 3, интегрирующие цепочки, содержащие резистор 4 и конденсатор 5, резистор 6 и конденсатор 7; резистор 8 и конденсатор 9, электронный ключ 10, источник смещения ll, нагрузочный резистор 12, а каждый из пороговых элементов выполнен в виде двух электрических цепей, первая из которых состоит из последовательно соединенных резистивиых делителей напряжения, содержащих резисторы 13 -18, динисторов 19 — 21 и выходов

22 — 24, дифференци ал ьного фоторезисторпого оптрона, подключенного к выходу интегрирующей цепочки, а вторая электрическая цепь состоит иэ последовательно соединенных выходов 25 — 27 фототиристорного оптрона, светодиодов 28 — 30, входов 31 — ЗЗ фототиристорного оптрона и ограничительных резисторов 34 — 36, соединенных с нагрузочным резистором и через дополнительный резистор 37 со входом электронного ключа, причем анод светодиодов соединен со средней точкой . реэистнвных делителей напряжения, коллектор транзистора элект- 55 ронного ключа соединен через вход 38 дифференциального оптрона с источником питания, а входы интегрирующих цепочек через первую группу ключей 2 соединены с фаэными напряжениями U+, !.1, Uc,, а ключи второй группы 3 включены параллельно кон- 4о денсаторам интегрирующих цепочек.

Устройство работает следующим образом.

Фазные напряжения Ц, U, U через группу ключей 2 подключаются ко входу интегрирующих цепочек.

На конденсаторах 5, 7 и 9 происходит процесс нарастания напряжения, скорость нарастания которого пропорциональна уровням сравниваемых напряжений U, Ug, U .

Например, при U > Ug> U, первым пробьется динистор 19, что вызовет увеличение тока через резисторы 13, 14. При этом транзистор электронного ключа 10 открыт отрицательным напряжением смещения, ток течет через вход 38 оптрона, что обуславливает малое омическое сопротивление его выходов

22 — 24.

Увеличение напряжения на резисторе 14 вызовет срабатывание светодиода 28, фиксируя фазу с наибольшим напряжением, а также включается вход 31 фототиристорного оптрона, что приводит к включению выхо. да 25 упомянутого оптрона, в результате чего происходит самоблокировка предлагаемой электрической схемы. На резисторе 12 появляется положительный потенциал, недостаточный для закрытия транзистора ключа 10. Далее, исходя из заданного условия, срабатывает цепь фазы 1, что увеличивает падение напряжения на резисторе 12, которое становится достаточным для закрывания транзистора и, следовательно, проис- ходит выключение выходов 22 — 24 оптрона.

Таким образом, горят светодиоды 28 и

29, в то время как незажженный светодиод

30 указывает фазу с наименьшим напряжением.

Подготовка схемы к следующим измерениям производится отключением группы ключей 2 и кратковременным включением группы ключей 3.

Таким образом, уменьшение порога зоны нечувствительности достигается за счет точного сравнительного анализа амплитуд фазных напряжений.

Устройство для определения фазы с наименьшим напряжением, содержащее три пороговых элемента, отличающеегя тем, что, с целью повышения чувствительности, в него введены электронный ключ, нагрузочный резистор, источник питания с ключом и три интегрирующих цепочки с двумя групнами ключей по два в каждой фазе, а каждый пороговый элемент выполнен в виде двух электрических цепей, первая из которых состоит из последовательно соединенных резистивного делителя напряжения, динистора и выхода дифференциального фоторезисторного оптрона, а вторая цепь состоит из последовательно соединенных выхода фототиристорного оптрона, светодиода, входа фототиристорного оптрона и ограничивающего ток резистора, причем анод светодиода соединен со средней точкой делителя, вход дифференциального оптрона соединен между источником питания и коллектором транзистора электронного ключа, вход которого соединен с общей точкой ограничивающих резисторов и нагруэочного резистора, входы интегрирующих цепочек через первую группу ключей соединены с фазными напряжениями,.а их выходы с выходами фоторезисторных оптронов и через вторую группу ключей с общей шиной устройства, выходы фототиристорных оптронов объединены и соединены через ключ с источником питания, а конденсаторы . интегрирующих цепочек, резистор нижнего плеча делителя и нагру884022

lie

Составитель В. Дубков

Редактор Н. Пушнеикова Техред А. Бойкас Корректор М. Коста

Заказ 10246/79 Тираж 678 Подписное

ВНИИПИ Государственного комитета СССР по. делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП с Патент>. г. Ужгород, ул. Проектная, 4 зочный резистор вторыми концами соединены с об1цей шиной устройства.

Источники информации, принятые во внимание прн экспертизе

I. Авторское свндетельстео СССР № 470770, кл. G OI R 29/16, )974.

2. Авторское свидетельство СССР № 335763, кА-.1Я Эй; h 3/)5, 29.I070.