Устройство для умножения частоты следования импульсов

Иллюстрации

Показать всеРеферат

Союз Советскмх

Соцнапнстмческнх

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l ) Дополнительное к авт. свкд-ву (22) Заявлено 04.02.80 (2) ) 2877915/18-2 1. с присоединением заявки РЙ (23) Приоритет

Опубликовано 23. у 1.81 Бюллетень JA 43

Дата опубликования описания 26 ° 11 81 (5l)M. Кл.

Н 03 К 5/01

Государственный комитет по делам изаоретеиий и открытий (53) УДК 621.374. .4(088.8) (72) Авторы изобретения

H. И. Макаренко, В. Н. Буценко и И. Э. Рассказов (7l) Заявитель (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧАСТОТЫ

СЛЕДОВАНИЯ ИМПУЛЬСОВ

Изобретение относится к измерительной технике, автоматике и может быть использовано в измерителях частоты, в системах регулирования с частотными датчиками и других устройствах для умножения частоты.

Известен умножитель частоты периодических импульсов, содержащий опорный генератор и блок заполнения, к выходу опорного генератора подключен детю литель частоты с коэффициентом деления, равным требуемому коэффициенту умножения, а блок заполнения содержит два счетчика импульсов, первый подключен к делителю, а второй — к опорному

15 генератору, запоминающий элемент, подключенный к выходам ячеек первого счет чика, и элемент сравнения, подключенный к выходам ячеек запоминаюшего элемента и второго счетчика импульсов, выход элемента сравнения соединен с выходом умножителя и через элемент

ИЛИ вЂ” со входом установки нуля второго счетчика импульсов, причем вход умножителя соединен с входом установки нуля запоминающего элемента и линией задержки, часть которой подключена к входу считывания первого счетчика, а конец — к входам установки пуля делителя и первого счетчика импульсов, а также к второму входу элемента ИЛИ (1 )

Недостатком указанного умножителя является относительно низкая точность умножения из- за ошибки, возникаюшей при определении периода входной частоты.

Наиболее близким по технической сущности к изобретению является устройство умножения частоты следования импульсов, - содержашее управляющий блок, вход которого соединен с выходом входного формирователя, а первый выход - с установочным входом делителя частоты, генератор опорной частоты, выход которого подключен к первому управляюшему.входу ключа и к входу делителя частоты, блок умножения, состояший из

3 88 элемента ИЛИ и последовательно соединенных первого счетчика импульсов, запоминающего регистра, элемента переноса, второго счетчика импульсов и элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого объедиен с установочным входом первого счетчика импульсов и подключен к первому выходу управляющего блока, а выход — к управляющему входу элемента переноса, при этом вход первого счетчика импульсов соединен с выходом делителя частоты, вход запоминающего регистра — со вторым выходом управляющего блока, а вход второго счетчика — с выходом ключа, и блок коррекции, состоящий из одновибратора, первого элемента И и последовательно соединенных блока переноса, счетчика и второго элемента И, причем вход одновибратора соединен с выходом элемента И блока умножения, разрядные выходы делителя частоты подключены к входам элемента переноса блока коррекции, управляющий вход которого соединен с вторым выходом управляющего бло- ка, выход первого элемента И блока коррекции подключен к входу счетчика блока коррекции и ко второму управляющему входу ключа, первый вход — к выходу одновибратора, а второй вход - к выходу второго элемента И блока коррекции (2) .

Недостаток известного устройства— низкая надежность работы, Е1ель изобретения — повышение надежности работы устройства.

С этой целью в устройство для умножения частоты следования импульсов, содержащее управляющий блок, первый выход которого соединен с установочным входом делителя чатоты, генератор опорной частоты, выход которого подключен к счетному входу делителя часI тоты, блок умножения, состоящий из запоминающего регистра, управляющий вход которого подключен к второму выходу управляющего блока, а разрядные входы - к выходам первого счетчика импульсов, вход которого соединен с выходом делителя частоты, а установочный вход— с первым выходом управляющего блока и первым входом элемента ИЛИ, выход которого подключен к входу элемента переноса, к выходам которого подключены последовательно соединенные второй счетчик импульсов и элемент И, выход которого подключен к второму входу элемента ИЛИ, и блок коррекции, состоящий из по4102!

5 ными счетчиками.

35 ю

45 следовательно соединенных элемента переноса, разрядные входы которого подключены к разрядным выходам делителя частоты, а управляющий вход — к второму выходу управляющего блока, счетчик импульсов и элемента ИЛИ, выход которого подключен к первому входу элемента И блока коррекции, выход которого соединен с входом счет чика импульсов этого блока, введены синхронизатор и сумматор, первая группа входов которого соединена с выходами запоминающего регистра блока ум-! ножения, вторая группа входов — с шиной логического нуля, вход младшего разряда— с первым входом элемента И блока коррекции, а выходы — с разрядными входами элемента переноса блока умножения,, вход которого соединен с вторым входом элемента И блока коррекции, при этом первый вход синхронинизатора подключен к входной шине, второй вход — к выходу генератора опорной частоты и входу второго счетчика импульсов блока умножения, а выход — к управляющему блоку.

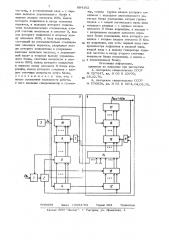

На чертеже. представлена структурная электрическая схема устройства.

Устройство содержит синхронизатор 1, выход которого подключен к входу управляющего блока 2, генератор 3 опорной частоты, делитель .4 частоты, блок коррекции 5 и бок умножения 6.

Блок коррекции 5 состоит из элемента И 7 и последовательно соединенных элемента 8 переноса, счетчика 9 импульса и элемента ИЛИ 10, Блок умножения 6 содержит элемент

ИЛИ 11 и последовательно соединенные первый счетчик 12 импульсов, запоминающий регистр 13, сумматор 14 элементы переноса 15, второй счетчик 16 импульсов и элемент И 17.

Делитель 4 и счетчик 12 являются суммирующими двоичными счетчиками, счетчики 9 и 16 - вычитаюшими двоичУстройство работает следующим образом.

Импульсы умножаемой частоты поступают на вход синхронизатора 1, При этом, перед каждым входным импульсом со сдвигом на интервал времени+I p))E>< появляется импульс, совпадающий во времени с Ьдним из импульсов эталонной частоты о, поступающий на вход блока 2, Импульсы от генератора 3 поступают на вход делителя 4, коэффициент деления которого равен заданному коэффи- 10 циенту К умножения. .Импульсы с выхода делителя 4, частота следования которых равна / К, поступают на вход счетчика 12.

Первым импульсом с управляющего бдока 2 переписывается полученное значение кодов из делителя 4 через элемент 8 в счетчик 9 и из первого счетчика 12 в регистр 13„

При этом, к моменту прихода перво- 20 го импульса с управляющего блока 2 на вход делителя 4 поступит N = T импульсов.

В первом счетчике 12 зафиксируется . число импульсов N, равное целой части от деления N/К, а в делителе 4 зафиксируется остаток импульсов Q.N = N -М .

Второй импульс с блока 2 через элемент 11 переписывает значение выходного кода сумматора 14, равного коду g< 30 приИЧ= О и N + 1, при ЬМ = О, в счетчик 16 и сбрасывает в ноль делитель 4 и в счетчик 12, подготавливая их к новому заполнению в следующий периодТ Выходные импульсы устройства умножения появляются каждый раз, как только счетчик 16 переходит в нулевое состояние, на вычитаюший вход которого подаются импульсы Ко от генератора 3.

Каждым выходным импульсом уст» ройства умножения выходной код сумматора 14 переписывается через элемент переноса 15 в счетчик 16, и процесс вычитания повторяется

Очевидно, что выходные импульсы будут расстановлены равномерно только при N-кратном К, т. е. при gN = О.

При hN ф О, блок 5 осуществляет

С коррекцию расстановки выходных импупьсов по времени внутри периода Тц, Коррекция производится следующим образом.

При 6N +-О, значение которого находится в счетчике 9, на выходе элемента ИЛИ 10, соединенного с младшим

$$ разрядом второго входа сумматора 14, присутствует единичный уровень. Каждый выходной импульс устройства, либо второй импульс, вырабатываемый уп!

5 88410

Блок 2 на каждый импульс синхронизатора формирует два импульса. Длительность первого импульса (. C 1 j f o.

Второй импульс образуется из первого импульса путем задержки его на время C)< (; <1(g

2 Ь равляющим блоком 2, переписывает выходной код сумматора 14, значение которого будет равно Я„ + 1, во второй счетчик 16. В этом случае появление следующего выходного импупьса устройства будет позже на время То. Кроме того, импульсы с выхода элемента 11 через элемент 7 подаются на вычитающий вход счетчика 9 и из числа дЯ вычитается единица. За время Tgg эта операция производится дЯ раз, пока счетчик 9 не установится в ноль. При этом на выходе элемента 10 устанавливается нулевой уровень, запрещающий прохождение импульсов на вычитаюший вход счетчика 9 и исключающий коррекцию кода Я, запоминающего регистра

13 при перезаписи его на второй счет чик 16.

Таким образом, расстановка по времени дй выходных импульсов осуществляется путем коррекции кода N .

Кроме того, импульс, по которому осуществляется перезапись информации о измеренном периоде входной частоты, не может совпасть с импульсом опорного генератора, так как эти сигналы синхронны и всегда имеют определенный фазовый сдвиг.

Предложенный способ расстановки К выходных импульсов умноженной частоты и привязка их к входной частоте позволяет повысить надежность работы умножителя частоты.

Максимальная абсолютная погрешность любого из К выходных импульсов приведенного устройства для умножения частоты внутри периода Т,, не превьпцает значения То и определяется только погрешностью привязки импульсов входной частоты к импульсам опорного генератора.

Формула изобретения

Устройство для умножения частоты спедования импульсов, содержащее управляющий блок, первый выход которого соединен с установочным входом делителя частоты, генератор опорной частоты, выход которого подключен к счет ному входу делителя частоты, блок умножения, состоящий из запоминающего регистра, управляющий вход которого подключен к второму выходу управляющего блока, а разрядные входы - к выходам первого счетчика импульсов, вход которого соединен с выходом делителя

884102 частоты, а установочный вход — с первым выходом управляющего блока и первым входом элемента ИЛИ, выход которого подключен к входу элемента переноса, к выходам которого подключены последовательно соединенные второй счетчик импульсов и элемент И, выход которого подключен к второму входу элемента ИЛИ, и блок коррекции, состоящий из последовательно соединенных элемента переноса, разрядные входы которого подключены к разрядным выходам делителя частоты, а управляющий вход- к второму выходу управляющего блока, счетчика импульсов и элемента ИЛИ, выход которого подключен к первому входу элемента И блока коррекции, выход которого соединен с входом счетчика импульсов этого блока, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности работы, в него введены синхронизатор и сумма8 тор, первая группа входов которого соединена с выходами запоминающего регистра блока умножения, вторая группа входов - с шиной логического нуля, вход младшего разряда — с первым входом элемента И блока коррекции, а выходыс разрядными входами элемента переноса блока умножения, вход которого соединен с вторым входом элемента И блока коррекции, при этом первый вход синхронизатора подключен к входной шине, второй вход — к выходу генератора опорной частоты и входу второго счетчика импульсов блока умножения, а выход— к управляющему блоку.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

% 337947, кл, Н 03 К 23/00, о 28.12.70.

2, Авторское свидетельство СССР

% 576658, кл. Н 03 К 5/01, 04.03.76.

ВИИИПИ Заказ 10253/83 . Тираж 991 . Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4