Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

ОП ИКАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

< >884122

Ф

/ ;г гг (61) Дополнительное к авт. свид-ay— (22) Заявлено 05.03.79 (21) 2734218/18-21 с присоединением заявки №вЂ” (51 ) М. К .

Н 03 К 13/02

Госудорстееииый комитет (23) Приоритет— (53) УДК 681.325 (088.8) Опубликовано 23.1 !.8!. Бюллетень № 43

Дата опубликования описания 28.11.81 во депем изобретений и открытий

О. Г. Сморыго и В. Я. Стени и l e(p ;; (1: !

Московский ордена Трудового Красного Знамени .

° ° р инженерно-физическии институт (72) Авторы изобретения (71) Заявитель (54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЪ

Изобретение относится к вычислительной технике.

Известен аналого-цифровой преобразователь поразрядного уравновешивания, содержащий блок сравнения, выход которого соединен со входом запоминающего ре: гистра, к п другим входам которого подсоединены п выходов .сдвигового регистра, и выходов запоминающего регистра соединены с и входами параллельного цифроаналогового преобразователя на основе резистивной матрицы R — 2R, выход которого соединен с одним. из двух входов блока сравнения, к второму входу которого подключен генератор входного сигнала !1).

Недостатком является большое количество логических элементов.

Известен аналого-цифровой преобразователь, содержащий блок сравнения, выход которого соединен со входом блока управления, выход блока управления соединен с одним из входов блока коммутации, к другому входу которого подсоединен ге-. нератор эталонных сигналов, два выхода блока коммутации соединены со входами двух блоков хранения разрядов, выходы которых подсоединены ко входам блока сравиения, генератор входного сигнала подклю .чен к одному иэ блоков хранения зарядов (2) .

Недостатком устройства является ннэ кая точность преобразования.

Цель изобретения — повышение точ-, . ности преобразования.

Указанная цель достигается тем, по в аналого-цифровой преобразователь, содержащий генератор входного сигнала, блок сравнения, блок управления, блок коммута10 ции и генератор эталонного сигнала, введены две линии задержки с п выходами каждая, две п разрядные резистивные матрицы с и входами, причем выходы блока коммутации соединены со входами соответствующих линий задержки, и выходов линий за15 держки соединены с и входами соответствующих n — разрядных резистнвных матриц так, что первый выход каждой линии задержки соединен со входом младшего разряда соответствующей п — разрядной реэистивной MBTpHUbl, выходы и разрядных реэистивных матриц соединены со входами блока сравнения, а к дополнительному входу блока коммутации подсоединей выход генератора входного сигнала.

884!22

Формула изобретения

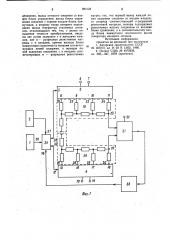

3 г1а фиг. 1 приведена структурная электрическая схема устройства; на фиг. 2— временные диаграммы работы устройства.

Устройство содержит генератор 1 эталонных сигналов, генератор 2 входного сигнала, линии 3 и 4 задержки, клеммы 5 — 18 линий задержки, выполненных на приборах с зарядовой связью, матрицы 1-9, и 20, выполненные по схеме R — 2R, клеммы 21 — 30 резистивных матриц 19 и 20, блок 31 сравнения, имеющий фазовую клемму 32, блок

33 управления, блок 34 коммутации, имеющий клеммы 35 — 39.

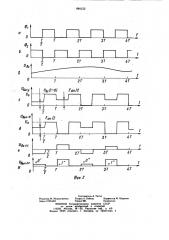

На фиг. 2 приведены временные диаграммы фазовых импульсов питания Ф и Ф

{а, б) напряжения входного сигнала (в), напряжений на первых выходах линий 3 и 4 задержки (г, д), разностного напряжения (е), подаваемого на входы блока 31, и выходного напряжения блока 31 (ж). Полярности напряжений на фиг. 2 приведены для устройства, в котором приборы с зарядовой связью с индуцированным каналом и — типа изготовлены на полупроводниковой подложке р — типа.

Аналого-цифровой преобразователь работает следующим образом.

На клеммы 6 и 13 линий 3 и 4 подается фазовое напряжение Ф (фиг. 2 а), а на клеммы 7, 14 и.32 линий 3 и 4 и блока 31— фазовое напряжение Ф (фиг. 2б). Клеммы 8 — 11 и 15 — 18 линий 3 и 4 подключены к клеммам 21 — 24 и 27 — 30 резистивных матриц 19 и 20 соответственно.

Генератор 2 подключается к выходу 37 блока 34; По состоянию логический ноль «О» на выходе блока 31 блок 33 обеспечивает ввод сигнала Е /2 от генератора 1 через блок 34, где Е4 равно максимальному значению входного сигнала U „в линию

3. Если на выходе блока 31 логическая единица «1», то сигнал Е„/2 вводится в линию 4. Выборка напряжения входного сигнала U, от генератора 2 (фиг. 2 в) вводится блоком 34 в линию 3 при t = 0 и появляется на клемме 8 (фиг. 2 г). До завершения преобразования данной выборки U „блок 34 коммутации отключает генератор 2 от линии 3. Одновременно с выборкой входного сигнала блок 34, к клемме

35 которого подключен генератор 1, формирует эталонный сигнал Е „/2 и вводит его в линию 4. Этот сигнал считывается с клеммы 15 в момент начала преобразования (фиг. 2д) t = О. В это время с остальных клемм 9 — 11 и 16 — 18 линий 3 и 4 считываются нулевые сигналы. На клемме 25 появляется сигнал U /(3 2 ), а на клемме

26 — Е,„ /(2 3 2 ). Разность сигналов (замес = U /(32 ) — Еоп/(2 3 2з) подается на входы блока 31 (фиг. 2е) t = О.

Если Uw /(3 2 )>Epp/(2 3 2 ), что аналогично U > Ep„/2, то на выходе блока

31 появляется логическая «1», в случае

Бв» /(3 2 ) + Epp (2 3 2З) — логический

«О». Сигналы с выхода блока 31 (фиг. 2ж) подаются на вход блока 33, выход которого

4 подсоединен к клемме 36 блока 34. Для диаграмм, приведенных на фиг. 2 г, д, Ug, . Е„пф (фиг. 2е, ж), и в интервале времени Π—. T/2 на выходе блока 31 вырабатывается логический «О». По результатам сравнения Ug и Е0, /2 в момент времени Т блок 34 вводит через клемму 5 опорный сигнал Е,д/2 в линию 3, а сигналы, бывшие ранее в линиях

3 и 4, перемещаются на один разряд. В момент времени t = Т с клемм 8 и 16 считываются опорные сигналы Е,„/2, с клеммы 9 — (.1вх, а с остальных клемм 10, ll, 15, 17 и 18 — нули. Разность сигналов между клеммами 25 и 26 будет равна

Uexcc = U /(3 2 ) + Eon/ (232 )—

Е,„/(232).

В соответствии с. фиг. 2е этой разности будет соответствовать уровень логической

«1» на выходе блока 31. Логическая «1» управляет блоком 34 и в момент времени

t = 2Т опорный сигнал Е,„/2 вводится в линию 4, а затем считывается с клеммы 15.

zo

В момент времени t = 2Т начинается очередной такт сравнения сигналов, которому будет соответствовать. разность сигналов между клеммами 25 и 26

1./васс = Ug)(/(3 2 ) + Ерп/(2 3 2 )— — Egg /(232 ) — Е „(2.32з)

Таким образом, в зависимости от значения сигнала на выходе блока 31 очередной опорный сигнал Е, /2 добавляется в ту линию 3 и 4, которой соответствует меньшая величина сигнала на выходе резистивной зв матрицы 19 или 20. Для диаграмм фиг. 2 выходной код аналогового сигнала будет равен 0101. В конце преобразования набор опорных сигналов, содержащийся в линии

4, соответствует выходному коду. Код самого младшего разряда с выхода блока 31

З5 можно ие вводить в линию 4, при этом время преобразования уменьшается на один тактовый период T.

Предельная точность аналого-цифрового преобразователя определяется коэффициентом эффективности переноса заряда в

40 линиях 3 и 4, выполненных на приборах с зарядовой связью, согласованностью устройств неразрушающего считывания зарядов и сопротивлений резистивных матриц, . динамическим диапазоном линий задержки и чувствительностью блоков схем сравнения.

Если в качестве устройств неразрушающего считывания зарядов и блока сравнения использовать известные схемы на биполярных транзисторах, то можно добиться того, что основное влияние на предельную

5о точность преобразования будет оказывать неидеальность коэффициента переноса сигнала в линиях задержки, величина которого меньше единицы.

Аналого-цифровой преобразователь, содержащий генератор входного сигнала, блок

884122

6 7

Фиг. 1 сравнения, выход которого соединен со вход>м блока управления, выход блока управления соединен с первым входом блока коммутации, к второму входу которого подсоединен выход генератора эталонных сигналов, отличающийся тем, что, с целью повышения точности преобразования, введены две линии задержки с и выходами каждая, две п — - разрядные резистивные мат-рицы с и входами, причем выходы блока коммутации соединены со входами соответствующих . линий задержки, и выходов линий задержки соединены с и входами соответствующих и — разрядных резистивных матриц так, что первый выход каждой ли. ннн задержки .соединен со входом младше. го разряда соответствующей и-разрядной резистивной матрицы, выходы и-разрядных резистивных матриц соединены со входами блока сравнения, а к дополнительному входу блока коммутации подсоединен выход генератора входного сигнала..

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 167373, кл. Н 03 К 13/02, 1966.

2. Патент США № 4072939, кл. 340 †3, 1978 (прототип).

884122

27

2Т

ЗТ дд

Ц) Q сс е

Цьд.cc

Мыл а

У!у

Составитель А. Титов

Редактор М. Недолуженко Техред А. Бойкас Корректор М. Шароеи

Заказ !0254/84 Тираж 99! Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений н открытий! 3035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «!1атент», г. Ужгород, ул. Проектная, 4