Преобразователь частота-код

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКЬМУ СВИДЕТЕЛЬСТВУ

Союз Сов етскнн

Соцнапнстнческнн

Респубпнн (i )884133, (6) ) Дополнительное к авт. свид-ву— (22) Заявлено 26,03,80 (21) 2898529/18 21 с присоединением заявки М (5 3 ) М. Кл.

Н 03 К 13/20

//а 01 Р 23/10 (23) Приоритет

Гооудзрстмнный комитет

СССР

Опубликовано 23. 11.81. Бюллетень М 43 по делзи изобретений н открытиЯ

{53) УДК 621.317. .76 (088,8) Дата опубликования описания 25.11.81 (72) Авторы изобретения

El. А, Ппастун и А. В. Пипипе (71) Заявитель (54) ПРЕОБРАЭОВАТЕЛЬ ЧАСТОТА — КОД

Изобретение относится к импульсной технике, в частности к спедящим цтерровым преобразователям частота - код, работающим путем сравнения периодов входного сигнала и сигнала в цепи обратной . и связи, и может найти применение в системах регулирования и контроля частоты вращения.

Известен спедящий преобразователь частота - код, содержащий реверсивный то счетчик, блок сравнения периодов и преобраэоватепь код - частота в цепи обратной связи между реверсивным счетчиком и блоком сравнения периодов (1). .15

Недостатком укаэанного преобразователя является недостаточная точность.

Наиболее близким к изобретению по технической сущности является спедящий преобразователь частота - код, содержащий генератор опорной частоты, реверсивный счетчик, преобраэоватепь код - частота со схемой ткоррекпии, соединенный

f с генератором опорной частоты и кодовым выходом реверсивного счетчика, и блок сравнения периодов, соединенный входами с входной шиной устройства и выходом преобразоватепя код - частота, а выходами .- с суммирующим и вычитаюшим входа» ми реверсивного счетчика j2).

Недостатком устройства является недостаточная точность, что вызвано совпадением моментов заполнения реверсивного счетчика импульсами коррекции периода и формирования частоты на преобразователе код-частота, соединенного непосредственно с выходами реверсивного счетчика.

Бель изобретения - повышение точности измерений.

Бель достигается тем, что в преобразоватепь частота - код, содержащий генератор опорной частоты, блок сравнения периодов, первый и второй выходы которого соединены с суммирующим и вычитаюшим входами реверсивного счетчика соот884133 4 вателя 4 кода в частоту, а выходамис шинами сложения и вычитания счетчика 2, элемент 11 И-НЕ.

Работа устройства заключается в следующем.

Входная импульсная последовательность полупериодных импульсов частоты которую необходимо преобразовать в код, поступает на первые входы элемента 11 и триггера 7 блока 5 сравнения периодов. На второй вход элемента 11 и триггера 8 поступают полупериодные импульсы Г с с преобразователя 4, Укаэанные импульсные последовательности с частотами F g и Г ос представлены на фиг. 2 б, в. На фиг. 2, r представлены импульсы, сформированные на выходе элемента 11. По переднему и заднему фронтам этих импульсов формирователем 6 формируется пара коротких импульсов (фиг. 2 д, е). Импульсы, сформированные по переднему фронту на втором выходе формирователя устанавливают триггеры 7 и 8 в исходное состояние, а сформированные по заднему фронту — производят перепись кода со счетчика 2 в регисгр 3.

Состояния триггеров 7 и 8 показаны на фиг. 2 ж, з. Исходные положения триг;геров заштрихованы. Переключение триггеров 7 и 8 производится задними фронтами импульсов соответствующих последовательностей F Х и Foz .

На входах элементов 9 и 10, таким образом, присутствуют сигналы с выхода элемента 11, входных сигналов Fo u :,>с и сигналы с выходов триггеров 7 и 8, В зависимости от соотношения частот

Ех и Сос на входах счетчика 2 происходит периодическое суммирование и вычитание импульсов представленных на фиг. 2 и, к.

При равенстве входных частот F х и о, соответствующих установлению кода частоты, количество импульсов на- . копленных по шинам суммирования и вычитания счетчика 2 равны между собой..

Код, зафиксированный в конце суммирования регистром памяти 3l записан вторыми импульсами (фиг. 2д, е) со счетчика 2 (фиг. 2л).

$$ ветственно, преобразователь кода в часгогу, выход которого совпадает с первым входом блока сравнения периодов, второй вход которого подключен к входной шине устройства, введен регистр памяти, кодо - $ вые входы которого соединены с выходами разрядов реверсивного счетчика, вход записи регистра памяти подключен к третьему выходу блока сравнения периодов, первый и второй выходы которого соединены со счетным входом реверсивного счетчика и входом преобразователя кода в частоту, кодовые входы которого соединены с выходами разрядов регистра памяти и выходными шинами устройства, а кроме того, блок !$ сравнения периодов содержит формирователь импульсов, элемент И-НЕ, два триггера и два элемента И, причем первым входом блока сравнения rIepHolloB является первый вход элемента И-НЕ, соединенный с первыми входами первого триггера и первого элемента И, выход которого является вторым выходом блока сравнения периодов, вторым входом которого является второй вход элемента И25

НЕ, соединенный с первыми входами второго триггера и второго элемента И, выход которого подключен к первому выходу блока сравнения периодов, выход элемента И-HE соединен со вторыми входами элементов И и со входом формирователя импульсов, первый выход которого является третьим выходом блока сравнения периодов, а второй выход подключен к вторым входам триггеров, выход каждого из которых подключен к третьему входу соответствующего элемента H.

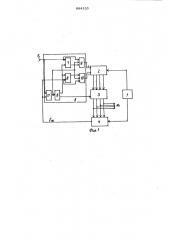

На фиг, 1 представлена блок-схема 40 преобразователя; на фиг. 2 — временные диаграммы работы устройства.

Устройство содержит генератор 1 опор- ной частоты, реверсивный счетчик 2, сое- 4$ диненный счетным входом с выходом генератора, регистр 3 памяти, соединенный кодовыми входами с выходами разрядов счетчика 2, преобразователь 4 кода в

$0 частоту, соединенный с регистром 3 и выходными шинами устройства, а импульсным входом - с генератором, блок

1 бл 5 сравнения периодов, включающий в себя формирователь 6 импульсов, R 5-триггеры 7 и 8 и трехвходовые элементы 8 и

1О И, соединенные входами с входной шиной устройства и выходом преобразоПри равенстве частот код на выходе регистра памяти 3 изменяться не будет.

Нарушение равенства входных частот и Ррс вызывает неравенство чисВЕ4133 ла импульсов накапливаемых за период входной частоты на входах счетчика 2 (фиг. 2л). При этом изменяется результируюший код на выходе регистра 3 (фиг. 2г). Код, неизменный в течение периода входного сигнала, с выхода регистра 3 поступает на преобразователь

4 кода в частоту в цепи обратной связи и на выход устройства., Таким образом, буфферное включение регистра памяти между реверсивным счетчиком и преобразователем код частота с управлением его записи с блока сравнения периодов в моменты отсутствия накопления импульсов на реверсивном счетчике .повышает точность формирования кода - частоты, такое выполнение блока сравнения позволяет устранить несимметричность характеристик устрой20 ства при разном соотношении частот (р ГХ Г и Fx. F ). Это позволяет повысить частоту формирования сигналов коррекции блоком сравнения перио25 дов при превышении частоты входного сигнала F по сравнению с частотой цепи обратной связи Foes eeM самым повысить динамическую точность устройства.

Формула изобретения

l. Преобразователь частота- код, содержащий генератор опорной частоты, блок 55 .сравнения периодов, первый и второй выходы которого соединены с суммирутощим и вычитающим входами реверсивного счетчика соответственно, преобразователь кода в частоту, выход которого соединен 40 с первым входом блока сравнения периодов, второй вход которого подключен к входной шине устройства, о г л и ч а юш и и с я . тем, что, с целью повышения точности измерений в него введен регистр памяти, кодовые входы которого соединены с выходами разрядов реверсивного счетчика, вход записи регистра памяти подключен к третьему выходу блока сравнения периодов, первый и второй выходы которого соединены со счетным входом реверсивного счетчика и входом преобразователя кода в частоту, кодовые входы которого соединены с выходами разрядов регистра памяти и выходными шинами устройства, 2, Преобразователь частота - код по и. l, отличающийся тем, что блок сравнения периодов содержит формирователь импульсов, элемент И-НЕ, два триггера н два элемента И, причем первым входом бпока сравнения периодов является первый вход элемента И-НЕ, соединенный с первыми входами первого триггера и первого элемента И, выход которого является вторым выходом блока сравнения периодов, вторым входом которого является второй вход элемента И-НЕ, соединенный с первыми входами второго триггера и второго элемента И, выход которого подключен к первому выходу блока сравнения периодов, выход элемента И-НЕ соединен со вторыми входами элементов И и со входом формирователя импульсов, первый выход которого является третьим выходом блока сравнения периодов, а второй выход подключен к вторым входам триггеров, выход каждого из которых подключен к третьему входу соответствующего элемента И.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

% 443482, кл. Н 03 К 13/20, 1974.

2. Авторское свидетельство СССР

Ng 445148, кл. Н 03 К l3/20, 1972 (проготиц).