Широтно-импульсное множительное устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДВТИЛЬСТВУ

Союз Соввтскик

Соцмалистмчесимк

Республик (п>886009 (61) Дополнительмое к авт. сеид-ву— (22)Заявлено 18.02. 80 (21) 2883534/18-24 с присоединением заявки М—

{23) Приоритет— (5 В ) М. Кл.

G Об G 7/161

10еударстщкаыв кемвтет

CCCP ао двлан «звбрвтвнвй и втюритк1

Опубликовано 30 ° 11.81, бюллетень М 44 (53) УЙ К 681 . 335 (088. 8) Дата опубликования опмсання 30.11.81 (72) Авторы изобретения

А.С Давыдов, В.У.Кизилов и И.И.См

Харьковский ордена Ленина полите им.В .И.Ленина ф щщр тф4 ": (71) Заявитель ь."ВЛИОТЕМ% (54) ПИРОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНОЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике и может быть использовано как блок перемножения, Известны широтно-импульсные множительные устройства, в которых результат перемножения представляется в виде разности длительностей импульсов (11.

Основной недостаток указанных устройств состоит в их сложности.

Наиболее близким rio технической

10 сущности к предлагаемому является широтно-импульсное множительное устройство, которое содержит широтноимпульсный модулятор, состоящий из

И последовательно соединенных интегратора, ко входу которого подключен источник входного сигнала, и компаратора, ко входу которого подключен другой источник входного сигнала, второй компаратор, подключенный к выходу интегратора, и два ключа, управляемые выходным сигналом первого компаратора 2 g.

Недостатком известного устройства является невысокая точность перемножения. Погрешности в результатах перемножения сигналов в основном оп-. ределяются тем, что переключение второго компаратора происходит не при переходе напряжения на выходе интегратора через ноль, так как реальные транзисторные ключи имеют остаточное напряжение.

Цель изобретения — повышение точности перемножения входных сигналов.

Поставленная цель достигается тем, что в широтно-импульсное множительное устройство, содержащее последовательно соединенные интегратор и первый компаратор, выход которого подключен ко входу интегратора, вход интегратора является входом первого сомножителя устройства, первый вход первого компаратора является входом второго сомножителя устройства, а второй вход подключен к шине нулевого потенциала, и второй компаратор, 88

20 причем выход интегратора подключен к первому входу второго компаратора, введен элемент неравнозначности,входы которого подключены к выходам первого и второго компараторов, выход элемента неравнозначности является выходом устройства, второй вход второго компаратора подключен к шине нулевого потенциала.

Злемент неравнозначности (или равнозначности) формирует на выходе четыре разнополярных примыкающих импульса, относительная разность длительностей которых пропорциональна произведению входных сигналов, что исключает из схемы основной источник погрешностей — транзисторные ключи.

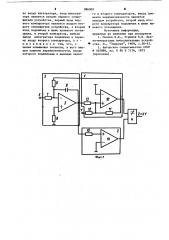

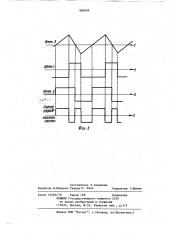

На фиг.1 приведена принципиальная схема широтно-импульсного множительного устройства, на фиг.2 — временные диаграммы его работы.

Широтно-импульсное множительное устройство содержит компараторы и 2, интегратор 3 и элемент 4 неравнозначности

Интегратор 3 содержит операционный усилитель 5, резисторы 6, 7 и 8 и конденсатор 9, первый компаратор содержит операционный усилитель 10 и резисторы 11, 12 и 13, второй компаратор содержит операционный усилитель

14 и, резистор 15.

Множительное устройство работает следующим образом.

При отсутствии входных сигналов интегратор 3 и компаратор 1 работают в автоколебательном режиме как релаксационвый генератор. На выходе интегратора 3 формируется симметричное пилообразное напряжение, а на выходе коипаратора - напряжение прямоугольной формы. Компаратор 2 переключает ая при переходе через ноль напряжения на выходе интегратора 3, Hà его выходе также формируется напряжение прямоугольной формы. Разнополярные импульсы с выходов комнараторов 1 и

2 подаются на входы элемента 4 неравнозначности, на выходе которой эа период образуются две пары чередующихся разнополярных импульсов.

При отсутствии входных сигналов относительная разность длительностей импульсов на выходе элемента 4 Нрравнозначности равна нулю. Если на вход интегратора и компаратора поданы входные сигналы Х и У, то скорость ,изменения напряжения на выходе интег6009

4 ратора равна - (U+x) при положительT ном и —" (U-х) при отрицательном напряг жениях на выходе компаратора 1, пороги срабатывания компаратора 1 равны соответственно (00+У) H (Ug -У), 4U — напряжение на выходе компаратора

1, . U 0 — порог срабатывания компаратора 1, Т - постоянная времени интегратора 3.

При наличии входных сигнапов на выходе элемента 4 неравноэначности за период Т интегратора 3 образуются четыре прямоугольных импульса различной длительности. Длительности этих импульсов равны тi T «a IL

U+X "- U+X

Т -т -- —; .=т

И-Х u-X

Определим относительную длительность положительных Т и и от3 ,рицательных и импульсов за период генерируемого напряжения р .гд.х я + +

1 Ъ 4

Т 2UoU+2XY - Т 2UyU 2ХУ и х 6 :7г хх

Зо T — - - ООО

Таким образом, относительная длительность разнополярных импульсов на выходе элемента 4 неравнозначности

35 оказывается пропорциональной произведению входных сигналов.

Так как погрешности прототипа в известном устройстве определяются тем, что переключения второго компа40 ратора происходят при некотором уровне напряжения, обусловленном остаточным напряжением реальных транзисторных ключей, а также прохождением сигнала с выхода первого компаратора через управляющие входы ключей на входы второго компаратора, то исключение из схемы ключей и получение результатов перемножения на выходе элемента неравнозначности повышает точность, 5о перемножения входных сигналов.

Формула изобретения

55 Широтно-импульсное множительное устройство, содержащее последовательно соединенные интегратор и первый компаратор, выход которого подключен1

% 886009 4 ко входу интегратора, вход интегра" го и второго компараторов, выход элетора является входом первого сомно- мента неравнозначности является жителя устройства, первый вход пер- выходом устройства, второй вход втового компаратора является входом вто- .рого компаратора подключен к шине нурого сомножителя устройства, а второй S левого потенциала. вход подключен к шине нулевого потен- Источники информации, циала, и второй компаратор, причем принятые во внимание при экспертиэе . выход интегратора подключен к перво- 1 . Смолов В .Б ., Угрюмов Е .П. Врему входу второго компаратора, о т — мя-импульсные вычислительные устрой- . л и ч а ю щ е е с я тем, что, с ® ства. Л., "Энергия", 1968, с.36-43. целью повышения точности, в него вве- 2. Авторское свидетельство СССР ден элемент неравноэначности, входы В 492886, кл. G 06 G 7/16, 1973 которого подключены к выходам перво- (прототип) .

886009

Фиг. г

Составитель Т.Сапунова

Редактор И.Михеева Техред М. Надь Корректор C.IIIîìàê

Заказ I0560/78 Тираж 748 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий !

)3035, Москва, Ж-35, Раушская наб., д.4/5

Я филиал ППП "Патент", r.Óæãîðoä, ул.Проектная,4