Аналоговый интегратор

Иллюстрации

Показать всеРеферат

- Союз Советсиив

Соцнаннатнчеси ив рес убяии

О П И С А Н И Е ц886010

ИЗОВРЕТЕН ИЯ

К А®ТОРС НОМУ СВИДВТНЗЬСТВУ (б1) Дополнительное к авт. сана-ву (22)Заявлено 06.02.80(2l) 2880802/18-24 (5(2 К>. с прнсоелннениее заявки М—

G 06 G 7/186

Гееуааретеанвй кенвтет

ССьр вв аелаи .взеврвтейвЯ в еткрмтвй (23) Приоритет

Опубликовано 30.11.81. Бюллетень М 44 ° (53} УДК 681.335 (088.8) Дата опубликования описания 30.11. 81 (72) Автор.Иороэов (54 ) АНАЛОГОВЫЙ ИНТЕГРАТОР

1 1

Изобретение относцтся к анапого- вым измерительным и вычислительным устройствам, а именно к решакицим блокам таких устройств — аналоговым интеграторам.

Известен аналоговыи интегратор, 3

Э состоящий из входного резистора, конденсатора обратной связи и операционного усилителя (11.

Известный интегратор характеризует10 ся увеличением ошибки интегрирования при недостаточном коэффициенте усиления.операционного усилителя, например, при повышенной частоте входного сигнала.

Наиболее близким по технической сущности к предлагаемому является интегратор, содержащий интегрирующий усилитель, усилитель напряженйя ошибки и дополнительный масштабный усилитель $2).

Однако существенный недостаток указанного интегратора состоит в необходимости применения дополнительного масштабного усилителя с двумя пре-цизионными входными резисторами. Относительная погрешность этих резисторов заметно ухудшает компенсацию ошибки интегрирования .

Цель изобретения — повышение точности интегрирования и упрощение аналогового интегратора за счет устранения дополнительного масштабного усилителя тт вычитания соответствующим образом сформированного сигнала ошибки непосредственно на входе интегратора.

Укаэанная цель достигается тем, что в аналоговом интеграторе, содержащем операционный усилитель, вход которого соединен с неинвертирующим входом усилителя напряжения ошибки, через первый масштабный резистор - со входом аналогового интегратора и через интегрирующий конденсатор — с выходом операционного усилителя, являющимся выходом аналогового интегратора, масштабные

886010 лителя 4, дает на выходе интегратора составляющую напряжения, равную

ЬО рТ (- IpT), т.е. -дО. Но в общем выходном сигнале Уз 4.д U составляющие ошибки д0 и -4U компенсируются. Сущестненйо, что отклонения параметров, резисторов 5, 6 и 7 и конденсатора 8 вызывает ошибку от ошибки, т.е. погрешность второго по10 рядка малости. Поэтому точность компенсации в реальных устройствах получается высокой.

Технический эффект от внедрения предлагаемого устройства определяет15 ся экономией за счет исключЕния одного операционного усилителя и двух прецизионных резисторов, что составляет 25Х стоимости элементов в известном устройстве. Для операционнощ го усилителя типа 140УД12 и резисторов типа С2-29 с допуском + 0,1Х это составляет около 3000 руб. годовой экономии при выпуске 12 аналоговых устройств с 50 интеграторами каждое.

Формула изобретения

Усилитель напряжения резисторы и накопительный конденсатор, неинвертирующий вход усилителя напряжения ошибки через второй масштабный резистор подключен к его выходу, соединенному через третий масштабный резистор с инвертирующим входом, подключенным через параллельно включенные четвертый масштабный резистор и накопительный конденсатор обратной связи к шине нулевого потенциала.

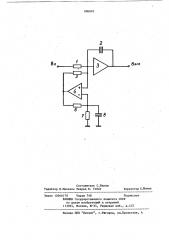

Схема аналогового интегратора показана на чертеже.

Аналоговый интегратор содержит масштабный резистор I, интегрирующий конденсатор 2 и операционный усили1тель 3, к суммирующему входу которого подключен неинвертирующий вход усилителя 4 напряжения ошибки, выход которого соединен с его инвертиоуюшим и неинвертирующим .входами через масштабные резисторы 5 и 6 соответственно.

Инвертирующий вход усилителя 4 соединен также с.шиной нулевого потенциала через параллельно соединенные масштабный резистор 7 и накопительный конденсатор 8. Сопротивление резисторов 5 и 6 равно сопротивлению резистора l. .Емкость конденсатора 8 равна емкости конденсатора 2.

Интегратор работает следующим образом.

На выходе операционного усилителя

3 в процессе работы имеется напряжение, равное сумме точного значения интеграла от входного сигнала и напряжения ошибки, т.е. 0> + д U . В суммирующей точке точное значение интеграла компенсируется входным сигналом, а остается лишь напряжение ошибки, поделенное на коэффициент передачи цепи обратной связи — кон-. денсатора 2 и параллельно соединенных резисторов 1 и 5, т .е. напряжение в суммирующей точке равно Д0

"1Р " 1 45

Р ошибки по неинвертирующему входу имеет усиление 1/Kz где К0с - коэффициент передачи цепи обратной связирезистора 6 и параллельно соединенных резистора 7 и конденсатора 8, равный (рТ+2) .

Таким образом, напряжение ошибки на выходе усилителя 4 равно Ь 0 рТ .

Поскольку коэффициент передачи интегратора по входу, образованному резистором 5, равен — 1/рТ, напряжение ошибки, поступающее с выхода усиАналоговый интегратор, содержащий операционный усилитель, вход которого соединен с неинвертирующим входом усилителя напряжения ошибки, через первый масштабный резистор— со входом аналогового интегратора и через интегрирующий .конденсатор— с выходом: операционного усилителя, являмцимся выходом аналогового-интегратора, масштабные резисторы и накопительный конденсатор, о т л и— ч а ю шийся тем, что, с целью повышения точности интегрирования и упрощения аналогового интегратора, неинвертирующий вход усилителя напряжения ошибки через второй масштабный резистор подключен к его выходу, соединенному через третий масштабный резистор с инвертирующнм входом, подключенным через параллельно включенные четвертый масштабный резистор и накопительный конденсатор к шине нулевого потенциала.

Источники информации, принятые во внимание при экспертизе

1 . Коган Б.Я. Электронные модели" рующие устройства и их применение для исследования систем автоматического регулйрования. М., Фиэматгиз, 1963.

2. Авторское свидетельство СССР по заявке Ф 281 5882/24,кл . G 06 G 7/1 8

1979 (прототип), 886010

Вьсх

Составитель С,Белан

Редактор И.Михеева Техред И. Гайду

Корректор СЛомак

Филиал ППП "Патент", r.ужгород, ул.Проектная, 4

Заказ 10560/78 Тираж 748 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5