Многоканальное устройство синхронизации и выравнивания потоков информации

Иллюстрации

Показать всеРеферат

(72) Авторы изобретения

И.В.Мареев и Д.В.Иоисеев (7)) Заявитель (54) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО СИНХРОНИЗАЦИИ

И ВЫРАВНИВАНИЯ ПОТОКОВ ИНФОРМАЦИИ

Изобретение относится к передаче .и обработке информации в многоканальных цифровых системах с цикловой синхронизацией, в которых синхросигнал передается в ниде последовательности чередующихся маркерных синхрогрупп двух видов, когда длина цикла во всех каналах одинакова, однако маркеры различных каналов смещены во времени относительно друг друга, т.е. преимущественно в.многоканальных сис-1 темах связи, системах телеиэмерения, а также в многоканальных цифровых магнитофонах, работающих с высокой плотностью записи, когда имеет место взаимный перекос каналов движу1% щегося носителя записи.

Известно многоканальное устройство синхронизации и выравнивания потоков информации, содержащее триггер, а

20 в каждом из каналов генератор управления записью и буферный накопитель, тактовые и информационные входы которых объединены соответственно (! ).

Недостатком известного устройства является низкая точность синхронизации.

Цель изобретения †.повышение точности синхронизации.

Для достижения указанной цели в, многоканальное устройство синхронизации и выравнивания потоков информации, содержащее триггер, а в каждом иэ каналов генератор управления записью и буферный накопитель, тактовые информационные входы которых объединены соответственно, введены управляемый компаратор, последовательно соединенные дискриминатор и генератор управления считыванием, а в каждый канал введены элемент ИЛИ и элемент

И, при этом управляющий и считывающий выходы генератора управления считыванием подключены к соответствующим входам буферного накопителя каждого канала, к фазирующему входу которого подключен через элемент И соответствующий выход генератора управления

886018 записью данного канала и один из входов элемента ИЛИ, другой вход которого подключен к выходу "Запись" генератора управления записью соответствующего канала, а выход элемента ИЛИ подключен ко входу "Запись" соответствующего буферного накопителя, кроме того, выход "Запись" генератора управления записью каждого канала подключен к соответствующему входу управляемого компаратора, выход которого подключен к счетному входу триггера, выход которого подсоединен ко входу дискриминатора и к другому входу элемента И каждого канала.

Кроме того, буферный накопитель каждого канала содержит входной коммутатор, выходы которого через элементы памяти подключены к соответствующим входам элемента

ИЛИ, причем входы входного коммутатора являются соответственно тактовым, фазирующим входом Запись" и управляющим входами буферного накопителя, объединенный вход элементов памятиинформационным входом буферного накопителя, а выход элемента ИЛИ вЂ” выходом буферного накопителя.

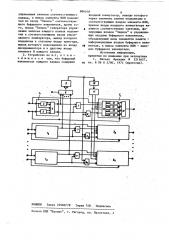

На чертеже приведена структурная электрическая схема предлагаемого устройства.

Многоканальное устройство синхронизации и выравнивания потоков информации содержит генераторы управления записью, каждый из которых состоит из дешифратора 2> счетчика

3 длины цикла и блока 4 вхождения в синхроцизм, буферные накопители 5, элементы И 6, элементы ИЛИ 7, унравляемый компаратор 8, триггер 9, дискриьынатор 10 и генератор 11 управления считыванием, кроме того, буферный накопитель содержит входной коммутатор 12, элементы 13 памяти и элемент ИЛИ 14.

Устройство работает следуюирам об" разом.

Генератор 1 управления записью в каждом канале устройства генерирует на первом выходе, соединенном со входом компаратора 8 и элементом ИЛИ

7, регулярную последовательность маркерных импульсов Ml, соответствующих по временному положению синхрогруп,пам первого вида, а на втором выходе, соединенном со вторыми входами элементов ИЛИ 7 и И 6 — последователь.,ность М2, соответствующую синхрогруппам второго вида. Для этого ннформа4 ционный сигнал со входа устройства поступает на дешифратор 2, а тактовые импульсы поступают на счетчйк 3 длины цикла. Отклики на синхрогруппы первого и второго видов с выхода дешифратора 2 поступают на вход блока 4; который в результате их анализа устанавливает необходимую фазу счетчика 3 длины цикла, с помощью выto ходного сигнала которого в блоке 4 формируются последовательности маркеров Мl и М2.

Маркеры М! всех каналов поступают на входы компаратора 8. Компаратор

8 выполняется таким образом, что импульс на его выходе появляется, о когда на его вход поступает некоторое наперед заданное число любых первых пришедших маркерных импульсов Ml

Удобно это чиспо выбирать равным половине общего числа каналов устройства. Такой выбор позволяет сохранить работоспособность устройства в целом даже при выходе as строя некоторого числа канапов (до половины) или потере синхрониэма в них.

Таким образом, комнаратор 8 гене-. рирует выходной импульс, когда на его входы поступает и /2 первых по времени маркеров М1 с выхода генераторов 1 управления записью любых tt/2 из и каналов.

Последовательность импульсов с выхода компаратора 8 поступает на счетный вход триггера 9, на выходе которого образуется несимметричный и непостоянный rro периоду в общем случае меандр. Несимметричность вызывается смещением маркеров от цикла к циклу, а изменения периода вызываются (например, в случае магнитной. записи) вариациями скорости носителя записи. Несимметричность и непостоянство периода выходного сигнала триггера 9 являются упранпяющими воздействиями для дискриминатора 10, кото-. рый преобразует их в сигнал управления частотой генератора Il управления считыванием, на оДном выходе

50 которого формируется тактовая частотаа считывания, а на другом — управляющий сигнал начала считывания.

Положительный полупериод выходного сигнала триггера 9 подается на входы элементов И 6 всех каналов уст55 ройства и является стробом фазирования для коммутаторов 12 буферных накопителей 5. Фазирование буферного накопителя 5 осуществляется индивиду88601

Формула изобретения

° 5

59

55 ально для каждого канала маркером М, который со второго выхода генератора

1 управления записью проходит через открытый стробом триггера 9 элемент

И 6, но буферные накопители 5 всех каналов фазируются маркерами М2, принадлежащими одному и тому же циклу во всех каналах устройства, причем фазировка подтверждается через каждые четыре цикла. После того как осуществлено фазирование накопителей 5, коммутатор 12 под воздействием цикловых синхроимпульсов М-М1УМ2 с выхода элементов ИЛИ 7 начинает формировать сигналы разрешения записи информации в элементы 13 памяти (ЗП) . 3a0 пись начинается цикловым синхроимпульсом М, совпадающим с фазирующнм маркером М2, в первый ЭП 13, следующим по времени маркером М, совпадающим с Ml формируется. строб записи во второй ЗП 13 и т.д. Тактовые импульсы записи поступают в накопители 5 со входа устройства, а информа" ция на входы ЭП ) 3 — с другого входа устройства. После того, как строб записи для одного из четырех ЭП 13 сформирован, адресный счетчик записи коммутатора 12 начинает заполнение выбранного ЭП 13 поступающей информацией.

Стробы разре1иения считывания формируются коммутаторами 12 одновременно во всех каналах под воздействием управляющих сигналов считывания с выхода генератора 11 управления считыванием, причем считывание осуществляется нз каждого ЗП 13 ео сдвигом примерно на два цикла относительно записи в него, т.е. если в текущем цикле запись идет в первый

ЭП 13, то считывание происходит из третьего ЭП 13, при записи во второй

ЭП )3 считывание осуществляется из четвертого ЭП 13 и т.д.

Такой алгоритм работы коммутатора

12 позволяет полностью исключить потери информации при относительном смещении маркеров в каналах устройства на цикл.

Одновременное считывание информации из накопителей 5 всех каналов осуществляет ее выравнивание. Тактовые импульсы считывания в накопителе

5 поступают с выхода генератора 11, управления считыванием. Информация из ЭП 13 через элементы ИЛИ 14 поступает на выходы устройства.

Предлагаемое устройство обладает более широкими функциональными возможностями по сравнению с известным, так как оно позволяет выравнивать потоки информации, сдвинутые друг относительно друга на интервалы длительностью до цикяа синхронизации. В результате построения генератора l управления записью в виде схемы, генерирующей две последовательности маркеров, возможно устранение сбоев фазировки даже в том случае, когда величина сдвига превышает в части какапов длительность цикла, а применение четырех элементов 13 памяти в буферном накопителе 5 позволяет из-. " бежать в этом случае потерь информации.

Устройство универсально, так как оно может применяться как для устранения перекосов движущегося носителя в системах магнитной записи, так и в несинхронизированных системах передачи информации, обладает сущестф5 венно более высокой помехоустойчивостью по сравнению с известным, поскольку возможность изменения порога срабатывания компаратора позволяет надежно осуществлять выравнивание потоков

5 информации даже прн выходе из строя части каналов системы передачи инфоп-! мации .

Многоканальное устройство синхронизации и выравнивания потоков информации, содержащее триггер, а в каждом из каналов генератор управле" ния записью и буферный накопитель, тактовые и информационные входы которых объединены соответственно, отличающееся тем, что, с целью повышения точности синхронизации, в него введены управляемый компаратор, последовательно соединенные дискриминатор и генератор управления считыванием, а в каждый канал введены. элемент ИЛИ и элемент И, при этом управляющий и считывающий выходы генератора управления считыванием подключены к соответствующим входам буферного накопителя каждого канала, к фазирующему входу которого подключен через элемент И соответствующий выход генератора управления записью данного канала и один из входов элемента ИЛИ, другой вход которого подключен к выходу "Запись" генератора

ВНИИПИ Заказ 10560/78 Тираж 748 . Подписное

Фи.чиал ППП "Патент", r. Ужгород, ул. Проектная, 4 управления записью соответствующего канала, а выход элемента ИЛИ подключен ко входу "Запись" соответствующего буферного накопителя, кроме того выход "Запись" генератора управления записью каждого канала подключен к соответствующему входу управляемого компаратора, выход которого подключен к счетному входу триггера, выход которого подсоединен ко входу дискриминатора и к другому входу элемента И каждого канала.

2. Устройство по п.1, о т л и— ч а ю щ е е с я тем, что буферный накопитель каждого канала содержит

886018 8 входной коммутатор, выходы которого через элементы памяти подключены к соответствующим входам элемента ИЛИ, причем входы входного коммутатора являются соответственно тактовым, фазирующим входом Запись" и управпяющим входами буферного накопителя, объединенный вход элементов памятиинформационным входом буферного нако-! ° пителя, а выход элемента ИЛИ вЂ” выходом буферного накопителя.

Источники информации, принятые во внимание при экспертизе

1 . Патент Франции 9 221 5657, 1у кл. G 06 К. 5/00, 1974 (прототип) .