Полупроводниковое постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социапнстических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 08. 02. 78 (21) 2578531/18-24 с присоединением заявки ¹вЂ” (23) Приоритет

Опубликовано 30 ° 11. 81. Бюллетень ¹ 44

Дата опубликования описания 01. 12.81

G 11 С!7/00 тощлорстесниый комитет

СССР (53) УДK 681.327..6(088.8 ) оо лелем изобретений . и открытий

Ы-:.; Д ;:";--,.-з

И. Я. Козырь и О. А. Петро яф 1 -" Е!!ТИО-! " "1 ::- - Е1ГГ.Ьщ тт

1, 1 Ц

Московский институт электронной техники (72) Авторы изобретения (7l ) Заявитель (54 1 ПОЛУПРОВОДНИКОВОЕ ПОСТОЯННОЕ ЗАПОИИНА1ОПЕЕ

УСТРОЙСТВО

Изобретение относится к вычислительной технике, в частности к микро1 электронным запоминающим устройствам, и может быть использовано в устройствах обработки цифровой информации в качестве подпрограмм, табличных данных, генераторов символов, преобразователей кодов и др.

Известно полупроводниковое постоянное запоминающее устройство, содержащее накопитель с элементами связи

10 на биполярных транзисторах (11 °

Наиболее близким к предлагаемому по технической сущности является полупроводниковое постоянное устрой15 . ство, содержащее накопитель с элементами связи на многоэмиттерных транзисторах, дешифратор, выполненный на многоэмиттерных транзисторах, адресные формирователи, инвертор разрешения выборки и источник питания (2).

Недостатками этих устройств являются необходимость применения преобразователей уровней по входу и выходу для согласования их уровней с аналогичными уровнями эмиттерно-связанной логики (ЭСЛ) и усилителей считывания, что приводит к уменьшению быстродействия.

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, что в полупроводниковое постоянное запоминающее устройство, содержащее дешифратор и накопитель, выполненные на многоэмиттерных транзисторах, адресные формирователи, выходы которых соединены с соответствующими эмиттерами многоэмиттерных транзисторов ,дешифратора, базы которых соединены с соответствующими базами многоэмиттерных транзисторов накопителя и одним концом соответствующих нагрузочных элементов, выполненных на резисторах, другие концы которых подключены к шине нулевого потенциала и к коллекторам многоэмиттерных транзисторов накопителя, инвертор разрешения выборки, каждый выход которогс. соединен с соответствующим эмиттером многоэмиттерных транзисторов дешифратора, и источник питания, введены блоки сопряжения, выполненные на резисторах, при этом одни концы резистора лодключенй к.выходу источника питания, а другие концы резисторов первого блока сопряжения к соответствующим эмиттерам многоэмиттерных транзисторов дешифратора, другие концы резисторов второго блока сопряжения подключены к соответствующему эмиттеру каждого многоэмиттерного транзистора дешифратора, а другие концы резисторов третьего блока сопряжения подключены к соответствующим эмиттерам многоэмиттерных транзисторов накопителя.

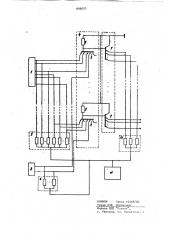

На чертеже преДставлена электрическая схема устройства.

Устройство содержит адресные формирователи 1 и инвертор 2 разрешения выборки, выходы которых соединены с соответствующюли эмиттерами многоэмиттерных транзисторов 3 дешифратора 4, при этом выходы адресных формирователей 1 соединены с соответствующими концами резисторов первого бло ,ка 5 сопряжения, а выходы инвертора

2 разрешения выборки соединены с со-ответствующими концами резистор6в второго блока 6 сопряжения. Базы

Ф многоэмиттерных транзисторов 3 дешифратора 4 соединены с соответствующими базами многоэмиттерных транзисторов 7 накопителя 8 и одним концом соответствующих нагрузочных элементов 9, выполненных на резисторах, другие концы которых подключены к шине нулевого потенциала и к коллекторам многоэмиттерных транзисторов 7 накопителя 8. Одноименные эмиттеры многоэмиттерных транзисторов 7 накопителя 8 объединены с сответствующими концами резисторов третьего блока

10 сопряжения и имеют внешние выводы. Одни концы резисторов блоков

5,6 и 10 сопряжения подключены к вы" ходу источника 11 питания.

В предлагаемом устройстве дешифратор 4 построен на многоэмиттерных транзисторах 3, где цепь коллектора разомкнута (коллектор многоэмиттерных транзисторов 3 можно закоротить с базой, что приведет к уменьшению времени рассасывания носителей, т.е. к повышению быстродействия), накопитель построен также на многоэм1п6053

40

Формула изобретения

4 терных транзисторах 7 и работает в ненасыщенном режиме, что приводит к повышению быстродействия.

Полупроводниковое постоянное запоминающее устройство работает следующим образом.

Адресные формирователи 1 вырабатывают высокие и низкие уровни напря.жения,которые подаются на соответствующие эмиттеры многоэмиттерных трансформаторов 3 дешифратора 4.При этом . переходы многоэмиттерного транзисто, ра 3 дешифратора 4,на все эмиттеры которого поступают высокие уровни из соответствующих выходов адресных

-формирователей 1 и инвертора 2 разрешения выборки запираются. В результате выбирается одноименный многоэмиттерный транзистор 7 накопителя

8, из которого считывается соответствующее слово. Значения высоких и низких уровней на выходах адресных формирователей 1, инвертора 2 разрешения выборки и накопителя 8 достигается с помощью блоков 5, 6 и 10 сопряжения соответственно. Аналогичным образом осуществляется считывание информации из других многоэмиттерных транзисторов 7 накопителя 8 при соответствующем выборе многоэмиттерного транзистора 3 дешифратора 4, на эмиттеры которого поступают высокие уровни напряжения из адресных формирователей 1 и инвертора 2 разрешения выборки.

Таким образом, предлагаемое устройство отличается от известных повышенным быстродействием, которое достигается введением блоков сопряжения.

Полупроводниковое постоянное запоминающее устройство, содержащее дешифратор и накопитель, выполненные на многоэмиттерных транзисторах, адресные формирователи, выходы которых соединены с соответствующими эмиттерами многоэмиттерных транзисторов дешифратора, база которых соединена с соответствующими базами многоэмиттерных транзисторов накопителя и одним концом соответствующих нагрузочных элементов, выполненных на резисторах, другие концы которых подключены к шине нулевого потенциала и к коллекторам многоэмиттерных транзисторов накопителя, инвертор разре5 88605 щения выборки, каждый выход которого ! соединен с соответствующим .эмиттером многоэмиттерных транзисторов дешифратора, и источник питания, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства,. оно содержит. блоки сопряжения, выполненные на резисторах, при этом одни концы резисторов подключены к выходу источника питания, а другие IO концы резисторов первого блока соПряжения подключены к соответствую- щим эмиттерам многоэмиттерных транзисторов дешифратора, другие концы резисторов второго блока сопряжения у подключены к соответствующему эмиттеру каждого многоэмиттерного транзистора дешифратора, а другие концы резисторов третьего блока сопряжения подключены к соответствующим эмиттерам многоэмиттерных транзисторов на" копителя.

Источники информации, принятые во внимание при экспертизе

1. Патент C11IA Р 3909805, кл.340173 SP опублик 1975

2. Щетинин 1О, И., :(рамаренко О. Л., Неклюдов В. А. Монолитное ПЗУ 155PEl емкостью 256 бит со схемами управле11 ния. Сб. Микроэлектроника и полупроводниковые приборы". "Cов ° радио", 1976, вып. 1, с. 50-58. (прототип ).